Professional Documents

Culture Documents

8CMOS Fabrication Process Overview

8CMOS Fabrication Process Overview

Uploaded by

Chandrajit PalCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

8CMOS Fabrication Process Overview

8CMOS Fabrication Process Overview

Uploaded by

Chandrajit PalCopyright:

Available Formats

8-1

Complementary MOS fabrication

CMOS Technology depends on using both N-Type and P-Type devices on the same chip. The two main technologies to do this task are: P-Well (Will discuss the process steps involved with this technology)

The substrate is N-Type. The N-Channel device is built into a P-Type well within the parent N-Type substrate. The P-channel device is built directly on the substrate.

N-Well

The substrate is P-Type. The N-channel device is built directly on the substrate, while the Pchannel device is built into a N-type well within the parent P-Type substrate.

Two more advanced technologies to do this task are:

Becoming more popular for sub-micron geometries where device performance and density must be pushed beyond the limits of the conventional p & n-well CMOS processes.

Twin Tub

Both an N-Well and a P-Well are manufactured on a lightly doped N-type substrate.

Silicon-on-Insulator (SOI) CMOS Process

SOI allows the creation of independent, completely isolated nMOS and pMOS transistors virtually side-by-side on an insulating substrate.

CMOS fabrication process overview

8-2

P-well on N-substrate

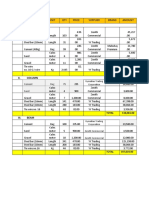

Steps : N-type substrate Oxidation, and mask (MASK 1) to create P-well (4-5m deep) P-well doping

P-well acts as substrate for nMOS devices. The two areas are electrically isolated using thick field oxide (and often isolation implants [not shown here])

SiO2

P-well N-type substrate

CMOS fabrication process overview

8-3

Polysilicon Gate Formation

Steps : Remove p-well definition oxide Grow thick field oxide Pattern (MASK 2) to expose nMOS and pMOS active regions Grow thin layer of SiO2 (~0.1m) gate oxide, over the entire chip surface Deposit polysilicon on top of gate oxide to form gate structure Pattern poly on gate oxide (MASK 3)

Thin gate oxide (SiO2)

Gate (patterned polysilicon on thin oxide)

Thick field oxide pMOS active region N-type substrate

nMOS active region

CMOS fabrication process overview

nMOS P+ Source/Drain difusion self-aligned to Poly gate

Implant P+ nMOS S/D regions (MASK 4)

8-4

P+ implant/diffusion

P+ mask

Thick field oxide N-type substrate

CMOS fabrication process overview

pMOS N+ Source/Drain difusion self-aligned to Poly gate

Implant N+ pMOS S/D regions (MASK 5 often the inverse of MASK 4)

8-5

N+ implant/diffusion N+ mask

P+ N-type substrate

N+

CMOS fabrication process overview

8-6

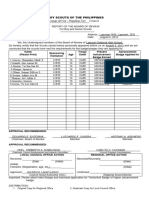

pMOS N+ Source/Drain difusion, contact holes & metallisation

Oxide and pattern for contact holes (MASK 6) Deposit metal and pattern (MASK 7) Passivation oxide and pattern bonding pads (MASK 8) P-well acts as substrate for nMOS devices. Two separate substrates : requires two separate substrate connections Definition of substrate connection areas can be included in MASK 4/MASK5

Vin N+ for N-substrate contact) Vdd Vout Vss P+ (for P-substrate contact)

P P+

P channel Device

N+

N channel Device

N-type substrate

CMOS fabrication process overview

8-7

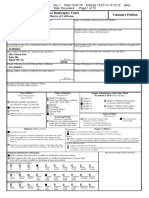

CMOS N-well process

An N-well process is also widely used

Vin P+ for P-substrate Vss contact) Vout Vdd N+ (for Nsubstrate contact)

N+

N channel Device

P+

N-well

P channel Device

P-type substrate

CMOS fabrication process overview

8-8

Composite layout and cross-section view of n-well CMOS device

(excludes passivation and patterning of wire-bonding pads)

CMOS fabrication process overview

Twin-Tub (Twin-Well) CMOS Process

8-9

This technology provides the basis for separate optimization of the nMOS and pMOS transistors, thus making it possible for threshold voltage, body effect and the channel transconductance of both types of transistors to be tuned independently. Generally, the starting material is a n+ or p+ substrate, with a lightly doped epitaxial layer on top. This epitaxial layer provides the actual substrate on which the n-well and the p-well are formed. Since two independent doping steps are performed for the creation of the well regions, the dopant concentrations can be carefully optimized to produce the desired device characteristics. The Twin-Tub process is shown below.

In the conventional p & n-well CMOS process, the doping density of the well region is typically about one order of magnitude higher than the substrate, which, among other effects, results in unbalanced drain parasitics. The twin-tub process avoids this problem.

CMOS fabrication process overview

8-10

Silicon-on-Insulator (SOI) CMOS Process

Rather than using silicon as the substrate material, technologists have sought to use an insulating substrate to improve process characteristics such as speed and latch-up susceptibility. The SOI CMOS technology allows the creation of independent, completely isolated nMOS and pMOS transistors virtually side-by-side on an insulating substrate. The main advantages of this technology are the higher integration density (because of the absence of well regions), complete avoidance of the latch-up problem, and lower parasitic capacitances compared to the conventional p & n-well or twin-tub CMOS processes. A crosssection of nMOS and pMOS devices using SOI process is shown below.

The SOI CMOS process is considerably more costly than the standard p & n-well CMOS process. Yet the improvements of device performance and the absence of latch-up problems can justify its use, especially for deep-sub-micron devices.

CMOS fabrication process overview

You might also like

- Deed of Donation - FormatDocument2 pagesDeed of Donation - FormatGodofredo Sabado89% (61)

- Pretty WomanDocument105 pagesPretty WomanMarkk Way May PattNo ratings yet

- VLSI Micro-Project Report Group A PDFDocument14 pagesVLSI Micro-Project Report Group A PDFganesh SawantNo ratings yet

- DM-PH&SD-P7-TG01 - (Guidelines For Swimming Pool Safety)Document7 pagesDM-PH&SD-P7-TG01 - (Guidelines For Swimming Pool Safety)Niel Brian VillarazoNo ratings yet

- C MOS: Omplementary FabricationDocument8 pagesC MOS: Omplementary FabricationVarun KumarNo ratings yet

- Fabrication ProcessDocument32 pagesFabrication ProcessRaja VidyaNo ratings yet

- Mos TechDocument23 pagesMos TechPavamana GiribhattanavarNo ratings yet

- 5 CMOS P-Well & N-Well ProcessDocument15 pages5 CMOS P-Well & N-Well ProcessRajesh PylaNo ratings yet

- Twin Tub CmosDocument14 pagesTwin Tub CmosZainora Kamal LudinNo ratings yet

- N Well CMOS FabricationDocument21 pagesN Well CMOS Fabricationshitijkarsolia96No ratings yet

- CMOS Process: Material Mainly Taken From UMBC, Kang and CampbellDocument38 pagesCMOS Process: Material Mainly Taken From UMBC, Kang and CampbellSmitha KollerahithluNo ratings yet

- Vlsi Design UNIT-1: Lecture-3Document11 pagesVlsi Design UNIT-1: Lecture-3Erica WhiteheadNo ratings yet

- VLSI - P Well ProcessDocument15 pagesVLSI - P Well ProcessK.R.Raguram100% (2)

- CMOS Process FlowDocument39 pagesCMOS Process FlowYashaswa JainNo ratings yet

- Lecture CMOS NWELL and TwinTub ProcessDocument33 pagesLecture CMOS NWELL and TwinTub Processilias ahmedNo ratings yet

- Lecture1 3 CMOS nWELL and TwinTub ProcessDocument33 pagesLecture1 3 CMOS nWELL and TwinTub ProcessSrikanth Soma100% (8)

- Cmos Fabrication TechnologyDocument36 pagesCmos Fabrication TechnologyKhadarNo ratings yet

- Nmos FabricationDocument45 pagesNmos FabricationDr-GopalNo ratings yet

- Complementary MetalDocument5 pagesComplementary MetalesaidanNo ratings yet

- CMOS/Processing TechnologyDocument15 pagesCMOS/Processing TechnologyYidnekachwe MekuriaNo ratings yet

- Unit 1: IC Fabrication: CMOS ProcessDocument42 pagesUnit 1: IC Fabrication: CMOS Processbadrinarayan2210298No ratings yet

- Integrated Analog/Digital Bicmos ProcessDocument8 pagesIntegrated Analog/Digital Bicmos ProcessJyothi PoornaNo ratings yet

- Twin TubDocument37 pagesTwin TubMalavika R NairNo ratings yet

- Transistors: Current (BJT) Voltage (FET)Document7 pagesTransistors: Current (BJT) Voltage (FET)Qin LingNo ratings yet

- Dic Lec 02 Fabrication v01Document68 pagesDic Lec 02 Fabrication v01fatmaadelmoNo ratings yet

- An Introduction To Integrated An Introduction To Integrated Circuits and CMOS TechnologyDocument34 pagesAn Introduction To Integrated An Introduction To Integrated Circuits and CMOS Technologymm16467No ratings yet

- 2017 ch3-1-CMOS TechnologysdDocument64 pages2017 ch3-1-CMOS TechnologysdNhân LêNo ratings yet

- Chip FabricationDocument34 pagesChip Fabricationrajatbarik_kiitNo ratings yet

- Layout Lec 01 Fab v01Document53 pagesLayout Lec 01 Fab v01Ahmed MetwalyNo ratings yet

- Seminar Report-Bicmos TechnologyDocument19 pagesSeminar Report-Bicmos Technologymbiswasray_iter0% (1)

- Vlsi NotesDocument11 pagesVlsi NotesShowcase MarathiNo ratings yet

- Cmos FabricationDocument42 pagesCmos FabricationAnonymous eWMnRr70qNo ratings yet

- FabricationDocument39 pagesFabricationfayazNo ratings yet

- Lecture 030 - Deep Submicron (DSM) Cmos TechnologyDocument14 pagesLecture 030 - Deep Submicron (DSM) Cmos TechnologywatelzbuddyNo ratings yet

- 2CMOSFabricationMNIT (DEc2006)Document46 pages2CMOSFabricationMNIT (DEc2006)Arjun YadavNo ratings yet

- Understanding About CMOS Fabrication TechnologyDocument4 pagesUnderstanding About CMOS Fabrication TechnologyJayesh RaghuwanshiNo ratings yet

- Pmos Nmos CmosDocument58 pagesPmos Nmos Cmosrahulmishra84No ratings yet

- 2016 ch3-CMOS Technology PDFDocument31 pages2016 ch3-CMOS Technology PDFTrần Anh TânNo ratings yet

- Cmos Process TechnologyDocument23 pagesCmos Process TechnologyDikshaNo ratings yet

- Introduction To Cmos Circuits: Unit IiDocument48 pagesIntroduction To Cmos Circuits: Unit Iiarun14089No ratings yet

- CMOS FabricationDocument27 pagesCMOS FabricationspvenuNo ratings yet

- Analog Digital VLSI Design: Discipline/eee/agupta/advd/advd - HTMDocument78 pagesAnalog Digital VLSI Design: Discipline/eee/agupta/advd/advd - HTMhkajaiNo ratings yet

- Cmos Fabrication: N - Well ProcessDocument42 pagesCmos Fabrication: N - Well ProcessArun GopinathNo ratings yet

- 3.4.3.7 Non-Volatile Memory: P+ Diode N+ Well Contact Collector Base EmitterDocument1 page3.4.3.7 Non-Volatile Memory: P+ Diode N+ Well Contact Collector Base EmitterCarlos SaavedraNo ratings yet

- Seminar Report Bicmos Technology PDFDocument6 pagesSeminar Report Bicmos Technology PDFjayarajcuietNo ratings yet

- Cmos Layout Design RulesDocument18 pagesCmos Layout Design RulesbharathababuNo ratings yet

- Dasar Design CMOS TransistorDocument49 pagesDasar Design CMOS Transistormaqbulloh darojatiNo ratings yet

- Cmos Metal GateDocument56 pagesCmos Metal GateSubin AlexNo ratings yet

- Fabrication of CMOS Integrated Circuits: Dae Hyun Kim Eecs Washington State UniversityDocument34 pagesFabrication of CMOS Integrated Circuits: Dae Hyun Kim Eecs Washington State Universityfouzia_qNo ratings yet

- VLSI Unit 2 Technology - SDocument52 pagesVLSI Unit 2 Technology - SIndrajeet GautamNo ratings yet

- C Cmos Basics - Ani PDFDocument17 pagesC Cmos Basics - Ani PDFAnindra NallapatiNo ratings yet

- Microsoft Powerpoint - Vlsi Design AspectDocument89 pagesMicrosoft Powerpoint - Vlsi Design AspectAKASHDIP DUTTANo ratings yet

- UNIT-1: TOPIC: MOS Process, NMOS Process, CMOS ProcessDocument36 pagesUNIT-1: TOPIC: MOS Process, NMOS Process, CMOS ProcessashishNo ratings yet

- Vlsi PDFDocument81 pagesVlsi PDFShruthiNo ratings yet

- 1.5 CMOS Fabrication and Layout: N+ N+ N+ P+ P+ P+Document1 page1.5 CMOS Fabrication and Layout: N+ N+ N+ P+ P+ P+Carlos SaavedraNo ratings yet

- Operation and FabricationDocument27 pagesOperation and Fabricationsaiteja kothapalliNo ratings yet

- Lecture 0 - CMOS VLSI DesignDocument41 pagesLecture 0 - CMOS VLSI Designkrishy19sNo ratings yet

- Unit 5 - VLSI Design - WWW - Rgpvnotes.inDocument12 pagesUnit 5 - VLSI Design - WWW - Rgpvnotes.intanishachaturvedi2025No ratings yet

- Ee 401 - Vlsi Design: WEEK-04Document27 pagesEe 401 - Vlsi Design: WEEK-04Khurram shahzadNo ratings yet

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- PROPULSION E-Motors 300609-014459 PDFDocument59 pagesPROPULSION E-Motors 300609-014459 PDFScott_B4U100% (1)

- Data Akun PDDocument19 pagesData Akun PDArinda Putri OfficialNo ratings yet

- Kitab Al Bidayah Wan Nihayah PDF FilesDocument4 pagesKitab Al Bidayah Wan Nihayah PDF Filesrahmat hidayatNo ratings yet

- Carnegie Vanguard High School/Houston ISD Renovation BudgetDocument5 pagesCarnegie Vanguard High School/Houston ISD Renovation BudgetTexas WatchdogNo ratings yet

- 01 V5 X Series Engineering Data BookDocument212 pages01 V5 X Series Engineering Data Bookcalvin.bloodaxe4478No ratings yet

- Gasket Design CriteriaDocument63 pagesGasket Design CriteriakingdbmNo ratings yet

- John Dy Vs PeopleDocument22 pagesJohn Dy Vs Peoplechristopher1julian1aNo ratings yet

- Ash Utilisation - An Australian Perspective: MR Craig HeidrichDocument13 pagesAsh Utilisation - An Australian Perspective: MR Craig HeidrichRizqikha Hanung CiptayukasNo ratings yet

- Jeremy Johnston Capstone Project-CompressedDocument62 pagesJeremy Johnston Capstone Project-Compressedapi-575618099No ratings yet

- Robots TeleoperadosDocument7 pagesRobots TeleoperadosDanilo Carvajal MarinNo ratings yet

- 54.2017新版ISO IEC17025對實驗室管理系統之應用Document192 pages54.2017新版ISO IEC17025對實驗室管理系統之應用Chi Jui HanNo ratings yet

- F-1705 Internal Audit Check ListDocument73 pagesF-1705 Internal Audit Check ListAjay100% (1)

- Collection: ZARA: The International Success of Fast Moving FashionDocument14 pagesCollection: ZARA: The International Success of Fast Moving FashionAhmed ZaidiNo ratings yet

- In Re Atty Rufillo BucanaDocument1 pageIn Re Atty Rufillo BucanaKym HernandezNo ratings yet

- Using Algebra To Solve ProblemsDocument18 pagesUsing Algebra To Solve ProblemsJason Lam LamNo ratings yet

- A$ap Ferg Feat. Nicki Minaj - Plain Jane Remix LyricsDocument1 pageA$ap Ferg Feat. Nicki Minaj - Plain Jane Remix LyricsKAREENA AMEENAH ACRAMAN BASMANNo ratings yet

- Lotte Titanpro PM903 Product DataDocument1 pageLotte Titanpro PM903 Product DataJoni Sie MssNo ratings yet

- Epicondilitis Lateral. La Condición y Las Estrategias de Manejo ActualesDocument5 pagesEpicondilitis Lateral. La Condición y Las Estrategias de Manejo Actualescontact.movementsiteNo ratings yet

- Oracle Learning - New Features in Release 24A: Bookmark Learning Items Questions AnswersDocument6 pagesOracle Learning - New Features in Release 24A: Bookmark Learning Items Questions AnswersSiva KumarNo ratings yet

- Chapter 10 - IMC - Media Planning & StrategyDocument26 pagesChapter 10 - IMC - Media Planning & Strategysumanth1437100% (1)

- 2006 CSTE CBOK Skill Category 2Document54 pages2006 CSTE CBOK Skill Category 2api-3733726No ratings yet

- Amazon Kindle Publishing GuidelinesDocument63 pagesAmazon Kindle Publishing Guidelinesa_rogall7926No ratings yet

- ITEMDocument7 pagesITEMGintokiNo ratings yet

- Link Beam Schedule-ModelDocument19 pagesLink Beam Schedule-ModelJohnson SambranoNo ratings yet

- BSP fORM 194-DEMODocument24 pagesBSP fORM 194-DEMORonald GomezNo ratings yet

- Manual Robots CP en 01 2021Document42 pagesManual Robots CP en 01 2021asrulnizam matnor100% (1)

- Electracash's BankruptcyDocument70 pagesElectracash's BankruptcyhyenadogNo ratings yet