Professional Documents

Culture Documents

VTU - Practical Book - Part A - 04-08-2009

Uploaded by

Kishore KumarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VTU - Practical Book - Part A - 04-08-2009

Uploaded by

Kishore KumarCopyright:

Available Formats

Implementation Design Ideas

for

CMOS VLSI Practicals

as per Syllabus of

VTU, Karnataka

Part - A

ASIC Digital Design

This page is intentionally left blank

VTU 2009 Part A

ASIC Digital Design

Table of Contents

Introduction to Xilinx ISE Software for Digital Logic Design ....................................... 4

Experiment 1: Logic Inverter .................................................................................... 11

Experiment 2: Transmission Gate ............................................................................ 14

Experiment 3: Digital Gates...................................................................................... 18

Experiment 4: Flip Flops........................................................................................... 22

Experiment 5: Adders............................................................................................... 27

Part A: Serial Adder ........................................................................................... 27

Part B: Parallel Adder ........................................................................................ 31

Experiment 6: Counters............................................................................................ 35

Part A: Synchronous Counter ............................................................................ 35

Note: To be performed by studentPart B: Asynchronous Counter ..................... 35

Part B: Asynchronous Counter .......................................................................... 36

Note: To be performed by studentExperiment 7: Successive Approximation

Register(SAR) .......................................................................................................... 36

Experiment 7: Successive Approximation Register(SAR) ........................................ 37

Reference Software:

Xilinx ISE webpack 10.1

VTU 2009 Part A

ASIC Digital Design

Introduction to Xilinx ISE Software for Digital Logic Design

Creating New Project

Step (1): Open software and click on NEW PROJECT from file menu

Step (2): Write project name and specify location for project.

VTU 2009 Part A

ASIC Digital Design

Step (3): Specify target device technology and select your desired device.

Step (4): Create NEW SOURCE file.

(Example shown is of D type Flip-Flop)

VTU 2009 Part A

ASIC Digital Design

Step (5): Specify the input & outputs in design

(Example shown is of D type Flip-Flop)

Step (6): Describe the code for the design

(Example shown is of D type Flip-Flop)

VTU 2009 Part A

ASIC Digital Design

Step (7): For TESTBENCH. Create NEW SOURCE FILE

Step (8): Select the source file for TESTBENCH

VTU 2009 Part A

ASIC Digital Design

Step (9): Set the timing parameter in test bench. Set values carefully.

Step (10): Click on input pins to generate desired input test pattern.

VTU 2009 Part A

ASIC Digital Design

Step (11): Goto SOURCE TAB in software, and select simulation mode.

Step (12): Not select the test bench file and run the simulation process

VTU 2009 Part A

ASIC Digital Design

Step (13): Verify the results

Zoom in results

Step (14): Run VIEW RTL NETLIST command to check RTL schematic results

VTU 2009 Part A

10

ASIC Digital Design

Experiment 1: Logic Inverter

Aim: To write a Verilog code for Inverter and Synthesize using Spartan-3 XC3S50 OR

XC3S400 device.

Logic symbol:

Verilog Code:

// Inverter Design

module Inverter(

input a,

output y

);

assign y = ~a;

endmodule

VTU 2009 Part A

11

ASIC Digital Design

RTL Schematic Generated after Synthesis:

Synthesis Results:

======================================================================

*

Final Report

*

======================================================================

Final Results

RTL Top Level Output File Name : Inverter.ngr

Top Level Output File Name

: Inverter

Output Format

: NGC

Optimization Goal

: Speed

Keep Hierarchy

: NO

Design Statistics

# IOs

:2

Cell Usage :

# BELS

:1

#

INV

:1

# IO Buffers

:2

#

IBUF

:1

#

OBUF

:1

======================================================================

VTU 2009 Part A

12

ASIC Digital Design

Timing Report:

Pad to Pad

---------------+---------------+---------+

Source Pad

|Destination Pad| Delay |

---------------+---------------+---------+

a

|y

|

6.289|

---------------+---------------+---------+

Simulation Result:

Post-layout or gate-level verification of design (Full view)

VTU 2009 Part A

13

ASIC Digital Design

Experiment 2: Transmission Gate

Aim: To write a Verilog code for Transmission gate and Synthesize using Spartan-3

XC3S50 OR XC3S400 device.

Specifications:

Design with Output enable, direction control and of 8bit size.

Logic symbol:

Verilog Code:

module t_gate(a,b,enable,dir);

input enable,dir;

inout [7:0] a,b;

wire [7:0] a , b;

//-------------Code Starts Here------// b --> a

assign a = (enable == 1'b0 && dir == 1'b1) ? b : 8'hzz;

// a --> b

assign b = (enable == 1'b0 && dir == 1'b0) ? a : 8'hzz;

endmodule

VTU 2009 Part A

14

ASIC Digital Design

RTL Schematic Generated after Synthesis:

Synthesis Results:

======================================================================

*

Final Report

*

======================================================================

Final Results

RTL Top Level Output File Name : t_gate.ngr

Top Level Output File Name

: t_gate

Output Format

: NGC

Optimization Goal

: Speed

Keep Hierarchy

: NO

Design Statistics

# IOs

: 18

Cell Usage :

# BELS

:2

#

LUT2

:2

# IO Buffers

: 18

#

IBUF

:2

#

IOBUF

: 16

======================================================================

Device utilization summary:

Selected Device : 3s50tq144-4

Number of Slices:

Number of 4 input LUTs:

Number of IOs:

Number of bonded IOBs:

1 out of 768 0%

2 out of 1536 0%

18

18 out of 97 18%

VTU 2009 Part A

15

ASIC Digital Design

Timing Report:

Pad to Pad

---------------+---------------+---------+

Source Pad

|Destination Pad| Delay |

---------------+---------------+---------+

a<0>

|b<0>

|

6.060|

a<1>

|b<1>

|

6.060|

a<2>

|b<2>

|

6.060|

a<3>

|b<3>

|

6.060|

a<4>

|b<4>

|

6.060|

a<5>

|b<5>

|

6.060|

a<6>

|b<6>

|

6.060|

a<7>

|b<7>

|

6.060|

b<0>

|a<0>

|

6.060|

b<1>

|a<1>

|

6.060|

b<2>

|a<2>

|

6.060|

b<3>

|a<3>

|

6.060|

b<4>

|a<4>

|

6.060|

b<5>

|a<5>

|

6.060|

b<6>

|a<6>

|

6.060|

b<7>

|a<7>

|

6.060|

dir

|a<0>

|

6.954|

dir

|a<1>

|

6.954|

dir

|a<2>

|

6.954|

dir

|a<3>

|

6.954|

dir

|a<4>

|

6.954|

dir

|a<5>

|

6.954|

dir

|a<6>

|

6.954|

dir

|a<7>

|

6.954|

dir

|b<0>

|

6.954|

dir

|b<1>

|

6.954|

dir

|b<2>

|

6.954|

dir

|b<3>

|

6.954|

dir

|b<4>

|

6.954|

dir

|b<5>

|

6.954|

dir

|b<6>

|

6.954|

dir

|b<7>

|

6.954|

enable

|a<0>

|

6.954|

enable

|a<1>

|

6.954|

enable

|a<2>

|

6.954|

enable

|a<3>

|

6.954|

enable

|a<4>

|

6.954|

enable

|a<5>

|

6.954|

enable

|a<6>

|

6.954|

enable

|a<7>

|

6.954|

enable

|b<0>

|

6.954|

enable

|b<1>

|

6.954|

enable

|b<2>

|

6.954|

enable

|b<3>

|

6.954|

enable

|b<4>

|

6.954|

enable

|b<5>

|

6.954|

enable

|b<6>

|

6.954|

enable

|b<7>

|

6.954|

---------------+---------------+---------+

VTU 2009 Part A

16

ASIC Digital Design

Simulation Result:

Post-layout or gate-level verification of design (Full view)

Post-layout or gate-level verification of design (Full view)

Power Consumption Report:

Power summary

|

I(mA)

|

P(mW)

|

---------------------------------------------------------------Total estimated power consumption

|

|

24 |

--Total Vccint

1.20V |

5 |

6 |

Total Vccaux

2.50V |

7 |

18 |

Total Vcco25

2.50V |

0 |

0 |

--IOs

|

0 |

0 |

Inputs

|

0 |

0 |

Logic

|

0 |

0 |

Signals

|

0 |

0 |

--Quiescent Vccint

1.20V |

5 |

6 |

Quiescent Vccaux

2.50V |

7 |

18 |

VTU 2009 Part A

17

ASIC Digital Design

Experiment 3: Digital Gates

Aim: To write a Verilog code for basic & universal gates and Synthesize using Spartan-3

XC3S50 OR XC3S400 device.

Specifications:

Design a 2-bit XOR, NAND, and AND gate.

Logic symbol:

Verilog Code:

module gates(

input a,

input b,

output gate_NAND,

output gate_XOR,

output gate_AND

);

assign gate_XOR = a ^ b;

assign gate_AND = a & b;

assign gate_NAND = ~(a & b);

endmodule

VTU 2009 Part A

18

ASIC Digital Design

RTL Schematic Generated after Synthesis:

Synthesis Results:

======================================================================

*

Final Report

*

======================================================================

Final Results

RTL Top Level Output File Name : gates.ngr

Top Level Output File Name

: gates

Output Format

: NGC

Optimization Goal

: Speed

Keep Hierarchy

: NO

Design Statistics

# IOs

: 5

Cell Usage :

# BELS

: 3

#

LUT2

: 3

# IO Buffers

: 5

#

IBUF

: 2

#

OBUF

: 3

======================================================================

Device utilization summary:

Selected Device : 3s50tq144-4

Number of Slices:

Number of 4 input LUTs:

Number of IOs:

Number of bonded IOBs:

VTU 2009 Part A

3

5

5

out of

out of

768

1536

0%

0%

out of

97

5%

19

ASIC Digital Design

Timing Report:

Pad to Pad

---------------+---------------+---------+

Source Pad

|Destination Pad| Delay |

---------------+---------------+---------+

a

|gate_AND

|

7.720|

a

|gate_NAND

|

8.037|

a

|gate_XOR

|

7.520|

b

|gate_AND

|

7.528|

b

|gate_NAND

|

8.206|

b

|gate_XOR

|

7.249|

---------------+---------------+---------+

To see timing results open *.TWR file from your project folder.

For Eb. gates.twr or FF_All.twr

VTU 2009 Part A

20

ASIC Digital Design

Simulation Result:

Post-layout or gate-level verification of design (Full view)

Post-layout or gate-level verification of design (Full view)

Power Consumption Report:

Power summary

|

I(mA)

|

P(mW)

|

---------------------------------------------------------------Total estimated power consumption

|

|

24 |

--Total Vccint

1.20V |

5 |

6 |

Total Vccaux

2.50V |

7 |

18 |

Total Vcco25

2.50V |

0 |

0 |

--Inputs

|

0 |

0 |

Logic

|

0 |

0 |

Outputs

|

Vcco25 |

0 |

0 |

Signals

|

0 |

0 |

--Quiescent Vccint

1.20V |

5 |

6 |

Quiescent Vccaux

2.50V |

7 |

18 |

VTU 2009 Part A

21

ASIC Digital Design

Experiment 4: Flip Flops

Aim: To write a Verilog code for RS, D, JK, MS & T flip flops and Synthesize using Spartan3 XC3S50 OR XC3S400 device.

Specifications:

Write code for RS, D, JK, MS & T flip flops.

Logic symbol:

Verilog Code:

module FF_All(

input clk,

// Inputs for Flip-Flops

input J,K,

input R,S,

input D,

input set, reset,

input T_En,

// Outputs for Flip-Flops

output Q_JK, Q_JK_bar, // JK

output Q_RS,Q_RS_bar,

output Q_D,Q_D_bar,

output Q_MS,Q_MS_bar,

output Q_T,Q_T_bar

);

// RS

// D

// MS

// T

// Internal Variables

reg q_jk_temp;

reg q_rs_temp,q_rs_bar_temp;

reg q_d_temp;

reg q_t_temp;

reg q_ms_temp;

// JK Flip-Flop description

always@(posedge clk)

begin

if (J==1'b0 && K==1'b1)

q_jk_temp = 1'b0;

else if(J==1'b1 && K==1'b0)

q_jk_temp = 1'b1;

else if(J==1'b1 && K==1'b1)

q_jk_temp = ~q_jk_temp;

end

// JK Outputs assignments

assign Q_JK = q_jk_temp;

assign Q_JK_bar = ~q_jk_temp;

VTU 2009 Part A

22

ASIC Digital Design

// RS Flip-Flop description

always@(R,S)

begin

q_rs_temp = ~(S && q_rs_bar_temp);

q_rs_bar_temp = ~(S && q_rs_temp);

end

assign Q_RS

= q_rs_temp;

assign Q_RS_bar

= q_rs_bar_temp;

// D Flip-Flop description

always@(posedge clk or posedge reset or posedge set)

begin

if (reset)

// Asynchronous reset & set logic

q_d_temp = 1'b0;

else if(set)

q_d_temp = 1'b1;

else

q_d_temp = D;

end

// D-FF Outputs assignments

assign Q_D = q_d_temp;

assign Q_D_bar = ~q_d_temp;

// D Flip-Flop description

always@(negedge clk or posedge reset or posedge set)

begin

if (reset)

// Asynchronous reset & set logic

q_ms_temp = 1'b0;

else if(set)

q_ms_temp = 1'b1;

else

q_ms_temp = q_d_temp;

// stores O/P coming from D flip-flop

end

// MS-FF Outputs assignments

assign Q_MS = q_ms_temp;

assign Q_MS_bar = ~q_ms_temp;

// T Flip-Flop description

always@(posedge clk)

begin

if (T_En)

q_t_temp = ~q_t_temp;

end

// T-FF Outputs assignments

assign Q_T = q_t_temp;

assign Q_T_bar = ~q_t_temp;

endmodule

VTU 2009 Part A

23

ASIC Digital Design

RTL Schematic Generated after Synthesis:

Synthesis Results:

======================================================================

*

Final Report

*

======================================================================

Final Results

Design Statistics

# IOs

: 19

Cell Usage :

# BELS

: 10

#

INV

:5

#

LUT2

:5

# FlipFlops/Latches

:5

#

FDCP

:2

#

FDCP_1

:1

#

FDE

:1

#

FDRSE

:1

# Clock Buffers

:1

#

BUFGP

:1

# IO Buffers

: 17

#

IBUF

:7

#

OBUF

: 10

======================================================================

Device utilization summary:

Selected Device : 3s50tq144-4

Number of Slices:

Number of Slice Flip Flops:

Number of 4 input LUTs:

Number of IOs:

Number of bonded IOBs:

IOB Flip Flops:

Number of GCLKs:

VTU 2009 Part A

4

10

19

18

1

1

out of

out of

out of

768

1536

1536

0%

0%

0%

out of

97

18%

out of

12%

24

ASIC Digital Design

Timing Report:

All values displayed in nanoseconds (ns)

Setup/Hold to clock clk

------------+------------+------------+------------------+--------+

| Setup to | Hold to

|

| Clock |

Source

| clk (edge) | clk (edge) |Internal Clock(s) | Phase |

------------+------------+------------+------------------+--------+

D

|

3.426(R)|

0.779(R)|clk_BUFGP

|

0.000|

J

|

2.893(R)|

-0.324(R)|clk_BUFGP

|

0.000|

K

|

2.724(R)|

-0.174(R)|clk_BUFGP

|

0.000|

T_En

|

1.216(R)|

0.161(R)|clk_BUFGP

|

0.000|

------------+------------+------------+------------------+--------+

Clock clk to Pad

------------+------------+------------------+--------+

| clk (edge) |

| Clock |

Destination |

to PAD

|Internal Clock(s) | Phase |

------------+------------+------------------+--------+

Q_D

|

7.678(R)|clk_BUFGP

|

0.000|

Q_D_bar

|

8.166(R)|clk_BUFGP

|

0.000|

Q_JK

|

8.128(R)|clk_BUFGP

|

0.000|

Q_JK_bar

|

8.518(R)|clk_BUFGP

|

0.000|

Q_MS

|

8.831(F)|clk_BUFGP

|

0.000|

Q_MS_bar

|

9.155(F)|clk_BUFGP

|

0.000|

Q_T

|

9.525(R)|clk_BUFGP

|

0.000|

Q_T_bar

|

8.857(R)|clk_BUFGP

|

0.000|

------------+------------+------------------+--------+

Clock to Setup on destination clock clk

---------------+---------+---------+---------+---------+

| Src:Rise| Src:Fall| Src:Rise| Src:Fall|

Source Clock

|Dest:Rise|Dest:Rise|Dest:Fall|Dest:Fall|

---------------+---------+---------+---------+---------+

clk

|

1.713|

|

1.617|

|

---------------+---------+---------+---------+---------+

Pad to Pad

---------------+---------------+---------+

Source Pad

|Destination Pad| Delay |

---------------+---------------+---------+

S

|Q_RS

|

7.945|

S

|Q_RS_bar

|

7.360|

---------------+---------------+---------+

To see timing results open *.TWR file from your project folder.

For Eb. gates.twr or FF_All.twr

VTU 2009 Part A

25

ASIC Digital Design

Simulation Result:

Post-layout or gate-level verification of design (Full view)

Post-layout or gate-level verification of design (Full view)

Power Consumption Report:

Power summary

|

I(mA)

|

P(mW)

|

---------------------------------------------------------------Total estimated power consumption

|

Number of error messages: 0

Number of warning messages: 3

Number of info messages: 1

1.20V

Total Vccaux

Total Vcco25

2.50V

2.50V

--Clocks

Inputs

Logic

Outputs

Vcco25

Signals

--Quiescent Vccint

1.20V

Quiescent Vccaux

2.50V

|

|

|

5

7

0

|

|

|

6

18

0

|

|

|

|

|

|

|

|

|

0

0

0

|

|

|

0

0

0

|

|

|

0

0

|

|

0

0

|

|

|

|

5

7

|

|

6

18

|

|

VTU 2009 Part A

26

ASIC Digital Design

Experiment 5: Adders

Part A: Serial Adder

Aim: To write a Verilog code for serial adder and Synthesize using Spartan-3 XC3S50 OR

XC3S400 device.

Specifications:

Design a 4-bit serial adder. Addition will start with a control signal Enable, the 2 numbers

would come serially to the adder. Output has to be given on a o/p register.

Logic symbol:

Verilog Code:

module adder_serial(

input clk,rst,

input en,

// on Enable, addition will start

input a,

// 4-bit adder

input b,

output [3:0] result

);

reg [3:0] y;

reg carry;

always@(posedge rst or posedge clk)

begin

if (rst)

begin

y = 4'b0;

carry = 1'b0;

end

else if (en)

begin

y[3] = y[2];

y[2] = y[1];

y[1] = y[0];

{carry,y[0]} = a + b + carry;

end

end

assign result = y;

endmodule

VTU 2009 Part A

27

ASIC Digital Design

RTL Schematic Generated after Synthesis:

Synthesis Results:

======================================================================

*

Final Report

*

======================================================================

Design Statistics

# IOs

:9

Cell Usage :

# BELS

:2

#

LUT3

:2

# FlipFlops/Latches

:5

#

FDCE

:5

# Clock Buffers

:1

#

BUFGP

:1

# IO Buffers

:8

#

IBUF

:4

#

OBUF

:4

======================================================================

Device utilization summary:

Selected Device : 3s50tq144-4

Number of Slices:

Number of Slice Flip Flops:

Number of 4 input LUTs:

Number of IOs:

Number of bonded IOBs:

Number of GCLKs:

VTU 2009 Part A

5

2

9

9

1

out of

out of

out of

768

1536

1536

0%

0%

0%

out of

out of

97

8

9%

12%

28

ASIC Digital Design

Timing Report:

Setup/Hold to clock clk

------------+------------+------------+------------------+--------+

| Setup to | Hold to

|

| Clock |

Source

| clk (edge) | clk (edge) |Internal Clock(s) | Phase |

------------+------------+------------+------------------+--------+

a

|

0.514(R)|

0.703(R)|clk_BUFGP

|

0.000|

b

|

0.610(R)|

0.625(R)|clk_BUFGP

|

0.000|

en

|

0.868(R)|

0.461(R)|clk_BUFGP

|

0.000|

------------+------------+------------+------------------+--------+

Clock clk to Pad

------------+------------+------------------+--------+

| clk (edge) |

| Clock |

Destination |

to PAD

|Internal Clock(s) | Phase |

------------+------------+------------------+--------+

result<0>

|

8.194(R)|clk_BUFGP

|

0.000|

result<1>

|

8.911(R)|clk_BUFGP

|

0.000|

result<2>

|

8.858(R)|clk_BUFGP

|

0.000|

result<3>

|

8.825(R)|clk_BUFGP

|

0.000|

------------+------------+------------------+--------+

Clock to Setup on destination clock clk

---------------+---------+---------+---------+---------+

| Src:Rise| Src:Fall| Src:Rise| Src:Fall|

Source Clock

|Dest:Rise|Dest:Rise|Dest:Fall|Dest:Fall|

---------------+---------+---------+---------+---------+

clk

|

1.912|

|

|

|

---------------+---------+---------+---------+---------+

To see timing results open *.TWR file from your project folder.

For Eb. gates.twr or FF_All.twr

VTU 2009 Part A

29

ASIC Digital Design

Simulation Result:

Post-layout or gate-level verification of design (Full view)

Post-layout or gate-level verification of design (Full view)

Power Consumption Report:

Power summary

|

I(mA)

|

P(mW)

|

---------------------------------------------------------------Total estimated pow

Number of error messages: 0

Number of warning messages: 3

Number of info messages: 1

Total Vccint

1.20V |

Total Vccaux

2.50V

Total Vcco25

2.50V

--Clocks

Inputs

Logic

Outputs

Vcco25

Signals

--Quiescent Vccint

1.20V

Quiescent Vccaux

2.50V

|

|

7

0

|

|

6 |

18 |

0 |

|

|

|

|

|

|

0

0

0

|

|

|

0

0

0

|

|

|

0

0

|

|

0

0

|

|

|

|

5

7

|

|

6

18

|

|

VTU 2009 Part A

30

ASIC Digital Design

Part B: Parallel Adder

Aim: To write a Verilog code for parallel adder and Synthesize using Spartan-3 XC3S50 OR

XC3S400 device.

Specifications:

Design a 4-bit serial adder with Carry input.

Logic symbol:

A

4

B

4

Result

Cin

Verilog Code:

module Adder_Parallel(

input [3:0] a,b,

input cin,

output [4:0] y

);

assign y = a + b + cin;

endmodule

VTU 2009 Part A

31

ASIC Digital Design

RTL Schematic Generated after Synthesis:

Synthesis Results:

======================================================================

*

Final Report

*

======================================================================

Design Statistics

# IOs

: 14

Cell Usage :

# BELS

: 12

#

LUT2

:4

#

MUXCY

:4

#

XORCY

:4

# IO Buffers

: 14

#

IBUF

:9

#

OBUF

:5

======================================================================

Device utilization summary:

Selected Device : 3s50tq144-4

Number of Slices:

Number of 4 input LUTs:

Number of IOs:

Number of bonded IOBs:

4

14

14

VTU 2009 Part A

out of

out of

768

1536

0%

0%

out of

97

14%

32

ASIC Digital Design

Timing Report:

Pad to Pad

---------------+---------------+---------+

Source Pad

|Destination Pad| Delay |

---------------+---------------+---------+

a<0>

|y<0>

|

8.906|

a<0>

|y<1>

|

9.638|

a<0>

|y<2>

|

9.500|

a<0>

|y<3>

|

9.503|

a<0>

|y<4>

|

8.449|

a<1>

|y<1>

|

9.301|

a<1>

|y<2>

|

9.607|

a<1>

|y<3>

|

9.610|

a<1>

|y<4>

|

8.556|

a<2>

|y<2>

|

8.642|

a<2>

|y<3>

|

9.265|

a<2>

|y<4>

|

8.436|

a<3>

|y<3>

|

9.158|

a<3>

|y<4>

|

8.773|

b<0>

|y<0>

|

8.386|

b<0>

|y<1>

|

9.118|

b<0>

|y<2>

|

8.980|

b<0>

|y<3>

|

8.983|

b<0>

|y<4>

|

7.929|

b<1>

|y<1>

|

8.705|

b<1>

|y<2>

|

9.011|

b<1>

|y<3>

|

9.014|

b<1>

|y<4>

|

7.960|

b<2>

|y<2>

|

8.028|

b<2>

|y<3>

|

8.651|

b<2>

|y<4>

|

7.822|

b<3>

|y<3>

|

8.430|

b<3>

|y<4>

|

8.045|

cin

|y<0>

|

9.874|

cin

|y<1>

|

9.986|

cin

|y<2>

|

9.848|

cin

|y<3>

|

9.851|

cin

|y<4>

|

8.797|

---------------+---------------+---------+

To see timing results open *.TWR file from your project folder.

For eg. gates.twr or Adder_Parallel.twr

VTU 2009 Part A

33

ASIC Digital Design

Simulation Result:

Post-layout or gate-level verification of design (Full view)

Post-layout or gate-level verification of design (Zoom in view)

Power Consumption Report:

Power summary

|

I(mA)

|

P(mW)

|

---------------------------------------------------------------Total estimated power consumption

|

|

24 |

--Total Vccint

1.20V |

5 |

6 |

Total Vccaux

2.50V |

7 |

18 |

Total Vcco25

2.50V |

0 |

0 |

--Inputs

|

0 |

0 |

Logic

|

0 |

0 |

Outputs

|

Vcco25 |

0 |

0 |

Signals

|

0 |

0 |

--Quiescent Vccint

1.20V |

5 |

6 |

Quiescent Vccaux

2.50V |

7 |

18 |

VTU 2009 Part A

34

ASIC Digital Design

Experiment 6: Counters

Part A: Synchronous Counter

Aim: To write a Verilog code for Synchronous Counter and Synthesize using Spartan-3

XC3S50 OR XC3S400 device.

Specifications:

Design a 4-bit synchronous counter with asynchronous reset and enable.

Verilog Code:

// 4-bit Synchronous counter

module Syn_cntr_4_bit (

out ,

en ,

clk ,

rst

// Output of the counter

// Enable for the counter

// clock input

// reset input

);

//----------Output Ports-------------output [3:0] out;

//------------Input Ports-------------input en, clk, rst;

reg [3:0] out;

always @(posedge clk or posedge rst)

begin

if (rst) begin // active high reset

out <= 4'b0 ;

end

else if (en)

out <= out + 1;

end

endmodule

Note: To be performed by student

VTU 2009 Part A

35

ASIC Digital Design

Part B: Asynchronous Counter

Aim: To write a Verilog code for Asynchronous Counter and Synthesize using Spartan-3

XC3S50 OR XC3S400 device.

Specifications:

Design a 4-bit asynchronous counter.

Verilog Code:

// Asynchronous 4-bit Counter

module Async_cntr_4bit(clk,q,rst);

input clk,rst;

output [3:0] q;

reg q0,q1,q2,q3;

// LSB bit

always@(posedge clk or posedge rst)

begin

if (rst)

q0 = 1'b0;

else

q0 = ~q0;

end

// O/P of LSB bit as clock to next F/F

always@(negedge q0 or posedge rst)

begin

if (rst)

q1 = 1'b0;

else

q1 = ~q1;

end

always@(negedge q1 or posedge rst)

begin

if (rst)

q2 = 1'b0;

else

q2 = ~q2;

end

always@(negedge q2 or posedge rst)

begin

if (rst)

q3 = 1'b0;

else

q3 = ~q3;

end

assign q = {q3,q2,q1,q0};

endmodule

Note: To be performed by student

VTU 2009 Part A

36

ASIC Digital Design

Experiment 7: Successive Approximation Register(SAR)

Aim: To write a Verilog code for SAR logic of ADC and Synthesize using Spartan-3 XC3S50

OR XC3S400 device.

Specifications:

Design a 4-bit SAR logic for 4-bit ADC, use start of conversion & end of conversion signals.

Algorithm for SAR counter:

Reset counter

i=N-1,ai=1

Update VDAC

Yes

No

Vin> VDAC

i=i-1; ai=1

ai=0

ai=1

Yes

No

i>=0?

End conversion

Verilog Code:

module SAR_Counter(

input clk,

input rst,

input comparator_in,

input SOC,

output EOC,

output [3:0] Q

);

reg[3:0] q_temp; // DAC o/p register

reg [2:0] q_cntr; // cycle counter

reg en,EOC_temp;

// Enable Control

always@(posedge clk or posedge rst)

begin

if (rst)

en = 1'b0;

else if (EOC_temp)

en = 1'b0;

else if (SOC)

en = 1'b1;

end

// End of conversion Control

always@(posedge clk or posedge rst)

begin

VTU 2009 Part A

37

ASIC Digital Design

if (rst)

EOC_temp = 1'b0;

else if (q_cntr==3'b111)

EOC_temp = 1'b1;

else

EOC_temp = 1'b0;

end

assign EOC = EOC_temp;

// Cycle Counter

always@(posedge clk or posedge rst)

begin

if (rst)

q_cntr = 3'b0;

else if (EOC_temp)

q_cntr = 3'b0;

else if (en)

q_cntr = q_cntr + 1;

end

assign Q = q_temp;

// SAR logic

always@(posedge clk or posedge rst)

begin

if (rst)

q_temp = 4'b1000;

else if (en)

begin

case (q_cntr)

3'b001 :

begin

if(comparator_in)

// Check MSB bit

q_temp[3] = q_temp[3];

else

q_temp[3] = 1'b0;

end

3'b010 : begin

q_temp[2] = 1'b1;

// Set 2nd MSB bit

end

3'b011 : begin

if(comparator_in)

// Check 2nd MSB bit

q_temp[2] = q_temp[2];

else

q_temp[2] = 1'b0;

end

3'b100 : begin

q_temp[1] = 1'b1;

// Set 3rd MSB bit

end

3'b101 : begin

if(comparator_in)

// Check 3rd MSB bit

q_temp[1] = q_temp[1];

else

q_temp[1] = 1'b0;

end

3'b110 : begin

q_temp[0] = 1'b1;

// Set LSB bit

end

VTU 2009 Part A

38

ASIC Digital Design

3'b111 : begin

if(comparator_in)

q_temp[0] = q_temp[0];

else

q_temp[0] = 1'b0;

end

default: begin

q_temp = q_temp;

end

endcase

end

else

q_temp = 4'b1000;

end

// Check LSB bit

endmodule

VTU 2009 Part A

39

ASIC Digital Design

RTL Schematic Generated after Synthesis:

Synthesis Results:

======================================================================

*

Final Report

*

======================================================================

Design Statistics

# IOs

:9

Cell Usage :

# BELS

: 16

#

INV

:2

#

LUT2

:3

#

LUT2_L

:1

#

LUT3

:2

#

LUT4

:5

#

LUT4_L

:3

# FlipFlops/Latches

:9

#

FDC

:4

#

FDCE

:4

#

FDPE

:1

# Clock Buffers

:1

#

BUFGP

:1

# IO Buffers

:8

#

IBUF

:3

#

OBUF

:5

======================================================================

Device utilization summary:

Selected Device : 3s50tq144-4

Number of Slices:

7 out of

768

0%

Number of Slice Flip Flops:

9 out of

1536

0%

Number of 4 input LUTs:

16 out of

1536

1%

Number of IOs:

9

Number of bonded IOBs:

9 out of

97

9%

Number of GCLKs:

1 out of

8

12%

VTU 2009 Part A

40

ASIC Digital Design

Timing Report:

Setup/Hold to clock clk

-------------+------------+------------+------------------+--------+

| Setup to | Hold to

|

| Clock |

Source

| clk (edge) | clk (edge) |Internal Clock(s) | Phase |

-------------+------------+------------+------------------+--------+

SOC

|

1.826(R)|

-0.326(R)|clk_BUFGP

|

0.000|

comparator_in|

2.218(R)|

0.413(R)|clk_BUFGP

|

0.000|

-------------+------------+------------+------------------+--------+

Clock clk to Pad

------------+------------+------------------+--------+

| clk (edge) |

| Clock |

Destination |

to PAD

|Internal Clock(s) | Phase |

------------+------------+------------------+--------+

EOC

|

9.296(R)|clk_BUFGP

|

0.000|

Q<0>

|

8.613(R)|clk_BUFGP

|

0.000|

Q<1>

|

8.266(R)|clk_BUFGP

|

0.000|

Q<2>

|

8.174(R)|clk_BUFGP

|

0.000|

Q<3>

|

9.200(R)|clk_BUFGP

|

0.000|

------------+------------+------------------+--------+

Clock to Setup on destination clock clk

---------------+---------+---------+---------+---------+

| Src:Rise| Src:Fall| Src:Rise| Src:Fall|

Source Clock

|Dest:Rise|Dest:Rise|Dest:Fall|Dest:Fall|

---------------+---------+---------+---------+---------+

clk

|

3.540|

|

|

|

---------------+---------+---------+---------+---------+

To see timing results open *.TWR file from your project folder.

For eg. gates.twr or Adder_Parallel.twr

VTU 2009 Part A

41

ASIC Digital Design

Simulation Result:

Zoom in view

Power Consumption Report:

Power summary

|

I(mA)

|

P(mW)

|

---------------------------------------------------------------Total estimated power consumption

|

|

24 |

--Total Vccint

1.20V |

5 |

6 |

Total Vccaux

2.50V |

7 |

18 |

Total Vcco25

2.50V |

0 |

0 |

--Clocks

|

0 |

0 |

Inputs

|

0 |

0 |

Logic

|

0 |

0 |

Outputs

|

Vcco25 |

0 |

0 |

Signals

|

0 |

0 |

--Quiescent Vccint

1.20V |

5 |

6 |

Quiescent Vccaux

2.50V |

7 |

18 |

VTU 2009 Part A

42

You might also like

- 8.3.3.3 Lab - Collecting and Analyzing NetFlow Data - ILM PDFDocument13 pages8.3.3.3 Lab - Collecting and Analyzing NetFlow Data - ILM PDFEl Amrani MoutiaNo ratings yet

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosFrom EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosRating: 5 out of 5 stars5/5 (1)

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- X5 GT Wiring DiagramDocument2 pagesX5 GT Wiring DiagramBrian Thompson0% (1)

- VLSI Lab ManualDocument83 pagesVLSI Lab ManualSri SandhiyaNo ratings yet

- VLSI Lab Manual - 2022-1Document54 pagesVLSI Lab Manual - 2022-1SuhailNo ratings yet

- Ecad and Vlsi Lab ManualDocument125 pagesEcad and Vlsi Lab Manualsameer7mohammadNo ratings yet

- FPGA With Touch ScreenDocument23 pagesFPGA With Touch ScreenCharawut MasukNo ratings yet

- Programming AVR Micro Controllers in CDocument50 pagesProgramming AVR Micro Controllers in CDhishan AmaranathNo ratings yet

- Xilinx Lab RecordDocument76 pagesXilinx Lab RecordDivya SantoshiNo ratings yet

- FPGA Lab 07Document14 pagesFPGA Lab 07Zain AlamgirNo ratings yet

- 02Document8 pages02ahmedNo ratings yet

- VLSI Lab Manual - Exp 9 To 12Document42 pagesVLSI Lab Manual - Exp 9 To 12036 PRANEETHA S SNo ratings yet

- Sightline Video ProtocolDocument71 pagesSightline Video ProtocolStanley Ochieng' OumaNo ratings yet

- University College of Engineering ArniDocument51 pagesUniversity College of Engineering ArniVimalNo ratings yet

- ECE 2003 ManualDocument79 pagesECE 2003 Manualannambaka satishNo ratings yet

- Combinational Logic Design With Verilog: Reading AssignmentDocument15 pagesCombinational Logic Design With Verilog: Reading AssignmentRaghvendra SinghNo ratings yet

- Data Communications And Networking LAB FILEDocument19 pagesData Communications And Networking LAB FILEAnshul GeraNo ratings yet

- Fpga Module PresDocument45 pagesFpga Module PrescatchmereddyNo ratings yet

- VLSI LAB REPORTDocument70 pagesVLSI LAB REPORTSri SandhiyaNo ratings yet

- Vedic Multiplier DesignDocument39 pagesVedic Multiplier DesignVeena Sridhar100% (1)

- Vlsi RecordDocument61 pagesVlsi RecordRaghul MNo ratings yet

- SSRN Id4166233Document30 pagesSSRN Id4166233Kabilesh CmNo ratings yet

- HDL Manual 2017 5th Sem E&CE 15ECL58Document75 pagesHDL Manual 2017 5th Sem E&CE 15ECL58vishvakiranaNo ratings yet

- ECAD and VLSI Lab ManualDocument107 pagesECAD and VLSI Lab ManualHarold WilsonNo ratings yet

- Lec39 FullDocument27 pagesLec39 FullnmaravindNo ratings yet

- Index: Mallareddy College of Engineering and Technology-Mtech (Vlsi Lab)Document42 pagesIndex: Mallareddy College of Engineering and Technology-Mtech (Vlsi Lab)Vikas YerramNo ratings yet

- Print VlsiDocument104 pagesPrint VlsiDivagar Infant100% (1)

- Pic18 Pulse Width Modulation (PWM) DC Motor Speed Controller With The RPM Counter Project ErmicroblogDocument15 pagesPic18 Pulse Width Modulation (PWM) DC Motor Speed Controller With The RPM Counter Project Ermicroblogcreationist100% (2)

- IMA ADPCM EncDec Core SpecificationsDocument11 pagesIMA ADPCM EncDec Core SpecificationsMaria MafteiNo ratings yet

- VLSI Lab Manual Exercise ProblemsDocument38 pagesVLSI Lab Manual Exercise ProblemsPrakhar Kumar100% (1)

- Lab ManualDocument78 pagesLab Manualgurusandhya11No ratings yet

- Instructions:: IT185L - (CISCO 2) Actual Lab Skills Integration ChallengeDocument3 pagesInstructions:: IT185L - (CISCO 2) Actual Lab Skills Integration ChallengeNiño De Leon0% (1)

- PRO1 02E Training UnitsDocument10 pagesPRO1 02E Training UnitsMarinel MoraruNo ratings yet

- DSD Lab ManualDocument49 pagesDSD Lab Manualshailygoyal50% (2)

- Vlsi Manual 2013-2014Document36 pagesVlsi Manual 2013-2014hr_suresh_kNo ratings yet

- Signal Generator With Arduino Using DDS and Pico - Hackster - IoDocument9 pagesSignal Generator With Arduino Using DDS and Pico - Hackster - IoAhmed Abdel AzizNo ratings yet

- Vlsi Lab Manual 2013Document64 pagesVlsi Lab Manual 2013harish33330% (1)

- 6c7f5ec8 1643863161253Document38 pages6c7f5ec8 1643863161253Akshay GuptaNo ratings yet

- 5.2.3.7 Lab - Configuring Port Address Translation (PAT) - ILM PDFDocument12 pages5.2.3.7 Lab - Configuring Port Address Translation (PAT) - ILM PDFShelton Siziba100% (1)

- L5 - Combinational Logic Design With VerilogDocument17 pagesL5 - Combinational Logic Design With VerilogYogen SharmaNo ratings yet

- Writing Test Benches: A Free Application NoteDocument8 pagesWriting Test Benches: A Free Application NoteEhsan MahdaviNo ratings yet

- Chapter 7 Parameters Task and Function in VerilogDocument34 pagesChapter 7 Parameters Task and Function in Veriloghieu27718No ratings yet

- CO Lab Manual-MinDocument40 pagesCO Lab Manual-MinMatheen TabidNo ratings yet

- 8 Ways To Use A Digital Module in A CompactRIO SystemDocument6 pages8 Ways To Use A Digital Module in A CompactRIO SystemmafmonteNo ratings yet

- Serials IO Cards ASCIi - Allen Bradley ManualDocument30 pagesSerials IO Cards ASCIi - Allen Bradley ManualbadenkeyNo ratings yet

- Objective: Ce195277 - Delta Sigma Adc in Single-Ended Mode With Psoc 3/psoc 5LpDocument8 pagesObjective: Ce195277 - Delta Sigma Adc in Single-Ended Mode With Psoc 3/psoc 5LpFernando Andrés Cabrera SanchezNo ratings yet

- 1 Introduction To Real-Time ControlDocument8 pages1 Introduction To Real-Time ControlraghavNo ratings yet

- Verilog ExamplesDocument57 pagesVerilog ExamplesSandeepDeyNo ratings yet

- Vlsi Lab Manua2Document75 pagesVlsi Lab Manua2Nandan Bm100% (1)

- Implementation of 8 Bit Alu in Fpga: EX - NO. 1 DATE: 11-2-2010Document109 pagesImplementation of 8 Bit Alu in Fpga: EX - NO. 1 DATE: 11-2-2010Rajeshkumar KamarajNo ratings yet

- BRKRST-2612 Cisco IOS - Managing, Optimising and TweakingDocument105 pagesBRKRST-2612 Cisco IOS - Managing, Optimising and TweakingBoM36040No ratings yet

- Ni Sbrio-9651: Getting Started With The Sbrio-9651 Som Development KitDocument2 pagesNi Sbrio-9651: Getting Started With The Sbrio-9651 Som Development Kitkhin600No ratings yet

- EE8681 Lab ManualDocument110 pagesEE8681 Lab ManualVasunthara DNo ratings yet

- Simulink PLC Coder™ Release NotesDocument40 pagesSimulink PLC Coder™ Release NotesÍcaro VianaNo ratings yet

- Chapter 2Document40 pagesChapter 2s9222647No ratings yet

- Lab5 DSDDocument12 pagesLab5 DSDAhmed Razi UllahNo ratings yet

- F (A, B, C) A'BC' + A'BC+A' B' C'+ABC in SPO and POS Forms?: //casex ExampleDocument4 pagesF (A, B, C) A'BC' + A'BC+A' B' C'+ABC in SPO and POS Forms?: //casex ExampleSHREENo ratings yet

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- Dreamcast Architecture: Architecture of Consoles: A Practical Analysis, #9From EverandDreamcast Architecture: Architecture of Consoles: A Practical Analysis, #9No ratings yet

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkFrom EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkNo ratings yet

- Session 8: Innovation, Learning & Knowledge Management: Prof Ankur JainDocument12 pagesSession 8: Innovation, Learning & Knowledge Management: Prof Ankur JainKishore KumarNo ratings yet

- Session 7: Institutionalizing Organizational Culture: Prof Ankur Jain Ankur - Jain@iimrohtak - Ac.inDocument15 pagesSession 7: Institutionalizing Organizational Culture: Prof Ankur Jain Ankur - Jain@iimrohtak - Ac.inKishore KumarNo ratings yet

- Managing Change in Organizations: Ankure - Jain@iimrohtak - Ac.inDocument9 pagesManaging Change in Organizations: Ankure - Jain@iimrohtak - Ac.inKishore KumarNo ratings yet

- Transfer of Training CaseDocument2 pagesTransfer of Training CaseKishore KumarNo ratings yet

- EPuja CaseDocument17 pagesEPuja CaseKishore KumarNo ratings yet

- Session 15 4th Aug 2020 For StudentsDocument21 pagesSession 15 4th Aug 2020 For StudentsKishore KumarNo ratings yet

- ODD Session 11 Organizational Life Cycle For StudentsDocument12 pagesODD Session 11 Organizational Life Cycle For StudentsKishore KumarNo ratings yet

- Session 17 11th Aug For StudentsDocument85 pagesSession 17 11th Aug For StudentsKishore KumarNo ratings yet

- Design Effective L&D ProgramsDocument34 pagesDesign Effective L&D ProgramsKishore KumarNo ratings yet

- Optimize Your Product Portfolio Strategy with MARKSTRAT SimulationDocument5 pagesOptimize Your Product Portfolio Strategy with MARKSTRAT SimulationKishore KumarNo ratings yet

- Session 2 Learning Theories 9th June 2020 For StudentsDocument24 pagesSession 2 Learning Theories 9th June 2020 For StudentsKishore KumarNo ratings yet

- Session 9 3rd July 2020 For StudentsDocument22 pagesSession 9 3rd July 2020 For StudentsKishore KumarNo ratings yet

- Session 8 L&D Metrics and Analytics 25th June 2020 For StudentsDocument44 pagesSession 8 L&D Metrics and Analytics 25th June 2020 For StudentsKishore KumarNo ratings yet

- Session 1 Introduction To Training and Development 8th June For StudentsDocument22 pagesSession 1 Introduction To Training and Development 8th June For Studentssili coreNo ratings yet

- Aligning Learning & Development to Organizational StrategyDocument14 pagesAligning Learning & Development to Organizational StrategyKishore KumarNo ratings yet

- Muthoot Finance PDFDocument16 pagesMuthoot Finance PDFKishore KumarNo ratings yet

- Markstrat Simulation Team S Industry ConstellationDocument5 pagesMarkstrat Simulation Team S Industry ConstellationKishore KumarNo ratings yet

- Session 4 Internal Marketing Perspective 16th June 2020 For StudentsDocument20 pagesSession 4 Internal Marketing Perspective 16th June 2020 For StudentsKishore KumarNo ratings yet

- Jntuh Ettl Model Papers and Important QuestionsDocument7 pagesJntuh Ettl Model Papers and Important QuestionsKishore Kumar100% (1)

- Team S - Berlin - Period 2Document11 pagesTeam S - Berlin - Period 2Kishore KumarNo ratings yet

- Glenmark Research Report SummaryDocument10 pagesGlenmark Research Report SummaryKishore KumarNo ratings yet

- Session 5 Training Need Analysis 20 June 2020 For StudentsDocument18 pagesSession 5 Training Need Analysis 20 June 2020 For StudentsKishore KumarNo ratings yet

- Markstrat Simulation: Team: S (Berlin)Document11 pagesMarkstrat Simulation: Team: S (Berlin)Kishore KumarNo ratings yet

- Jntuh Ettl Model Papers and Important QuestionsDocument7 pagesJntuh Ettl Model Papers and Important QuestionsKishore Kumar100% (1)

- Jntuh Ettl Model Papers and Important QuestionsDocument7 pagesJntuh Ettl Model Papers and Important QuestionsKishore Kumar100% (1)

- Appscpolytechniclecturersg S Paper2007Document6 pagesAppscpolytechniclecturersg S Paper2007Lathasri MediboyanaNo ratings yet

- List of Books For ECEDocument16 pagesList of Books For ECEKishore KumarNo ratings yet

- 3 PH Connection Types 1519892309Document18 pages3 PH Connection Types 1519892309Alpagut Sencer KaracaNo ratings yet

- Electrical Power Window System CourseDocument18 pagesElectrical Power Window System CourseMuch Abdulah Nurhidayat100% (1)

- BaylorDocument140 pagesBaylorjairoleonx542691% (11)

- DSE91xx DSE92xx DSE94xx Series Operators ManualDocument74 pagesDSE91xx DSE92xx DSE94xx Series Operators ManualAlex GnNo ratings yet

- Specifications: Tx6A Shielded Copper Cabling System TX7000 Shielded Copper Cable - S/FTPDocument2 pagesSpecifications: Tx6A Shielded Copper Cabling System TX7000 Shielded Copper Cable - S/FTPΔΗΜΗΤΡΗΣ ΧΑΡΙΤΑΚΗΣNo ratings yet

- Process Control LoopDocument76 pagesProcess Control Loopsumanroyal100% (2)

- Motorola HZ800 ManualDocument28 pagesMotorola HZ800 Manualbsd_storesNo ratings yet

- Workshop On Digital Design With FPGA Organized by EiTRADocument4 pagesWorkshop On Digital Design With FPGA Organized by EiTRAmurali036No ratings yet

- Data Connector - SACC-M12MSD-4Q SH - 1543223Document3 pagesData Connector - SACC-M12MSD-4Q SH - 1543223Rafael DavidNo ratings yet

- Bluetooth Hands-Free System GuideDocument16 pagesBluetooth Hands-Free System Guidegswalia818342No ratings yet

- Experion LCN Tech Spec PDFDocument27 pagesExperion LCN Tech Spec PDFjashkishoreNo ratings yet

- Manual TLK48 InglesDocument14 pagesManual TLK48 Inglesselyani13No ratings yet

- MIMO Part 1Document30 pagesMIMO Part 1Abu Huzaifah BidinNo ratings yet

- STK0825F 1Document8 pagesSTK0825F 1Námaste AbaddonNo ratings yet

- Asus P5GPL-X SE Manual Placa MadreDocument100 pagesAsus P5GPL-X SE Manual Placa MadreSandor InopiaNo ratings yet

- 96-Cell Battery Stand ProposalDocument2 pages96-Cell Battery Stand ProposalCésar Fidel CruzNo ratings yet

- Using the 9XR Pro for More than Eight ChannelsDocument9 pagesUsing the 9XR Pro for More than Eight ChannelsPatricio Daniel Villalobos RojasNo ratings yet

- XTS5000 Parts CatalogDocument16 pagesXTS5000 Parts CatalogSeanFlynnNo ratings yet

- English User Guide - 0044-033-05 - enDocument16 pagesEnglish User Guide - 0044-033-05 - enZemouraMohamedNo ratings yet

- Algunos Codigos MAXXFORCE 13Document3 pagesAlgunos Codigos MAXXFORCE 13Juan AcostaNo ratings yet

- Sony CDX-GT45U/CDX-GT44UDocument52 pagesSony CDX-GT45U/CDX-GT44Uusama1571No ratings yet

- Introduction To In-Circuit TestingDocument123 pagesIntroduction To In-Circuit TestingMed Medy Fehem100% (1)

- Current ks3Document2 pagesCurrent ks3Fadi Abu RaidNo ratings yet

- Interpret AC Voltages & CurrentsDocument46 pagesInterpret AC Voltages & CurrentsKelvin LooiNo ratings yet

- Conventional and CAD of Electrical Machines EEE023Document3 pagesConventional and CAD of Electrical Machines EEE023Dheeraj KumarNo ratings yet

- Demon Analysis PDFDocument21 pagesDemon Analysis PDFBùi Trường Giang100% (1)

- Transformers HitachiDocument10 pagesTransformers Hitachiedy985No ratings yet

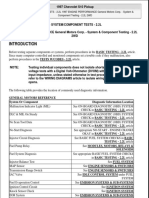

- System Component Tests Chevrolet S10Document19 pagesSystem Component Tests Chevrolet S10Maxi Sardi100% (1)

- Service Manual MrInspire 2200Document227 pagesService Manual MrInspire 2200Neyo Amptic LesserNo ratings yet