Professional Documents

Culture Documents

HW-1 16

HW-1 16

Uploaded by

Anuj DsouzaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

HW-1 16

HW-1 16

Uploaded by

Anuj DsouzaCopyright:

Available Formats

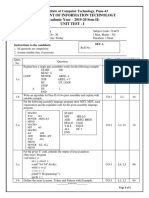

ECE 658 VLSI Design - I Homework-1 Due Date: Sept.

15, 16

Dr. D. Misra

No collaboration is permitted on this assignment. Your work must be your own. Submit a

PDF file in moodle.

Question 1.

Sketch the transistor-level schematics for a CMOS 4-input NOR gate and a CMOS 4-input NAND

gate. Also, provide a stick diagram for each gate. Be sure your stick diagram differentiates between

layers (metal, active, and poly) and indicates the different active regions (N+ and P-). See the

lecture notes for an example. Computer generated figures are preferred but hand-drawn figures

will be acceptable.

Question 2.

For each of the output functions below design a CMOS gate to implement the logic. Provide both

a schematic and stick diagram for each. Draw the transistor- level schematic. Be sure your stick

diagram differentiates between layers (metal, active, and poly) and indicates the different active

regions (N+ and P-). See the lecture notes for an example. Computer generated figures are

preferred but hand-drawn figures will be acceptable. Also, provide a gate-level design.

F = (A+B) . C

F = (A+B) . (C+D)

Question 3.

Figure below shows the stick diagram of a 2-input NAND gate. Sketch the side view (cross-

section) of the gate from X to X’ and Z to Z’

Z’

You might also like

- Lab1 - nMOS & pMOSDocument17 pagesLab1 - nMOS & pMOSThevenin Norton TOng TongNo ratings yet

- Acoe419 AssignmentDocument3 pagesAcoe419 AssignmentMamas VartholomeouNo ratings yet

- VLSI 設計導論 期末作業: Y AAA BB CCCDocument2 pagesVLSI 設計導論 期末作業: Y AAA BB CCC陳禹翔No ratings yet

- Logical EffortDocument108 pagesLogical EffortPranav DarganNo ratings yet

- Physical Design of CMOS Chips in Six Easy StepsDocument14 pagesPhysical Design of CMOS Chips in Six Easy StepskjvivekNo ratings yet

- Assignment 2 Unit 2Document3 pagesAssignment 2 Unit 2Maharshi Sanand Yadav TNo ratings yet

- Used in VLSI Technology (I) N-Diffusion (Ii) Polysilicon (Iii) Metal 1 (Iv) ImpactDocument1 pageUsed in VLSI Technology (I) N-Diffusion (Ii) Polysilicon (Iii) Metal 1 (Iv) ImpactprofmnsNo ratings yet

- 4-SNBhat - StickdiagraFile Setms - IUCEEEDocument38 pages4-SNBhat - StickdiagraFile Setms - IUCEEEranjithece1No ratings yet

- T.E. - Examination, (Revised) Code:66318: (SemesterDocument3 pagesT.E. - Examination, (Revised) Code:66318: (SemesterSandhya GaikwadNo ratings yet

- VLSI Question PaperDocument3 pagesVLSI Question Paper209X1A04D2 SHAIK ASMANo ratings yet

- Lab 2 NAND Gate Layout ECE334: MAX TutorialDocument6 pagesLab 2 NAND Gate Layout ECE334: MAX TutorialdamasgateNo ratings yet

- Dec50143 PW3Document10 pagesDec50143 PW3Alif FirdausNo ratings yet

- R7310404 Digital IC ApplicationsDocument1 pageR7310404 Digital IC ApplicationssivabharathamurthyNo ratings yet

- Cmos UNITDocument15 pagesCmos UNITKranthi VkrNo ratings yet

- CS 801D PDFDocument4 pagesCS 801D PDFarnab paulNo ratings yet

- EEE3602 AssignmentDocument5 pagesEEE3602 AssignmentUmair NazeerNo ratings yet

- 1 Stick DiagramDocument37 pages1 Stick DiagramSruti SinghNo ratings yet

- CENG3490 - VLSI Design: Spring 2012Document15 pagesCENG3490 - VLSI Design: Spring 2012Aarti KhareNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument29 pages3 Hours / 70 Marks: Seat Notechstack901No ratings yet

- Q Paper 09ec61 May June 2012Document2 pagesQ Paper 09ec61 May June 2012Bhaskar MishraNo ratings yet

- R7310404 Digital IC ApplicationsDocument1 pageR7310404 Digital IC ApplicationssivabharathamurthyNo ratings yet

- 9A04306 Digital Logic DesignDocument2 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- Lab 2 NAND Gate Layout ECE334S: MAX TutorialDocument6 pagesLab 2 NAND Gate Layout ECE334S: MAX TutorialAnkur ThakurNo ratings yet

- Practical Work 3 - CMOS + Rubric PDFDocument25 pagesPractical Work 3 - CMOS + Rubric PDFRiki SmithNo ratings yet

- ECE 301 - Digital Electronics: NAND and NOR Circuits, Multi-Level Logic Circuits, and Multiple-Output Logic CircuitsDocument30 pagesECE 301 - Digital Electronics: NAND and NOR Circuits, Multi-Level Logic Circuits, and Multiple-Output Logic CircuitsVIKH33No ratings yet

- SP Unit Test 1 - Set ADocument1 pageSP Unit Test 1 - Set APratiksha KambleNo ratings yet

- 2018 Winter DTE 3I - Q - 22320 - CODocument4 pages2018 Winter DTE 3I - Q - 22320 - CO14adisunnyNo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- StickDocument16 pagesStickBikram PaulNo ratings yet

- B.Tech II Year I Semester (R13) Supplementary Examinations June 2017Document2 pagesB.Tech II Year I Semester (R13) Supplementary Examinations June 2017Kareem KhanNo ratings yet

- Basics of Stick Diagrams and LayoutsDocument21 pagesBasics of Stick Diagrams and LayoutsSUSHANTH K JNo ratings yet

- 2019 Summer Question Paper (Msbte Study Resources)Document3 pages2019 Summer Question Paper (Msbte Study Resources)Ashutosh PatilNo ratings yet

- Vlsi Homework-1Document1 pageVlsi Homework-1jameelahmadNo ratings yet

- 9a04605 Vlsi DesignDocument1 page9a04605 Vlsi DesignsivabharathamurthyNo ratings yet

- CSCE-312 - Summer 2020 - Sample Midterm Exam: Name: UinDocument9 pagesCSCE-312 - Summer 2020 - Sample Midterm Exam: Name: UinannyNo ratings yet

- Jntua University Previous Question Papers: Dept., of E.C.E, RCEWDocument4 pagesJntua University Previous Question Papers: Dept., of E.C.E, RCEWHarshini ANo ratings yet

- SP ESE QuestionPaper Sem1 2019Document9 pagesSP ESE QuestionPaper Sem1 2019SK Relaxing MusicNo ratings yet

- B.Tech II Year I Semester (R13) Regular & Supplementary Examinations December 2015Document1 pageB.Tech II Year I Semester (R13) Regular & Supplementary Examinations December 2015jayarami reddy pNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument88 pages3 Hours / 70 Marks: Seat Noyashbirari29No ratings yet

- WWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic DesignDocument4 pagesWWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic Designbadiganti tejakrishnaNo ratings yet

- Chapter 5Document61 pagesChapter 5Faiz MohdNo ratings yet

- RT 21053112016Document4 pagesRT 21053112016RaunaqNo ratings yet

- UEC001Document2 pagesUEC001Abhav BansalNo ratings yet

- Chapter # 3: Multi-Level Combinational Logic: Contemporary Logic Design Contemporary Logic DesignDocument13 pagesChapter # 3: Multi-Level Combinational Logic: Contemporary Logic Design Contemporary Logic Designrtavares_980738No ratings yet

- Sample CSE370 Final Exam Questions: Logic MinimizationDocument8 pagesSample CSE370 Final Exam Questions: Logic MinimizationQaseem HussainNo ratings yet

- VlsiDocument16 pagesVlsiVishnu Vijay SNo ratings yet

- 2013 2019 Questions16 Elec A4Document75 pages2013 2019 Questions16 Elec A4Humaira HaroonNo ratings yet

- 80 Marks Sample Question PaperDocument3 pages80 Marks Sample Question Papersayli mNo ratings yet

- Comp SC 18Document8 pagesComp SC 18Masiur RahamanNo ratings yet

- Practical Work 4Document14 pagesPractical Work 4Kalai ShanNo ratings yet

- 8.RCX - View of CMOS Inverter and Nand GateDocument6 pages8.RCX - View of CMOS Inverter and Nand GatealokjadhavNo ratings yet

- 2018 Winter Question Paper (Msbte Study Resources)Document4 pages2018 Winter Question Paper (Msbte Study Resources)Parth patkarNo ratings yet

- Lab 9 (Group 4) - 1Document11 pagesLab 9 (Group 4) - 1MUHAMMAD HUZAIFANo ratings yet

- EC6302 Digital ElectronicsDocument13 pagesEC6302 Digital ElectronicsDhanaa DhanagopalNo ratings yet

- Ec0033-Asic Design-Model Qp-Vii Sem-Set1Document1 pageEc0033-Asic Design-Model Qp-Vii Sem-Set1skarthikpriyaNo ratings yet

- 4.essay Type QuestionsDocument4 pages4.essay Type Questionsvadlamudi TharunNo ratings yet

- Getting Started With Hspice - A TutorialDocument10 pagesGetting Started With Hspice - A TutorialSwati ChavanNo ratings yet

- Static CMOS Gates: F (A+B) - (C+D)Document22 pagesStatic CMOS Gates: F (A+B) - (C+D)Puneet ShrivastavaNo ratings yet