Professional Documents

Culture Documents

Open Ended Experiment Basic Electronics Engineering (Es201) 3CSE-9Y

Uploaded by

Kush0 ratings0% found this document useful (0 votes)

196 views2 pagesOriginal Title

open ended expt. 3CSE 9Y.docx

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

196 views2 pagesOpen Ended Experiment Basic Electronics Engineering (Es201) 3CSE-9Y

Uploaded by

KushCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 2

OPEN ENDED EXPERIMENT

BASIC ELECTRONICS ENGINEERING (ES201)

3CSE-9Y

GROUP ENROLLMENT NAME EXPERIMENT

NUMBER

1 A2305218575 JALAJ AGARWAL To design a voltage

A2305218576 LAVNEESH SAINI regulator using Zener

A2305218579 VARSHA AGRAWAL diode that will

A2305218580 VABHAV SHARMA maintain a constant

output across load

resistor with a

variable dc input

voltage. Also

calculate maximum

Zener current and

power.

2 A2305218581 HIMANSHU VERMA To design voltage

A2305218584 SUNIDHI divider biasing circuit

A2305218586 RAHUL YADAV for BJT as an amplifier

A2305218587 ATUL CHAUDHARY to obtain the

frequency response

curve and determine

the mid frequency

gain, lower and

higher cutoff

frequency of the

amplifier circuit.

3 A2305218589 TANYA GOYAL Design a two stage

A2305218590 DIGANT CHANDELA transistor amplifier

A2305218591 SAURABH which employs

A2305218592 HEMANYA MEHTA emitter follower

configuration prior to

common base

configuration to

ensure that the

maximum percentage

of applied signal

appears at the input

terminals of

common base

amplifier. The

following information

is given:

Emitter Follower: Z i

=10K Ω, Zo = 12Ω, A V

=1. Common Base: Z i

=26 Ω, Zo = 5.1KΩ, A

V =240.

R S = 1K Ω, R L = 8.2K

Ω

4 A2305218595 KARAN MALIK Design of common

A2305218597 VANSH GOYAL source amplifier for

A2305218598 CHANDAN SHARMA desired ac voltage

A2305218601 KSHITIZ SHARMA gain using self-biasing

circuit and determine

various parameters

and draw drain

characteristics.

5 A2305218602 SIDDHARTH MAKOL Design and

A2305218603 VANDIT JAIN implement clippers

A2305218604 AYUSH GUPTA (biased and unbiased)

A2305218605 SAKSHI NIMJE using OP-AMP IC 741

and other necessary

components.

6 A2305218606 GUNJAN SAINI Design and

A2305218737 ABHINAV SAXENA implement full

A2305218738 RAJ THAKUR subtractor by using

A2305218037 PRERIT RAJPUT minimum number of

A2305218065 YUGANSH PREET Universal gates.

You might also like

- VHDL Based Circuits Design and Synthesis On FPGA: A Dice Game Example For EducationDocument6 pagesVHDL Based Circuits Design and Synthesis On FPGA: A Dice Game Example For EducationRam RajaNo ratings yet

- Generation of High Voltage DC Using Diodes & Capacitors in Ladder NetworkDocument6 pagesGeneration of High Voltage DC Using Diodes & Capacitors in Ladder NetworkEditor IJRITCCNo ratings yet

- Open Ended 1Document12 pagesOpen Ended 1AneeshaNo ratings yet

- Lighting Schemes Design: Classroom and Office Illumination CalculationsDocument29 pagesLighting Schemes Design: Classroom and Office Illumination Calculationsjames40440No ratings yet

- Eec 752 Electronic Circuit Design LabDocument1 pageEec 752 Electronic Circuit Design LabAnonymous eWMnRr70q75% (4)

- EEE 308 Practical Experiment No. 1 Matric Number......................... Speed Control On Single Phase Induction MotorDocument2 pagesEEE 308 Practical Experiment No. 1 Matric Number......................... Speed Control On Single Phase Induction MotorOladeji Ifedayo RNo ratings yet

- Realization of a Simple AND-OR Circuit and Propagation Delay StudyDocument6 pagesRealization of a Simple AND-OR Circuit and Propagation Delay StudyJoanne Lai100% (1)

- EE 215 Lab 3 HandoutDocument5 pagesEE 215 Lab 3 HandoutArnav MathurNo ratings yet

- Articol - Dewan - Rectifier Filter Design PDFDocument7 pagesArticol - Dewan - Rectifier Filter Design PDFCovaci BogdanNo ratings yet

- Oscilloscope & Function Generator Operation: Department of Electrical Engineering Network Analysis LabDocument3 pagesOscilloscope & Function Generator Operation: Department of Electrical Engineering Network Analysis LabUsairum MirzaNo ratings yet

- Et438b 7Document42 pagesEt438b 7tina100% (1)

- "Bridge B2HZ" For The Control of A DC MotorDocument16 pages"Bridge B2HZ" For The Control of A DC MotorhadiNo ratings yet

- Design of A Non-Ideal Buck ConverterDocument13 pagesDesign of A Non-Ideal Buck ConverterJames Xgun100% (1)

- High Voltage Direct Current Transmission: Converters, Systems and DC GridsFrom EverandHigh Voltage Direct Current Transmission: Converters, Systems and DC GridsNo ratings yet

- Verify Thevenin's TheoremDocument10 pagesVerify Thevenin's TheoremJay SathvaraNo ratings yet

- Network Analysis: Sharique Najam MuzaffarDocument32 pagesNetwork Analysis: Sharique Najam Muzaffarmanzur_a_m100% (1)

- FET Exam Questions Cover BJT, MOSFET CircuitsDocument185 pagesFET Exam Questions Cover BJT, MOSFET CircuitsCham Raul100% (1)

- Switch Mode Power Supply Design and Efficiency OptimizationDocument19 pagesSwitch Mode Power Supply Design and Efficiency Optimizationkhan aliNo ratings yet

- Investigation of the Usefulness of the PowerWorld Simulator Program: Developed by "Glover, Overbye & Sarma" in the Solution of Power System ProblemsFrom EverandInvestigation of the Usefulness of the PowerWorld Simulator Program: Developed by "Glover, Overbye & Sarma" in the Solution of Power System ProblemsNo ratings yet

- Eletronics Lab Report - TTLDocument2 pagesEletronics Lab Report - TTLThan Lwin AungNo ratings yet

- Series & Parallel Resistance ExperimentsDocument2 pagesSeries & Parallel Resistance ExperimentsNisa ElNo ratings yet

- Brake Load Test of Squirel Cage Induction Motor 3 PhaseDocument7 pagesBrake Load Test of Squirel Cage Induction Motor 3 Phasejassisc100% (1)

- Aim: To Test Differentiator and Integrator Circuits Using Ua741op-AmpDocument8 pagesAim: To Test Differentiator and Integrator Circuits Using Ua741op-AmpAvinash Nandakumar100% (1)

- Symmetrical Fault AnalysisDocument36 pagesSymmetrical Fault Analysisdileep kumarNo ratings yet

- Transformers - Three Phase TransformersDocument25 pagesTransformers - Three Phase TransformersDeepakDeep100% (1)

- EEE 101 - Lect23Document12 pagesEEE 101 - Lect23Basim AlthafNo ratings yet

- Electrical and Electronics Lab Manual For Mechanical EngineeringDocument21 pagesElectrical and Electronics Lab Manual For Mechanical EngineeringSreerag Kunnathu SugathanNo ratings yet

- Induction Motor Model Example SolutionDocument8 pagesInduction Motor Model Example SolutionJocel GuzmanNo ratings yet

- Bridge Full Wave Rectifier - CheggDocument3 pagesBridge Full Wave Rectifier - Cheggsal27adamNo ratings yet

- Wireless Stepper Motor ControlDocument2 pagesWireless Stepper Motor ControlHarsha100% (1)

- Electronic Circuits & Logic Design Lab ManualDocument83 pagesElectronic Circuits & Logic Design Lab ManualsunandaalurNo ratings yet

- ENA Lab 9 Balanced Three-Phase Circuit (Software)Document12 pagesENA Lab 9 Balanced Three-Phase Circuit (Software)Mohammed Ahmad OsamaNo ratings yet

- Philadelphia University Final Exam for Power Electronics CourseDocument4 pagesPhiladelphia University Final Exam for Power Electronics CourseSaif UddinNo ratings yet

- EMT Assignment 5Document15 pagesEMT Assignment 5Kelvin KohNo ratings yet

- 12V To 120V DC - DC Converter Using Power Electronics For Higher Efficiency and Reliable OperationDocument23 pages12V To 120V DC - DC Converter Using Power Electronics For Higher Efficiency and Reliable OperationRaghav ChawlaNo ratings yet

- Electric Power Engineering Lecture NotesDocument209 pagesElectric Power Engineering Lecture NotesRaj Boda0% (1)

- Multisim Unsolved Questions BITS PilaniDocument2 pagesMultisim Unsolved Questions BITS Pilanimanish_genus100% (1)

- Electronics Lab Exp3.pdfDocument17 pagesElectronics Lab Exp3.pdfgacc4sitesNo ratings yet

- Lab Manual - Power ElectronicsDocument6 pagesLab Manual - Power Electronicsprisoner90No ratings yet

- Assignments StudentsDocument2 pagesAssignments StudentsManju Chakraborty100% (1)

- Chapter 3: Ac Power AnalysisDocument40 pagesChapter 3: Ac Power AnalysisAtyia Javed100% (1)

- Advanced Biomechanics AssignmentDocument1 pageAdvanced Biomechanics AssignmentsmalldotNo ratings yet

- Speed Torque Characteristics of 3 Phase Induction MotorDocument4 pagesSpeed Torque Characteristics of 3 Phase Induction MotorAdi AdnanNo ratings yet

- ICL8038 Linear Sweep Function Generator CCTDocument2 pagesICL8038 Linear Sweep Function Generator CCTian_new100% (1)

- Nodal Analysis Guide and 5 Question Examples SolvedDocument7 pagesNodal Analysis Guide and 5 Question Examples SolvedShivam ModiNo ratings yet

- LIC Lab ManualDocument65 pagesLIC Lab ManualBala Subramanian0% (1)

- Design Calculations For Buck-Boost Converters: Michael Green Advanced Low Power SolutionsDocument12 pagesDesign Calculations For Buck-Boost Converters: Michael Green Advanced Low Power SolutionsnandhakumarmeNo ratings yet

- Fundamentals of Electronics 2: Continuous-time Signals and SystemsFrom EverandFundamentals of Electronics 2: Continuous-time Signals and SystemsNo ratings yet

- HV Engineering: Generation of High Frequency Ac High Voltage Using Tesla CoilDocument6 pagesHV Engineering: Generation of High Frequency Ac High Voltage Using Tesla CoilAdnan AliNo ratings yet

- Design and Implementation of A Solar Charge Controller With Variable OutputDocument12 pagesDesign and Implementation of A Solar Charge Controller With Variable OutputManish kumar100% (1)

- 325 Lab 8 ReportDocument10 pages325 Lab 8 Reportapi-241454978No ratings yet

- Eed3001 Lab2 Single Phase Transformer Loading EM3000Document5 pagesEed3001 Lab2 Single Phase Transformer Loading EM3000Burak YılmazNo ratings yet

- AC Network Theorems: Prepared By: Karthik Chandran Pillai IV Sem, EEE (B)Document22 pagesAC Network Theorems: Prepared By: Karthik Chandran Pillai IV Sem, EEE (B)hodeegits9526100% (1)

- Image ImpedanceDocument16 pagesImage ImpedanceErick Wangila WanyonyiNo ratings yet

- BJT Transistor TheoryDocument63 pagesBJT Transistor TheoryspidyheroNo ratings yet

- Electronics 1 Lab Manual PDFDocument30 pagesElectronics 1 Lab Manual PDFAnonymous 7y7TeR0% (1)

- Solution:: Fig. 2 Shows The Required Common Base ConnectionDocument9 pagesSolution:: Fig. 2 Shows The Required Common Base ConnectionSwathi Gudivada100% (1)

- Assignmnet 02 RevisedDocument3 pagesAssignmnet 02 RevisedBilal Ayub100% (1)

- Practical 10: Echo "Today Is $ (Date) " Echo - e "List of Logged On Users and What They Are Doing:/n $ (W) "Document1 pagePractical 10: Echo "Today Is $ (Date) " Echo - e "List of Logged On Users and What They Are Doing:/n $ (W) "KushNo ratings yet

- AIM - TO Study Linux General Purpose Commands: Practical 2Document3 pagesAIM - TO Study Linux General Purpose Commands: Practical 2KushNo ratings yet

- Digraph Representation of RelationsDocument10 pagesDigraph Representation of RelationsKushNo ratings yet

- Practical 4: Name - Kushaggra Chaudhary ENROLL - A2305218568 Section - 7cse 9XDocument4 pagesPractical 4: Name - Kushaggra Chaudhary ENROLL - A2305218568 Section - 7cse 9XKushNo ratings yet

- AIM - TO Study VI Editor: Practical 3Document2 pagesAIM - TO Study VI Editor: Practical 3KushNo ratings yet

- Relation & Properties in Discrete MathematicsDocument11 pagesRelation & Properties in Discrete MathematicsKushNo ratings yet

- Mobility ManagementDocument30 pagesMobility ManagementKushNo ratings yet

- Bellman-Ford Algorithm: Improvement and Experimental EvaluationDocument4 pagesBellman-Ford Algorithm: Improvement and Experimental EvaluationKushNo ratings yet

- DMS - Mod-2 - L4 - Equvalence and Partial Order RelationDocument7 pagesDMS - Mod-2 - L4 - Equvalence and Partial Order RelationKushNo ratings yet

- Dbms 4&5&6Document10 pagesDbms 4&5&6KushNo ratings yet

- Types of Relations in Discrete MathematicsDocument13 pagesTypes of Relations in Discrete MathematicsKushNo ratings yet

- Name - Kushaggra Chaudhary ENROLL - A2305218568 Sec-5Cse 9X Quicksort External PracticalDocument2 pagesName - Kushaggra Chaudhary ENROLL - A2305218568 Sec-5Cse 9X Quicksort External PracticalKushNo ratings yet

- Uploads - Notes - Btech - 4sem - It - DBMS FRONT PAGE LAB MANUALDocument3 pagesUploads - Notes - Btech - 4sem - It - DBMS FRONT PAGE LAB MANUALKushNo ratings yet

- Mobile IP: Amity School of Engineering & TechnologyDocument19 pagesMobile IP: Amity School of Engineering & TechnologyKushNo ratings yet

- Wlans Ieee 802.11 Standard: Amity School of Engineering & TechnologyDocument29 pagesWlans Ieee 802.11 Standard: Amity School of Engineering & TechnologyKushNo ratings yet

- General Packet Radio System (GPRS)Document8 pagesGeneral Packet Radio System (GPRS)KushNo ratings yet

- Introduction To Mobile Computing &PCS ArchitectureDocument25 pagesIntroduction To Mobile Computing &PCS ArchitectureKushNo ratings yet

- Introduction to Cryptography (1): What is CryptographyDocument29 pagesIntroduction to Cryptography (1): What is Cryptographyprashantyadav98No ratings yet

- Uploads - Notes - Btech - 4sem - It - DBMS FRONT PAGE LAB MANUAL PDFDocument3 pagesUploads - Notes - Btech - 4sem - It - DBMS FRONT PAGE LAB MANUAL PDFKushNo ratings yet

- ReadmeDocument1 pageReadmeKushNo ratings yet

- German (A2305218568)Document3 pagesGerman (A2305218568)KushNo ratings yet

- Dbms Practical PrintDocument10 pagesDbms Practical PrintKushNo ratings yet

- Invoice 10500042309Document1 pageInvoice 10500042309KushNo ratings yet

- Experiment 2 - 14Document1 pageExperiment 2 - 14KushNo ratings yet

- ENCh 01Document34 pagesENCh 01jonty777No ratings yet

- Dbms Practical PrintDocument10 pagesDbms Practical PrintKushNo ratings yet

- The Trader Business PlanDocument4 pagesThe Trader Business Planmitesh100% (4)

- Kushaggra NTCC Report PlagDocument19 pagesKushaggra NTCC Report PlagKushNo ratings yet

- TutorialSheet NumericalMethodsRevDocument7 pagesTutorialSheet NumericalMethodsRevKushNo ratings yet

- Viden Io Amity Aset Matlab Practical File Basic Simulation Lab Manual UpdatedDocument50 pagesViden Io Amity Aset Matlab Practical File Basic Simulation Lab Manual UpdatedKushNo ratings yet

- Multiphase PWM Regulator For Amd Fusion™ Mobile Cpus Using Svi 2.0Document37 pagesMultiphase PWM Regulator For Amd Fusion™ Mobile Cpus Using Svi 2.0Denis DenisovNo ratings yet

- Fire Alarm and Water Turbine Sprinkler Using Zener DiodeDocument23 pagesFire Alarm and Water Turbine Sprinkler Using Zener DiodeJonathan SaydeNo ratings yet

- 056/057 Psm-Si: Vishay BccomponentsDocument11 pages056/057 Psm-Si: Vishay BccomponentsAli KeyvanNo ratings yet

- Electric Diagram Skandic PDFDocument44 pagesElectric Diagram Skandic PDFMirko Eugenin0% (1)

- Section 9 - RTD-Based Protection: SEL-751A Feeder Protection Relay - APP 751ADocument18 pagesSection 9 - RTD-Based Protection: SEL-751A Feeder Protection Relay - APP 751ABouazzaNo ratings yet

- Emlab 2Document21 pagesEmlab 2hafizrahimmitNo ratings yet

- DatasheetDocument4 pagesDatasheetNaresh KumarNo ratings yet

- Product Data Sheet: Circuit Breaker Compact NSX250F - TMD - 250 A - 3 Poles 2dDocument3 pagesProduct Data Sheet: Circuit Breaker Compact NSX250F - TMD - 250 A - 3 Poles 2dwmNo ratings yet

- S-AAA-SWG-MV-GIS (Rev.0-2015)Document28 pagesS-AAA-SWG-MV-GIS (Rev.0-2015)Muhammad hussainNo ratings yet

- NEW Slimpak EC Box Fan (SLPT EC) : ElectricalDocument6 pagesNEW Slimpak EC Box Fan (SLPT EC) : ElectricalRegieNo ratings yet

- General Product Information for Schneider Electric ABE7CPA03 Connection Sub-BaseDocument4 pagesGeneral Product Information for Schneider Electric ABE7CPA03 Connection Sub-BaseJose LunaNo ratings yet

- Servo Stabilizer Construction, Working and Application: EE 301 Power ElectronicsDocument9 pagesServo Stabilizer Construction, Working and Application: EE 301 Power ElectronicsHani Ameen SaqerNo ratings yet

- Nice ROBO RO 1000Document88 pagesNice ROBO RO 1000duartesilva100No ratings yet

- Engine Governing Systems Actuator GuideDocument6 pagesEngine Governing Systems Actuator GuideGONZALO100% (1)

- Troubleshooting Manual AK06 UMKA03Document271 pagesTroubleshooting Manual AK06 UMKA03Jorge JimenezNo ratings yet

- Simonazzi Motorized ValveDocument6 pagesSimonazzi Motorized Valveronal553No ratings yet

- Kishenpur Grid Station CompleteDocument39 pagesKishenpur Grid Station CompletepunitkapoorNo ratings yet

- Diode: Tube Diode (Now Rarely Used Except in Some High-Power Technologies) IsDocument16 pagesDiode: Tube Diode (Now Rarely Used Except in Some High-Power Technologies) IsGorishsharmaNo ratings yet

- Siemens MPCB CertificateDocument12 pagesSiemens MPCB CertificateSreegith ChelattNo ratings yet

- Afn3400 Alpha-Mos PDFDocument7 pagesAfn3400 Alpha-Mos PDFdoraemon007No ratings yet

- Report - Flashing LED ExperimentDocument6 pagesReport - Flashing LED ExperimentAnonymous rsxb6oEGpNo ratings yet

- FGDHDocument21 pagesFGDHkishorshinde75No ratings yet

- Suzuki SX4 2009 Tablero y FusilerasDocument22 pagesSuzuki SX4 2009 Tablero y FusilerasMartin BravoNo ratings yet

- Electric Duct Heaters PDFDocument64 pagesElectric Duct Heaters PDFFizh RatNo ratings yet

- Transients in Solar Photovoltaic Systems During Lightning Strikes To A Transmission LineDocument31 pagesTransients in Solar Photovoltaic Systems During Lightning Strikes To A Transmission LineHải Nguyễn HoàngNo ratings yet

- MRP Mar 20abb 13Document71 pagesMRP Mar 20abb 13tceterexNo ratings yet

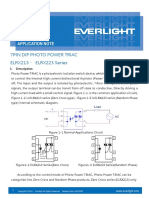

- ELRX213 - X223 Application Note Ver2.0ENDocument7 pagesELRX213 - X223 Application Note Ver2.0ENLuis HuanqqueNo ratings yet

- Electrical Specification SummaryDocument7 pagesElectrical Specification SummaryNATHANNo ratings yet

- Saudi Company SpecsDocument21 pagesSaudi Company Specskapamaro60% (5)

- PANASONIC LIFE SOLUTIONS PRICELIST FOR MCB AND MCCBDocument7 pagesPANASONIC LIFE SOLUTIONS PRICELIST FOR MCB AND MCCBElectrical JKFMNo ratings yet