Professional Documents

Culture Documents

Irfp450 PDF

Irfp450 PDF

Uploaded by

mkOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Irfp450 PDF

Irfp450 PDF

Uploaded by

mkCopyright:

Available Formats

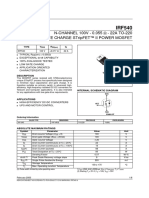

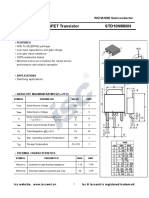

Philips Semiconductors Product specification

PowerMOS transistors IRFP460

Avalanche energy rated

FEATURES SYMBOL QUICK REFERENCE DATA

• Repetitive Avalanche Rated d

• Fast switching VDSS = 500 V

• Stable off-state characteristics

• High thermal cycling performance ID = 20 A

g

• Low thermal resistance

RDS(ON) ≤ 0.27 Ω

s

GENERAL DESCRIPTION PINNING SOT429 (TO247)

N-channel, enhancement mode PIN DESCRIPTION

field-effect power transistor,

intended for use in off-line switched 1 gate

mode power supplies, T.V. and

computer monitor power supplies, 2 drain

d.c. to d.c. converters, motor control

circuits and general purpose 3 source

switching applications.

tab drain 2

1 3

The IRFP460 is supplied in the

SOT429 (TO247) conventional

leaded package.

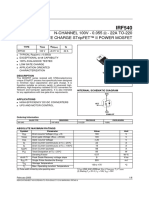

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

VDSS Drain-source voltage Tj = 25 ˚C to 150˚C - 500 V

VDGR Drain-gate voltage Tj = 25 ˚C to 150˚C; RGS = 20 kΩ - 500 V

VGS Gate-source voltage - ± 30 V

ID Continuous drain current Tmb = 25 ˚C; VGS = 10 V - 20 A

Tmb = 100 ˚C; VGS = 10 V - 12.4 A

IDM Pulsed drain current Tmb = 25 ˚C - 80 A

PD Total dissipation Tmb = 25 ˚C - 250 W

Tj, Tstg Operating junction and - 55 150 ˚C

storage temperature range

AVALANCHE ENERGY LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

EAS Non-repetitive avalanche Unclamped inductive load, IAS = 20 A; - 1300 mJ

energy tp = 0.2 ms; Tj prior to avalanche = 25˚C;

VDD ≤ 50 V; RGS = 50 Ω; VGS = 10 V

EAR Repetitive avalanche energy1 IAR = 20 A; tp = 2.5 µs; Tj prior to - 32 mJ

avalanche = 25˚C; RGS = 50 Ω; VGS = 10 V

IAS, IAR Repetitive and non-repetitive - 20 A

avalanche current

1 pulse width and repetition rate limited by Tj max.

September 1999 1 Rev 1.000

Philips Semiconductors Product specification

PowerMOS transistors IRFP460

Avalanche energy rated

THERMAL RESISTANCES

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Rth j-mb Thermal resistance junction - - 0.5 K/W

to mounting base

Rth j-a Thermal resistance junction SOT429 package, in free air - 45 - K/W

to ambient

ELECTRICAL CHARACTERISTICS

Tj = 25 ˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V(BR)DSS Drain-source breakdown VGS = 0 V; ID = 0.25 mA 500 - - V

voltage

∆V(BR)DSS / Drain-source breakdown VDS = VGS; ID = 0.25 mA - 0.1 - %/K

∆Tj voltage temperature

coefficient

RDS(ON) Drain-source on resistance VGS = 10 V; ID = 10 A - 0.2 0.27 Ω

VGS(TO) Gate threshold voltage VDS = VGS; ID = 0.25 mA 2.0 3.0 4.0 V

gfs Forward transconductance VDS = 30 V; ID = 10 A 13 18 - S

IDSS Drain-source leakage current

VDS = 500 V; VGS = 0 V - 2 50 µA

VDS = 400 V; VGS = 0 V; Tj = 125 ˚C - 100 1000 µA

IGSS Gate-source leakage current VGS = ±30 V; VDS = 0 V - 10 200 nA

Qg(tot) Total gate charge ID = 20 A; VDD = 400 V; VGS = 10 V - 147 190 nC

Qgs Gate-source charge - 12 18 nC

Qgd Gate-drain (Miller) charge - 78 100 nC

td(on) Turn-on delay time VDD = 250 V; RD = 12 Ω; - 23 - ns

tr Turn-on rise time RG = 3.9 Ω - 72 - ns

td(off) Turn-off delay time - 150 - ns

tf Turn-off fall time - 75 - ns

Ld Internal drain inductance Measured from tab to centre of die - 3.5 - nH

Ld Internal drain inductance Measured from drain lead to centre of die - 4.5 - nH

Ls Internal source inductance Measured from source lead to source - 7.5 - nH

bond pad

Ciss Input capacitance VGS = 0 V; VDS = 25 V; f = 1 MHz - 3000 - pF

Coss Output capacitance - 480 - pF

Crss Feedback capacitance - 270 - pF

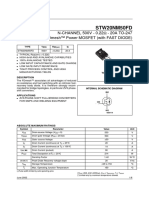

SOURCE-DRAIN DIODE RATINGS AND CHARACTERISTICS

Tj = 25 ˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

IS Continuous source current Tmb = 25˚C - - 20 A

(body diode)

ISM Pulsed source current (body Tmb = 25˚C - - 80 A

diode)

VSD Diode forward voltage IS = 20 A; VGS = 0 V - - 1.5 V

trr Reverse recovery time IS = 20 A; VGS = 0 V; dI/dt = 100 A/µs - 900 - ns

Qrr Reverse recovery charge - 15 - µC

September 1999 2 Rev 1.000

Philips Semiconductors Product specification

PowerMOS transistors IRFP460

Avalanche energy rated

PD% Normalised Power Derating

120

110 Zth j-mb (K/W) PHW20N50E

1

100 D = 0.5

90

80 0.2

0.1 0.1

70

60 0.05

50 0.02 P

D D = tp/T

tp

40 0.01

30

single pulse

20 T

10 0.001

0 1E-06 1E-05 1E-04 1E-03 1E-02 1E-01 1E+00 1E+01

0 20 40 60 80 100 120 140

Pulse width, tp (s)

Tmb / C

Fig.1. Normalised power dissipation. Fig.4. Transient thermal impedance.

PD% = 100⋅PD/PD 25 ˚C = f(Tmb) Zth j-mb = f(t); parameter D = tp/T

ID% Normalised Current Derating

120

110 Drain Current, ID (A) PHW20N50E

20

100 Tj = 25 C VGS = 10 V

18

90

16 8V

80

14

70

12 5V

60

10 4.8 V

50

8

40 4.6 V

6

30 4.4 V

4 4.2 V

20

2 4V

10

0

0

0 20 40 60 80 100 120 140 0 1 2 3 4 5

Tmb / C Drain-Source Voltage, VDS (V)

Fig.2. Normalised continuous drain current. Fig.5. Typical output characteristics.

ID% = 100⋅ID/ID 25 ˚C = f(Tmb); conditions: VGS ≥ 10 V ID = f(VDS); parameter VGS

Drain-Source On Resistance, RDS(on) (Ohms) PHW20N50E

Peak Pulsed Drain Current, IDM (A) PHW20N50E 0.5

100 4V 4.2V 4.6 V Tj = 25 C

tp = 10 us 4.4 V 4.8V 5V

0.45

100us 0.4

10

1 ms 0.35

RDS(on) = VDS/ ID

10 ms

d.c. 0.3

1 100 ms VGS = 6 V

0.25 10V

0.1 0.2

10 100 1000 0 2 4 6 8 10 12 14 16 18 20

Drain-Source Voltage, VDS (V) Drain Current, ID (A)

Fig.3. Safe operating area. Tmb = 25 ˚C Fig.6. Typical on-state resistance.

ID & IDM = f(VDS); IDM single pulse; parameter tp RDS(ON) = f(ID); parameter VGS

September 1999 3 Rev 1.000

Philips Semiconductors Product specification

PowerMOS transistors IRFP460

Avalanche energy rated

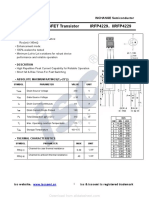

VGS(TO) / V

Drain current, ID (A) PHW20N50E

30 max.

VDS > ID X RDS(ON) 4

25

typ.

20 3

15 min.

150 C 2

Tj = 25 C

10

5 1

0

0 1 2 3 4 5 6 7 8 0

-60 -40 -20 0 20 40 60 80 100 120 140

Gate-source voltage, VGS (V)

Tj / C

Fig.7. Typical transfer characteristics. Fig.10. Gate threshold voltage.

ID = f(VGS); parameter Tj VGS(TO) = f(Tj); conditions: ID = 0.25 mA; VDS = VGS

ID / A SUB-THRESHOLD CONDUCTION

PHW20N50E 1E-01

Transconductance, gfs (S)

20

18 VDS > ID X RDS(ON)

Tj = 25 C 1E-02

16

14 150 C

2% typ 98 %

12 1E-03

10

8 1E-04

6

4

1E-05

2

0

0 5 10 15 20 25 30 1E-06

0 1 2 3 4

Drain current, ID (A)

VGS / V

Fig.8. Typical transconductance. Fig.11. Sub-threshold drain current.

gfs = f(ID); parameter Tj ID = f(VGS); conditions: Tj = 25 ˚C; VDS = VGS

a Normalised RDS(ON) = f(Tj)

Capacitances, Ciss, Coss, Crss (pF) PHW20N50E

10000

2

Ciss

1000

1

Coss

Crss

0 100

-60 -40 -20 0 20 40 60 80 100 120 140 0.1 1 10 100

Tj / C Drain-Source Voltage, VDS (V)

Fig.9. Normalised drain-source on-state resistance. Fig.12. Typical capacitances, Ciss, Coss, Crss.

a = RDS(ON)/RDS(ON)25 ˚C = f(Tj); ID = 10 A; VGS = 10 V C = f(VDS); conditions: VGS = 0 V; f = 1 MHz

September 1999 4 Rev 1.000

Philips Semiconductors Product specification

PowerMOS transistors IRFP460

Avalanche energy rated

Source-Drain Diode Current, IF (A) PHW20N50E

Gate-source voltage, VGS (V) PHW20N50E 50

15 VGS = 0 V

45

14 ID = 20A

13 40

12 Tj = 25 C 300V

11 35

10 30

9 200V

8 25

7 VDD = 400 V 150 C Tj = 25 C

6 20

5 15

4

3 10

2 5

1

0 0

0 25 50 75 100 125 150 175 200 0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 1.1 1.2 1.3 1.4 1.5

Gate charge, QG (nC) Drain-Source Voltage, VSDS (V)

Fig.13. Typical turn-on gate-charge characteristics. Fig.16. Source-Drain diode characteristic.

VGS = f(QG); parameter VDS IF = f(VSDS); parameter Tj

Switching times, td(on), tr, td(off), tf (ns) PHW20N50E Non-repetitive Avalanche current, IAS (A)

600 100

td(off)

500

Tj prior to avalanche = 25 C

400

300 10

tr, tf 125 C

VDS

200

tp

100 td(on) ID

PHW20N50E

0 1

0 5 10 15 20 25 30 1E-06 1E-05 1E-04 1E-03 1E-02

Gate resistance, RG (Ohms) Avalanche time, tp (s)

Fig.14. Typical switching times; td(on), tr, td(off), tf = f(RG) Fig.17. Maximum permissible non-repetitive

avalanche current (IAS) versus avalanche time (tp);

unclamped inductive load

Normalised Drain-source breakdown voltage

1.15

V(BR)DSS @ Tj

Maximum Repetitive Avalanche Current, IAR (A)

V(BR)DSS @ 25 C 100

1.1

1.05 Tj prior to avalanche = 25 C

10

1 125 C

0.95 1

0.9 PHW20N50E

0.1

0.85 1E-06 1E-05 1E-04 1E-03 1E-02

-100 -50 0 50 100 150

Tj, Junction temperature (C)

Avalanche time, tp (s)

Fig.15. Normalised drain-source breakdown voltage; Fig.18. Maximum permissible repetitive avalanche

V(BR)DSS/V(BR)DSS 25 ˚C = f(Tj) current (IAR) versus avalanche time (tp)

September 1999 5 Rev 1.000

Philips Semiconductors Product specification

PowerMOS transistors IRFP460

Avalanche energy rated

MECHANICAL DATA

Plastic single-ended through-hole package; heatsink mounted; 1 mounting hole; 3-lead TO-247 SOT429

E A

P A1

β

q

S

L1(1)

Q

b2

L

1 2 3

b w M c

b1

e e

0 10 20 mm

scale

DIMENSIONS (mm are the original dimensions)

(1)

UNIT A A1 b b1 b2 c D E e L L1 P Q q R S w Y α β

mm 5.3 1.9 1.2 2.2 3.2 0.9 21 16 16 4.0 3.7 2.6 3.5 7.5 15.7 6° 17°

5.45 5.3 0.4

4.7 1.7 0.9 1.8 2.8 0.6 20 15 15 3.6 3.3 2.4 3.3 7.1 15.3 4° 13°

Note

1. Tinning of terminals are uncontrolled within zone L1.

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC EIAJ PROJECTION

98-04-07

SOT429 TO-247

99-08-04

Fig.19. SOT429; pin 2 connected to mounting base

Notes

1. Observe the general handling precautions for electrostatic-discharge sensitive devices (ESDs) to prevent

damage to MOS gate oxide.

2. Refer to mounting instructions for SOT429 envelope.

3. Epoxy meets UL94 V0 at 1/8".

September 1999 6 Rev 1.000

Philips Semiconductors Product specification

PowerMOS transistors IRFP460

Avalanche energy rated

DEFINITIONS

Data sheet status

Objective specification This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification This data sheet contains final product specifications.

Limiting values

Limiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one

or more of the limiting values may cause permanent damage to the device. These are stress ratings only and

operation of the device at these or at any other conditions above those given in the Characteristics sections of

this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

Philips Electronics N.V. 1999

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the

copyright owner.

The information presented in this document does not form part of any quotation or contract, it is believed to be

accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any

consequence of its use. Publication thereof does not convey nor imply any license under patent or other

industrial or intellectual property rights.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices or systems where malfunction of these

products can be reasonably expected to result in personal injury. Philips customers using or selling these products

for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting

from such improper use or sale.

September 1999 7 Rev 1.000

You might also like

- Powermos Transistor Irf730 Avalanche Energy Rated: Features Symbol Quick Reference DataDocument7 pagesPowermos Transistor Irf730 Avalanche Energy Rated: Features Symbol Quick Reference DataCarlos Morales AvilaNo ratings yet

- N-Channel Trenchmos Transistor Psmn040-200W: Features Symbol Quick Reference DataDocument7 pagesN-Channel Trenchmos Transistor Psmn040-200W: Features Symbol Quick Reference DataRobert sibueaNo ratings yet

- N-Channel Trenchmos Transistor Phx9Nq20T, Phf9Nq20T: Features Symbol Quick Reference DataDocument10 pagesN-Channel Trenchmos Transistor Phx9Nq20T, Phf9Nq20T: Features Symbol Quick Reference DatareparacionesdmaNo ratings yet

- STP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetDocument8 pagesSTP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetCarlos A AvilaNo ratings yet

- N-Channel Enhancement Mode Irfz44N Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz44N Trenchmos Transistor: General Description Quick Reference DataingucvNo ratings yet

- N-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataNixon MaldonadoNo ratings yet

- IRFZ24NDocument8 pagesIRFZ24NarcatusNo ratings yet

- N-Channel Trenchmos Transistor Irf530N: Features Symbol Quick Reference DataDocument7 pagesN-Channel Trenchmos Transistor Irf530N: Features Symbol Quick Reference DataLenin Cadillo GutierrezNo ratings yet

- Buk455 200a PDFDocument8 pagesBuk455 200a PDFCarl Conter OnderNo ratings yet

- IRF840 AdvancedPowerElectronicsDocument4 pagesIRF840 AdvancedPowerElectronicssheikh sheharyarNo ratings yet

- IRF540Document9 pagesIRF540paul mathewNo ratings yet

- RU6199R RuichipsDocument9 pagesRU6199R RuichipsAndres padillaNo ratings yet

- DatasheetDocument3 pagesDatasheetRJ.ReflianoNo ratings yet

- Powermos Transistors Php6N60E, Phb6N60E Avalanche Energy RatedDocument9 pagesPowermos Transistors Php6N60E, Phb6N60E Avalanche Energy RatedEmmanuel ZambranoNo ratings yet

- SSM40N03P: DescriptionDocument6 pagesSSM40N03P: DescriptionspotNo ratings yet

- SMK1060P: Switching Regulator ApplicationsDocument8 pagesSMK1060P: Switching Regulator ApplicationsEdmundo VázquezNo ratings yet

- KIA KIA KIA: 1.descriptionDocument5 pagesKIA KIA KIA: 1.descriptionzakreaNo ratings yet

- K2611 K2611 K2611 K2611: FeaturesDocument7 pagesK2611 K2611 K2611 K2611: Featureskaung kyel zin aung zaw moeNo ratings yet

- K2611 K2611 K2611 K2611: FeaturesDocument7 pagesK2611 K2611 K2611 K2611: FeaturesAndrew BanezNo ratings yet

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharNo ratings yet

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFRubenNo ratings yet

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectNo ratings yet

- Irf 540Document8 pagesIrf 540Tom TweedleNo ratings yet

- Powermos Transistor Buk475-200A/B Isolated Version of Buk455-200A/BDocument7 pagesPowermos Transistor Buk475-200A/B Isolated Version of Buk455-200A/Bmaykel valdezNo ratings yet

- Stw20Nm50Fd: N-Channel 500V - 0.22 - 20A To-247 Fdmesh™ Power Mosfet (With Fast Diode)Document8 pagesStw20Nm50Fd: N-Channel 500V - 0.22 - 20A To-247 Fdmesh™ Power Mosfet (With Fast Diode)Alassane Djido SowNo ratings yet

- Advanced Power Electronics Corp.: AP0403GHDocument5 pagesAdvanced Power Electronics Corp.: AP0403GHIulius CezarNo ratings yet

- Advanced Power Electronics Corp.: AP2761I-ADocument4 pagesAdvanced Power Electronics Corp.: AP2761I-AAbelito JesusNo ratings yet

- Buz84 PDFDocument3 pagesBuz84 PDFmundomusicalmeriaNo ratings yet

- Datasheet RU190N10RDocument11 pagesDatasheet RU190N10Ralberto castañoNo ratings yet

- Advanced Power Electronics Corp.: AP2761I-ADocument4 pagesAdvanced Power Electronics Corp.: AP2761I-AM_YYYYNo ratings yet

- IRF840Document8 pagesIRF840Apc CamNo ratings yet

- Irf840 PDFDocument8 pagesIrf840 PDFAnonymous AssOOhqigNo ratings yet

- 40N03GP - N Channel Pwer MOSFET, 30v 40A, Vgs (TH) 3v, Vgs 20vDocument4 pages40N03GP - N Channel Pwer MOSFET, 30v 40A, Vgs (TH) 3v, Vgs 20vLangllyNo ratings yet

- 70L02GHDocument8 pages70L02GHJtzabalaNo ratings yet

- IRFP450Document8 pagesIRFP450Erick DavidNo ratings yet

- Important Notice: Kind RegardsDocument8 pagesImportant Notice: Kind Regardscarlosjamal95No ratings yet

- Umw 40N06Document6 pagesUmw 40N06Александр МилошевичNo ratings yet

- 09 N 70 IDocument4 pages09 N 70 IIwan YogyaNo ratings yet

- Retro Internet Aesthetic Interface Theme For MarketingDocument5 pagesRetro Internet Aesthetic Interface Theme For MarketingEka Satria NugrahaNo ratings yet

- SLW9N90C: 900V N-Channel MOSFETDocument7 pagesSLW9N90C: 900V N-Channel MOSFETJavier VelasquezNo ratings yet

- Enhancement Mode Power MOSFET: NCE N-ChannelDocument7 pagesEnhancement Mode Power MOSFET: NCE N-ChannelRichard MachadoNo ratings yet

- IRFP4229Document2 pagesIRFP4229Hammer CarabaliNo ratings yet

- Isc N-Channel MOSFET Transistor 2SK3505: FeaturesDocument2 pagesIsc N-Channel MOSFET Transistor 2SK3505: FeaturesFale MensNo ratings yet

- AP9972GSPDocument6 pagesAP9972GSPSantiago DiosdadoNo ratings yet

- NCEP4090GUDocument6 pagesNCEP4090GUMar GaoNo ratings yet

- Smps Mosfet: IRF3515S IRF3515LDocument10 pagesSmps Mosfet: IRF3515S IRF3515LHaris FNo ratings yet

- Datasheet 6Document9 pagesDatasheet 6Ivanor Ipanaque CordovaNo ratings yet

- RU30100R Mosfet: N-Channel Advanced Power MOSFETDocument9 pagesRU30100R Mosfet: N-Channel Advanced Power MOSFEThanif zulfiantoNo ratings yet

- Isc N-Channel MOSFET Transistor STD10NM60N: INCHANGE SemiconductorDocument2 pagesIsc N-Channel MOSFET Transistor STD10NM60N: INCHANGE SemiconductorY. Leonel MolinaNo ratings yet

- Buk555 60a PDFDocument7 pagesBuk555 60a PDFGiraldoCarpioRamosNo ratings yet

- Buk9635-100a 1Document7 pagesBuk9635-100a 1Raul OsoNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsRating: 5 out of 5 stars5/5 (1)

- Syahdam 220523604009 S1 Teknik SipilDocument2 pagesSyahdam 220523604009 S1 Teknik SipilRio CandrapurwitaNo ratings yet

- Quad High Side Switch (Quad 35 Mohm) : Advance InformationDocument48 pagesQuad High Side Switch (Quad 35 Mohm) : Advance InformationRio CandrapurwitaNo ratings yet

- Semiconductor Technical Data: Ordering InformationDocument6 pagesSemiconductor Technical Data: Ordering InformationRio CandrapurwitaNo ratings yet

- M54HCT257 PDFDocument12 pagesM54HCT257 PDFRio CandrapurwitaNo ratings yet

- Semiconductor Technical Data: Ordering InformationDocument6 pagesSemiconductor Technical Data: Ordering InformationRio CandrapurwitaNo ratings yet

- LM324 PDFDocument4 pagesLM324 PDFRio CandrapurwitaNo ratings yet

- HD74LV4066A: Quad. Analog Switches / Quad. MultiplexersDocument17 pagesHD74LV4066A: Quad. Analog Switches / Quad. MultiplexersRio CandrapurwitaNo ratings yet

- MJL4281A (NPN) MJL4302A (PNP) Complementary NPN PNP Silicon Power Bipolar TransistorsDocument6 pagesMJL4281A (NPN) MJL4302A (PNP) Complementary NPN PNP Silicon Power Bipolar TransistorsRio CandrapurwitaNo ratings yet

- Quad Operational Amplifiers LM324: FeaturesDocument4 pagesQuad Operational Amplifiers LM324: FeaturesRio CandrapurwitaNo ratings yet

- Silicon Switching NPN Transistor: 2N2222AC3A, 2N2222AC3B 2N2222AC3CDocument3 pagesSilicon Switching NPN Transistor: 2N2222AC3A, 2N2222AC3B 2N2222AC3CRio CandrapurwitaNo ratings yet

- DatasheetDocument2 pagesDatasheetRio CandrapurwitaNo ratings yet

- Negociando Con China by Henry M Paulson JR 86pdf A - 5a979a721723dd0d543a8606 PDFDocument2 pagesNegociando Con China by Henry M Paulson JR 86pdf A - 5a979a721723dd0d543a8606 PDFRoberto carlos Vinces monteiroNo ratings yet

- Din Rail Mount: Seriesone DR SeriesDocument7 pagesDin Rail Mount: Seriesone DR SeriesMortis BeansNo ratings yet

- AIM-ZSDM - Revised Draft DepEd ME Manual-011419 - v8Document100 pagesAIM-ZSDM - Revised Draft DepEd ME Manual-011419 - v8Andrew GallardoNo ratings yet

- The Medieval ArmorerDocument14 pagesThe Medieval Armorereusebius8806100% (1)

- G11 SLM9 RWS Final 2.Document24 pagesG11 SLM9 RWS Final 2.callajessamhay841No ratings yet

- Technical Analysis 2Document5 pagesTechnical Analysis 2Viral OkNo ratings yet

- Removing Distributor AssemblyDocument2 pagesRemoving Distributor Assemblyzelalem mamoNo ratings yet

- Financial Management - AssignmentDocument18 pagesFinancial Management - AssignmentCarina Ng Ka Ling50% (2)

- Wasim AkramDocument10 pagesWasim AkramtalhasadiqNo ratings yet

- Project Report of Dhanashree Goat FarmDocument56 pagesProject Report of Dhanashree Goat FarmNandan GowdaNo ratings yet

- Vaz 2017Document6 pagesVaz 2017Santhosh H ANo ratings yet

- Ebook PDF Visual C How To Program 6th Edition by Paul J Deitel PDFDocument47 pagesEbook PDF Visual C How To Program 6th Edition by Paul J Deitel PDFmary.ellis361100% (34)

- CatalogDocument29 pagesCatalogsupriNo ratings yet

- EFC 3213 Computing II (Numerical Methods) Group Assignment (15%)Document3 pagesEFC 3213 Computing II (Numerical Methods) Group Assignment (15%)Ani AniyoNo ratings yet

- Ushtrime Seminari PascalDocument13 pagesUshtrime Seminari PascalDesadaNo ratings yet

- CCL ProjectDocument50 pagesCCL ProjectShweta YadavNo ratings yet

- Genesis 30uvDocument42 pagesGenesis 30uvCARLOSNo ratings yet

- Historiographies On The Nature of The Mughal State: Colonialsist HistoriographyDocument3 pagesHistoriographies On The Nature of The Mughal State: Colonialsist Historiographyshah malikNo ratings yet

- Accounting Techniques For Decision MakingDocument24 pagesAccounting Techniques For Decision MakingRima PrajapatiNo ratings yet

- JAS Livestock Grading ProceduresDocument2 pagesJAS Livestock Grading ProceduresChristian Pinedo ReateguiNo ratings yet

- GT27R1A1 Ventilation of Underground Works During ConstructionDocument40 pagesGT27R1A1 Ventilation of Underground Works During Constructionfededa100% (2)

- Meralco Bill 436461660101 02082023Document2 pagesMeralco Bill 436461660101 02082023エスゲラ ミエル エンゼルNo ratings yet

- Brochure - Rigid Renold Page 40Document76 pagesBrochure - Rigid Renold Page 40Carlos Gallardo LagosNo ratings yet

- Oklahoma Name Change Voter Registration ApplicationDocument1 pageOklahoma Name Change Voter Registration ApplicationJustin CraytonNo ratings yet

- TSPG - Engine Tools 2-139 A 2-220 PDFDocument82 pagesTSPG - Engine Tools 2-139 A 2-220 PDFAKshay100% (1)

- KFC, Taco Bell, and Pizza Hut Case StudyDocument3 pagesKFC, Taco Bell, and Pizza Hut Case StudyFarhanAnsariNo ratings yet

- Chavez V PEA and AMARI G.R. No. 133250. July 9, 2002. Facts IssueDocument4 pagesChavez V PEA and AMARI G.R. No. 133250. July 9, 2002. Facts IssueFbarrsNo ratings yet

- Business Opportunities Updated 07 Mac 2022 11amDocument39 pagesBusiness Opportunities Updated 07 Mac 2022 11amazim ireadyNo ratings yet

- 1 - Which Factors Do Provoke Binge Eating An Exploratory Study in Eating Disorder Patients PDFDocument6 pages1 - Which Factors Do Provoke Binge Eating An Exploratory Study in Eating Disorder Patients PDFLaura CasadoNo ratings yet

- Dominos PizzaDocument8 pagesDominos PizzaNoor AzizahNo ratings yet