Professional Documents

Culture Documents

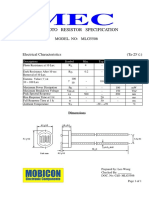

42700di PDF

Uploaded by

Juan CecconiOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

42700di PDF

Uploaded by

Juan CecconiCopyright:

Available Formats

design

Edited by Bill Travis and Anne Watson Swager

ideas

mC visualizes hex code

Abel Raynus, Armatron International, Melrose, MA

n mC systems, information ex- CD4511

I changes usually use the hexa-

decimal 1-2-4-8 format; out-

put data also appear in this format.

Figure 1

A

B

a

b

c

d

R1 TO R4 330

Reading the hex code is not a problem; C

e

MC68HC705J1A

several LEDs connected to the output D

f

lines can display the answer. The prob- A0 g

A1

lem arises when you wish to observe the B0 A2

output data. Many engineers are unfa- HEX B1 A3

TENS UNITS

miliar with hex code and prefer to ob- CODE B2 A4 a

b

serve data in the common decimal for- B3 A5

A

A6 c

mat. If the value of the output data is less B

d

A7

than 10, you can use an ordinary BCD- C

e

D

to-seven-segment decoder to visualize f

the hex code on an LCD or an LED dis- g

play. But what do you do if the value of

the output data is greater than 10? Un-

fortunately, no decoders can transform

hex code into two seven-segment codes. You can visualize hex code in BCD format by using this simple circuit.

Of course, you could configure such a de-

coder using a number of logic gates, but

another simple and inexpensive option is LISTING 1—HEX-TO-BCD CONVERSION

available. The key to this option is using

a low-end mC to transform the hex code

into two BCD codes. In Figure 1, the data

displayed ranges from 0 to 15. Thus, you

need only 4-bit hex code, using four in-

put and eight output mC lines.

Figure 1 uses the approximately $1

Motorola MC68HC705J1A, with 14 I/O

pins. The input lines Pin B0 to Pin B3 re-

mC visualizes hex code ..............................133

Simple circuit times

bathroom fan................................................134

Termination supply tracks

one-half core voltage..................................136

Switch debouncer isolates

input and output..........................................138

Circuit detects reset source........................140

Interface LCD with ease ............................142

www.ednmag.com April 27, 2000 | edn 133

design

ideas

ceive the 4-bit hex code to be displayed. method for an expanded data range, but and then enter the Software Center to

The mC-assembly program in Listing 1, you need more I/O lines, decoders, and download the file for Design Idea #2518.

converts the hex code into two BCD displays. For example, the 8-bit hex code (DI #2518)

codes, which appear on lines Pin A0 to covers the data range 0 to 255, but it

Pin A3 (units) and Pin A4 to Pin A7 needs eight input lines, 12 output lines,

(tens). These outputs drive the two stan- and three decoders and displays. You can

dard BCD-to-seven-segment decoders, download Listing 1 and the “include” file

which, in turn, drive the common-cath- in line 3 from EDN’s Web site, www.ed- To Vote For This Design,

ode LED displays. You can use the same nmag.com. Click on “Search Databases” Circle No. 301

Simple circuit times bathroom fan

Maxwell Strange, Goddard Space Flight Center, Fulton, MD

orget to turn off the ceiling fan in sec, or approximately 17 minutes. At develops a harmless 1.4W. You can easily

F your bathroom? Install the simple

timer in Figure 1. It’s located out-of-

sight in the fan unit, and you turn it on

time-out, Pin 7 goes high, turning off the

relay. For most fans, this relay can be a

small, pc-mountable unit rated at as lit-

adapt this circuit to other applications.

You can change the timing or make it lin-

early adjustable, and you can program

via the wall switch. The circuit costs vir- tle as 0.5A ac load current. These relays the solid-state relay to turn on instead of

tually nothing, using “junk” parts. When typically turn on reliably at 3V. You can off at time-out, by connecting Pin 8 of

ac power appears, a simple rectifier de- use resistor R to drop excess voltage, the timer to Pin 4 instead of Pin 2. You

velops approximately 7V across filter ca- thereby reducing loading on the power can also reverse the action of the solid-

pacitor C. This voltage powers the supply. state relay by reversing the control inputs.

LM2905 analog timer and simultaneous- The p-channel JFET turns on when the (DI #2520)

ly triggers it via trigger-input Pin 1; out- power switches off, rapidly discharging

put Pin 7 then goes low, turning on the CT to allow immediate recycling. The 10-

solid-state relay and fan. Low-leakage ca- kV series resistor makes the circuit in-

pacitor CT and resistor RT set the time de- herently safe; in a worst-case failure, line To Vote For This Design,

lay; for the values shown, the delay is 1000 voltage appears across this resistor and Circle No. 302

120V AC

FROM

Figure 1 FAN WALL

SWITCH

1N3612

4

5 mF

POLYCARBONATE CT C 1N755

'7V DC 100 mF (7.5V)

LM2905 3

+10V

200M RT

8 2N5021

(P-CHANNEL) 10k

2 2W

7 1 5 6

+

LINE

SSR FAN

1 LOAD

R

1.5k (TYPICAL)

Gain control of your bathroom fan by using this simple time-out circuit.

134 edn | April 27, 2000 www.ednmag.com

design

ideas

Termination supply tracks one-half core voltage

Chester Simpson, National Semiconductor, Santa Clara, CA

odern mPs typically require sirable, as the core voltage can vary with- a different control scheme to force the

M core voltages of 2 to 3V. They also

require “termination” voltages

that, for best performance, should equal

out upsetting the termination-voltage set

point. The circuit in Figure 1 is a 6A pow-

er-supply design that generates a termi-

regulated output to track at one-half

VCORE. Resistors R1 and R2 halve the core

voltage, and this voltage serves as the ref-

half the core voltage. The problem is, core nation voltage regulated to 1/2 VCORE. The erence in error amplifier IC1A. The am-

voltages vary among CPUs, and some circuit targets applications in which the plifier compares the one-half VCORE ref-

systems even incorporate variable-core- core voltage is approximately 1.8 to 3.6V. erence with the termination output

voltage supplies that allow systems to ad- An LM2636 synchronous-rectifier con- voltage obtained through R3 and adjusts

just the voltage on the fly, thereby in- troller switching at 300 kHz provides an its output to lock the termination voltage

creasing or reducing CPU operating efficient power converter that operates at one-half VCORE. In this way, the core-

speed to optimize power consumption. A from a 5V input. Because the LM2636 is voltage signal sets the termination volt-

termination-voltage power supply that designed to operate at a fixed output volt- age. IC1B is a unity-gain inverter that cor-

maintains an output of one-half VCORE age (as determined by control bits 14 rects the phase of the feedback signal that

over a range of core voltages is highly de- through 18), the circuit in Figure 1 uses goes to the input of the LM2636’s inter-

Figure 1 5V

10 CR1

N/C 2.2 mF MBR0530T3

MLCC

13 19 5 2

0.1 mF

PWR OUT VCC BOOTV MLCC 2.2 mF

7 (22) + +

GD EN 1000 mF MLCC

I MAX

2.2k CR2 10V

IRF7807 MBRD320 (SEE

20 NOTES)

HS GATE

8 220 4.7 mH TERMINATION

IFB VOLTAGE

LM2636 L1 (32) (ONE-HALF

1 3.9 1500 mF

LS GATE + + + CORE VOLTAGE)

6.3V

0.01 mF (SEE

3 IRF7807 MLCC NOTES)

P GND GND

4 220 pF 51 R3

S GND MLCC 56k

FREQ E/A R5

ADJ VID 0 VID 1 VID 2 VID 3 VID 4 SENSE VREF FB OUT 2k C1 2200 pF R6

12 18 17 16 15 14 6 9 11 10 MLCC 430

10k 4

R4 6

82k 2 10k 7 2 C2

N/C N/C N/C 10k + IC1A

1 5 FROM

IC1B (¼)LM324A 11 + CORE

3

(¼)LM324A 2 1 mF R2 VOLTAGE

MLCC 0.5%

1k

4.99k

(¼)LM324A

10

(¼)LM324A +

8

9 IC1D R1

12 0.1 mF

14 + 2 4.99k

IC1C 13 MLCC 0.5%

0.1 mF

2

MLCC

10k 10k

1% 1%

NOTES:

USE LOW-ESR ALUMINUM ELECTROLYTIC CAPACITOR SUITABLE FOR 300-kHz SWITCHING APPLICATIONS.

UNLESS OTHERWISE SHOWN, RESISTOR TOLERANCES ARE 5%.

MLCC DESIGNATES A CERAMIC CAPACITOR WITH AN X7R OR X5R TEMPERATURE RANGE.

Optimize your CPU’s performance by feeding it a termination voltage that’s exactly half the core voltage.

136 edn | April 27, 2000 www.ednmag.com

design

ideas

nal error amplifier. R4 sets the gain of the put of the LM2636, which would nor- scheme prevents the LM2636’s internal

internal amplifier to unity. R5 forces a soft mally sense the regulated output voltage. error-detection circuitry from shutting

start on turn-on and also eliminates Because the termination output voltage down the part in response to an under-

overshoot. IC1C amplifies the 1.23V in- must be variable (to track the core volt- voltage or overvoltage condition. R3, R6,

ternal reference to approximately 2.5V, age), a fixed 2.5V goes to the sense pin, C1, and C2 provide loop compensation.

which sets the operating point for the er- and the control pins 16 and 18 are (DI #2517)

ror amplifier, IC1A. grounded. These connections program To Vote For This Design,

The 2.5V also connects to the sense in- the internal DAC for a 2.5V output. This Circle No. 303

Switch debouncer isolates input and output

Phill Leyva, Maxim Integrated Products, Sunnyvale, CA

odern programmable-logic con- but this technique increases the pro- IC1’s optotransistor (an emitter follower)

M trollers (PLCs) for automated

process-control systems have ei-

ther 16 or 32 inputs and accept ac volt-

gram-scan time and ties up valuable

timers. The solid-state, electrically isolat-

ed circuit in Figure 1 debounces single

is off.

The two LEDs in IC1, which illuminate

the phototransistor on alternate half cy-

ages of 24 to 120V. A single circuit (a re- inputs without slowing the PLC module. cles of the ac-input current, rectify this

lay for isolation and an RC network with Optoisolators IC1 and IC2 provide elec- current. Most optoisolator applications

a Schmitt trigger to debounce signals to trical isolation for the ac sources at the in- set the current-transfer ratio (CTR) to

the processor) can debounce all the PLC put and output. IC3 is a CMOS switch de- more than 10 to ensure an accurate re-

signals in sequence. However, this ap- bouncer whose output (a 4V logic high) production of the input signal. The cir-

proach slows real-time data processing. appears following a fixed 40-msec delay. cuit in Figure 1, however, sets the CTR

Such debounce circuits also produce de- A 63-kV pullup resistor, connected in- to less than 1, which ensures that the

lay times that change with relay wear and ternally between IN and VCC, forms a emitter follower does not turn off as the

capacitor aging. In the PLC program, you voltage divider with R1. R1’s value ensures ac current goes to zero twice in each cy-

can use a debounce timer for each input, a logic low of less than 0.8V at IN when cle. R2 biases the emitter follower such

Figure 1 IC1 IC3

R2 5V 5V

TLP626 MAX681

1.5k

HOT 1 1

GND 4

4 VCC

3 2 IN 3

OUT

24V AC 2

R1

NEUTRAL 10k

5V

IC2

R3 TPL3043 R4

820

33 HOT

NOTES: FOR 120V AC INPUT OR OUTPUT, 1 6

R2=7.5k, 2W;

R4=160;

ALL RESISTORS ARE ¼W. 24V AC

2 5

3 4 RLOAD NEUTRAL

ZC

2N6073B

2N7000

This debouncer circuit allows an isolated ac voltage to control a separately isolated ac source.

138 edn | April 27, 2000 www.ednmag.com

design

ideas

that IC3’s IN signal remains greater than

the high level, 2.4V, during these

Figure 2

zero crossings. This action elimi-

nates the capacitor normally found in de-

bouncing circuits. IC3’s OUT pin drives

the n-channel MOSFET, and R3’s value is

such that the resulting current flow (in

the MOSFET and LED) is approximate-

ly 5 mA. When the MOSFET turns on,

the LED activates IC2’s zero-crossing tri-

ac driver. Thus, when the power triac

turns on, an ac source connected to the

output drives RLOAD with as much as 4A

(Figure 2). Turning on the triac at zero

crossings eliminates EMI and reduces the

turn-on stress in the triac. R4 limits cur-

rent into the triac driver (IC2) to 1A. Each

source can be either 24V ac (as shown)

or 120V ac. (DI #2521)

To Vote For This Design, An ac switch (top trace) turns on and then briefly bounces off; the output of the associated

Circle No. 304 debouncer circuit turns on cleanly (bottom trace).

Circuit detects reset source

Shyam Tiwari, Sensors Technology Pvt Ltd, Gwalior, India

mbedded single-board computers most cases, CPUs start from the starting source of a reset. It stores in an 8-bit latch

E do not rely only on power-on resets;

they often use multiple sources to re-

set CPUs to prevent CPUs from being

points of memories to fetch their first

code, because they have no way of know-

ing what generated the reset. The circuit

reset-control input data that the CPU can

read. If an input frequently resets the

CPU, the CPU can then report the error

locked into endless loops. However, in in Figure 1 allows a CPU to know the source to the user, using LEDs or other

indicators. In the circuit of Figure 1, an

experiment combined eight independent

Figure 1 EXTERNAL reset-signal sources into a wired-OR sin-

RESET INPUTS

RESET 0

2 D0 Q0

19 gle output. The 74HCT574 stores the 8-

RESET 1

3 D1 Q1

18 bit reset data at the rising edge of the sig-

RESET 2

4 D2 Q2

17 nal. The latch records no other signal if

5 D3 16 the signal appears after the rising edge of

RESET 3 Q3

15 TO CPU

ALL DIODES RESET 4

6 D4 Q4 DATA the first signal. If the CPU finds data that

ARE 1N914B 14

RESET 5 7 D5 Q5 BUS resembles a reset signal in the latch that

8 D6 13

RESET 6 Q6 the signal does not reset, then the reset

9 D7 12

RESET 7 Q7 pulse is too narrow to effect a reset. The

11

RESET CPU recognizes this signal after reading

1

OC

the information from the latch. The out-

74HCT574 put of the latch is a tristate structure; the

IC1

READ CPU reads the output using active chip-

CHIP ENABLE

enable and read-input signals. (DI #2516)

74HCT32

IC2

To Vote For This Design,

This circuit detects the source of a CPU-reset signal. Circle No. 305

140 edn | April 27, 2000 www.ednmag.com

design

ideas

Interface LCD with ease

Bharat Mehta, Space Applications Center, Ahmedabad, India

lphanumeric LCDs find use in bus-oriented interfacing structure, which to the LCD and then read from it. In these

A various embedded systems. In these

systems, mCs often lack I/O re-

sources, so you must make optimum use

consumes 11 I/O lines (eight data lines

and three control lines). You cannot al-

ways afford to spare this many I/O lines.

situations, you can omit one control pin

(of three) for reading data and save one

additional I/O-port pin. The circuit in

of the available resources. LCDs have a Most applications need to write the data Figure 1 saves I/O pins. It uses an 8051

VCC

Figure 1 VCC

1 16 15

4 Q0 D0 7

40

P1.0 DATA 5 Q1 D0 8

6 Q2 D0 9

P1.1 CLK

7 Q3 D0 10

14 Q4 D0 11 LCD

8051 IC1 MODULE

13 Q5 D0 12 VCC

CONTROLLER 74HCT4094

12 Q6 D0 13

2

P1.2 RS 11 Q7 D0 14

5

P1.3 E 8 RS

E 1

20

Save mC I/O pins by effecting a serial-to-parallel conversion with a shift register.

VCC VCC

Figure 2 40 16

2

3

P1.0 DATA 1

6

P1.1 CLK 3

8051 9 CONNECT AT

CONTROLLER P1.2 RS 9 IC1 10 REMOTE LOCATION

P1.3 E 15 26LS31 TO IC2 PINS

11

14

20

13

12

8

VCC

VCC

16 14 1 15

1 4 Q0 D0 7

3 DATA 2 D0 8

2 5 Q1

5 CLK 3

7 6 Q2 D0 9

6 7 Q3 D0 10 LCD

CONNECTION IC2 11 RS IC3 14 Q4 D0 11 VCC

9 MODULE

FROM IC1 PINS 26LS32

10 74HCT4094 13 Q5 D0 12

13 E 2

15 12 Q6 D0 13

8 5

14 11 Q7 D0 14

12 8 RS 1

E

Extend Figure 1’s scheme to long distances by using line-driver and -receiver ICs.

142 edn | April 27, 2000 www.ednmag.com

design

ideas

mC, and only four I/O pins (P1.0 to P1.3) transformation and displays the result on through a differential line receiver such

drive the LCD, instead of the 11 pins oth- the LCD (Listing 1). The same design can as the 26LS32 (IC2). The output of IC2

er displays require. Data transfers in a se- drive various types of alphanumeric drives IC3, which drives the LCD as in

rial mode through the P1.0 port of the LCDs—for example, single-line-to-mul- Figure 1.

mC. The mC interfaces to Pin 2 of IC1, a tiline types, with different character Listing 1, written in 8051 assembly

74HCT4094 8-bit shift register. Serial lengths on each line. You can configure code, provides the sample text “Hello,

data advances on every clock pulse and the circuit to send data over a long dis- EDN Reader” on a single-line, 16-char-

transfers to the shift register. The regis- tance for remote LCD readouts (Figure acter LCD. You can download Listing 1

ter converts the serial data to parallel 2). You can transmit serial data through from EDN’s Web site, www.ednmag.com.

data, available on the output pins Q0 to a differential line-driver IC such as the Click on “Search Databases” and then en-

Q7. The P1.1 port of the mC provides the 26LS31 (IC1). You can feed the output of ter the Software Center to download the

clock. IC1 to either twisted-pair wires or a par- file for Design Idea #2519. (DI #2519)

The data bus, D0 to D7, of the LCD allel pair of wires for transmission to a re-

module connects to the shift register’s mote location. At the other end of the re- To Vote For This Design,

outputs. Software carries out the data mote location, you can retrieve the data Circle No. 306

LISTING 1—SAMPLE DATA DISPLAY

144 edn | April 27, 2000 www.ednmag.com

design

ideas

Design Idea Entry Blank

Entry blank must accompany all entries. $100 Cash Award for all

published Design Ideas. An additional $100 Cash Award for the

winning design of each issue, determined by vote of readers.

Additional $1500 Cash Award for annual Grand Prize Design,

selected among biweekly winners by vote of editors.

To: Design Ideas Editor, EDN Magazine

275 Washington St, Newton, MA 02458

I hereby submit my Design Ideas entry.

Name

Title

Phone

E-mail Fax

Company

Address

Country ZIP

Design Idea Title

Social Security Number

(US authors only)

Entry blank must accompany all entries. (A separate entry

blank for each author must accompany every entry.) Design

entered must be submitted exclusively to EDN, must not be

patented, and must have no patent pending. Design must

be original with author(s), must not have been previously

published (limited-distribution house organs excepted), and

must have been constructed and tested. Fully annotate all

circuit diagrams. Please submit text and listings by e-mail

to b.travis@cahners.com or send a disk.

Exclusive publishing rights remain with Cahners

Publishing Co unless entry is returned to author, or editor

gives written permission for publication elsewhere.

In submitting my entry, I agree to abide by the rules of the

Design Ideas Program.

Signed

Date

Your vote determines this issue’s winner. Vote now, by

circling the appropriate number on the reader inquiry card.

Circle 5 or visit www.ednmag.com/infoaccess.asp

146 edn | April 27, 2000 www.ednmag.com

You might also like

- Facet Electronics Training System 91000-00: Labvolt SeriesDocument49 pagesFacet Electronics Training System 91000-00: Labvolt SeriesBlue Pnt100% (1)

- Logic Circuits and Switching Theory (Laboratory Manual)Document103 pagesLogic Circuits and Switching Theory (Laboratory Manual)Faye Yturralde50% (2)

- 7 Segment Display IntroductionDocument2 pages7 Segment Display IntroductionMrmouzinho100% (1)

- Lec07 DS 2018Document76 pagesLec07 DS 2018Hưng PhạmNo ratings yet

- 7 Segment LED CounterDocument7 pages7 Segment LED CounterOPie UPieNo ratings yet

- 2 Seven Segment Decoder PDFDocument9 pages2 Seven Segment Decoder PDFNisal Nuwan SenarathnaNo ratings yet

- Design and build gray code and BCD convertersDocument3 pagesDesign and build gray code and BCD convertersmarkjesterNo ratings yet

- Seven Segment DisplayDocument13 pagesSeven Segment DisplayJapjeet KaurNo ratings yet

- Ecgr2156 Experiment 3 Seven Segment DecoderDocument6 pagesEcgr2156 Experiment 3 Seven Segment Decoderm shahNo ratings yet

- Logic Circuits I Study Guide For Ch6-7Document23 pagesLogic Circuits I Study Guide For Ch6-7Alexandre Guerreiro100% (1)

- Avionics - Decoders & EncodersDocument5 pagesAvionics - Decoders & EncoderskrishnamurthyVishNo ratings yet

- BCD To 7 Segment LED Display Decoder Circuit Diagram and WorkingDocument19 pagesBCD To 7 Segment LED Display Decoder Circuit Diagram and WorkingAashish KumarNo ratings yet

- Lab 3Document4 pagesLab 3Inderraj Singh GrewalNo ratings yet

- BCD to 7-Segment Decoder Converts NumbersDocument7 pagesBCD to 7-Segment Decoder Converts NumbersBOMMA SRI MUKHINo ratings yet

- Counters, Oscillators, and Digital DisplaysDocument5 pagesCounters, Oscillators, and Digital DisplaysmhofuNo ratings yet

- BCD-to-7-Segment Decoder AnalysisDocument6 pagesBCD-to-7-Segment Decoder AnalysisPrathamesh PatilNo ratings yet

- BCD To 7 Segment LED Display Decoder CircuitDocument6 pagesBCD To 7 Segment LED Display Decoder CircuitMarx Lennin CabalticanNo ratings yet

- Laboratory Exercise 2: Numbers and DisplaysDocument5 pagesLaboratory Exercise 2: Numbers and DisplaysTuân PhạmNo ratings yet

- Digital To Analog Converters NotesDocument12 pagesDigital To Analog Converters Noteszoluska xyzNo ratings yet

- Lab2 VerilogDocument5 pagesLab2 Verilogar_g_usNo ratings yet

- BCD To 7 Segment Display PDFDocument18 pagesBCD To 7 Segment Display PDFRobertoRodríguezNo ratings yet

- Analysis of Functions of BCD To 7 Segment DecoderDocument5 pagesAnalysis of Functions of BCD To 7 Segment Decodercoker yusufNo ratings yet

- Electronic CEP ReportDocument8 pagesElectronic CEP ReportSaad AliKhanNo ratings yet

- 7-Segment Display DecoderDocument4 pages7-Segment Display DecoderYogesh KhatriNo ratings yet

- Learning Objectives:: Topic 2.2.3 - BCD Counter Topic 2.2.4 - Decade CounterDocument35 pagesLearning Objectives:: Topic 2.2.3 - BCD Counter Topic 2.2.4 - Decade CountersuriantoNo ratings yet

- Lab2 VHDLDocument4 pagesLab2 VHDLMayank AgarwalNo ratings yet

- 7 Segment DisplayDocument6 pages7 Segment DisplayTwesigomwe Gilbert GabrielNo ratings yet

- ECEN 1400 Lecture 11 Seven Segment DisplayDocument10 pagesECEN 1400 Lecture 11 Seven Segment DisplayRounit RaiNo ratings yet

- Modifications: Before Modification After Modification Set - Tris - B (0x7F) Pin - b7Document7 pagesModifications: Before Modification After Modification Set - Tris - B (0x7F) Pin - b7Ammar AlkindyNo ratings yet

- Laboratory Exercise 2: Numbers and DisplaysDocument4 pagesLaboratory Exercise 2: Numbers and DisplaysVu Hung CuongNo ratings yet

- Lab 1: Binary Numbers and Logic GatesDocument4 pagesLab 1: Binary Numbers and Logic GatesFatmir KelmendiNo ratings yet

- Microcontroller Bootcamp (4) : User InterfacesDocument8 pagesMicrocontroller Bootcamp (4) : User InterfacesMikko FagerlundNo ratings yet

- Seven Segment Display Document PDFDocument16 pagesSeven Segment Display Document PDFRekha MudalagiriNo ratings yet

- lcd1 PDFDocument6 pageslcd1 PDFddvp_gunawardana100% (1)

- PTI Section 9 Analog DigitalDocument14 pagesPTI Section 9 Analog Digitalchrist9088No ratings yet

- Assignment On Seven Segment Display: Ms. Gagandeep Kaur Saurabh Prabhakar Roll No. 100905067 B.Tech 3rd Year Eic 4Document10 pagesAssignment On Seven Segment Display: Ms. Gagandeep Kaur Saurabh Prabhakar Roll No. 100905067 B.Tech 3rd Year Eic 4Saurabh PrabhakarNo ratings yet

- Presentation Ch. 2Document63 pagesPresentation Ch. 2Hassan El-MansyNo ratings yet

- Chapter 5Document59 pagesChapter 5Humna DubbiiNo ratings yet

- Principles & Applications: Digital ElectronicsDocument20 pagesPrinciples & Applications: Digital ElectronicsAnmar AhmedNo ratings yet

- Lab2 EquipmentIntroDocument5 pagesLab2 EquipmentIntroHaSanTaRiqNo ratings yet

- Convert BCD to 7-segment displayDocument10 pagesConvert BCD to 7-segment displayM Salman RyanNo ratings yet

- Nagindas Khandwala College of Commerce, Arts & Management Studies & Shantaben Nagindas Khandwala College of Science Malad (W), Mumbai - 64Document35 pagesNagindas Khandwala College of Commerce, Arts & Management Studies & Shantaben Nagindas Khandwala College of Science Malad (W), Mumbai - 64127fyitvanshnagdaNo ratings yet

- 08.402 Digital Electronics and Logic Design (E)Document1 page08.402 Digital Electronics and Logic Design (E)anupvasuNo ratings yet

- Interfacing 16×2 LCD With 8051Document39 pagesInterfacing 16×2 LCD With 8051gunda manasaNo ratings yet

- BCD To Seven Segment Decoder PresentationDocument12 pagesBCD To Seven Segment Decoder PresentationIoT Library100% (1)

- A Digital Background Technique For Pipelined Analog-to-Digital ConvertersDocument5 pagesA Digital Background Technique For Pipelined Analog-to-Digital ConverterskennyNo ratings yet

- Implementing a 7-Segment DisplayDocument3 pagesImplementing a 7-Segment DisplayDeepam AsnaniNo ratings yet

- Hardware Project1Document14 pagesHardware Project1Meynard SamsonNo ratings yet

- Lab No 07 - Logic DesignDocument10 pagesLab No 07 - Logic DesignIDK 2No ratings yet

- High Resolution 12 Bit Segmented Capacitor DAC in Successive Approximation ADCDocument4 pagesHigh Resolution 12 Bit Segmented Capacitor DAC in Successive Approximation ADCbhasin_hemantNo ratings yet

- B 7 Segment Display DecoderDocument8 pagesB 7 Segment Display Decoderlokesh krapaNo ratings yet

- Lab 5: Digital To Analog and Analog To Digital Converter: Telecommunication Electronics Laboratory Exercise 5Document7 pagesLab 5: Digital To Analog and Analog To Digital Converter: Telecommunication Electronics Laboratory Exercise 5Nilesh BhardwajNo ratings yet

- Experiment-11 BCD Code To 7-Segment Decoder 11-1 ObjectDocument3 pagesExperiment-11 BCD Code To 7-Segment Decoder 11-1 ObjectMohammed Dyhia AliNo ratings yet

- EEE2211 Lab ManualDocument30 pagesEEE2211 Lab ManualMuhammed AslamNo ratings yet

- HCMC UNIVERSITY OF TECHNOLOGY & EDUCATION'S INTERNATIONAL EDUCATION EXCHANGE CENTERDocument12 pagesHCMC UNIVERSITY OF TECHNOLOGY & EDUCATION'S INTERNATIONAL EDUCATION EXCHANGE CENTERTân NguyễnNo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Resultados Totales1Document3 pagesResultados Totales1Juan CecconiNo ratings yet

- Esp32 Wroom Da Datasheet enDocument30 pagesEsp32 Wroom Da Datasheet enJuan CecconiNo ratings yet

- Snoaa 46Document7 pagesSnoaa 46Juan CecconiNo ratings yet

- Resultados Totales1Document3 pagesResultados Totales1Juan CecconiNo ratings yet

- Esp32 Wroom Da Datasheet enDocument30 pagesEsp32 Wroom Da Datasheet enJuan CecconiNo ratings yet

- ESP32 WROOM 32D & ESP32 WROOM 32U: Recommended FOR NEW Designs (NRND)Document31 pagesESP32 WROOM 32D & ESP32 WROOM 32U: Recommended FOR NEW Designs (NRND)Mogasi100% (1)

- PT2399 Echo Processor IC Spec SheetDocument5 pagesPT2399 Echo Processor IC Spec SheetMaulana AdiNo ratings yet

- High-Side Current Sources For Industrial Applications: by Ahmed NoemanDocument7 pagesHigh-Side Current Sources For Industrial Applications: by Ahmed NoemanJuan CecconiNo ratings yet

- Features Descriptio: Lt1932 Constant-Current DC/DC Led Driver in ThinsotDocument16 pagesFeatures Descriptio: Lt1932 Constant-Current DC/DC Led Driver in ThinsotJuan CecconiNo ratings yet

- Attansic L2 AagDocument1 pageAttansic L2 AagJuan CecconiNo ratings yet

- 60V Two Terminal Constant Current Led Driver PowerdiDocument17 pages60V Two Terminal Constant Current Led Driver PowerdiJuan Vicente Hernandez LogytelNo ratings yet

- Attansic L2Document1 pageAttansic L2Juan CecconiNo ratings yet

- MLG5506Document1 pageMLG5506Juan CecconiNo ratings yet

- Edison Opto Datasheet Federal 3535 3W LC Series Cool White - SAPv0.7Document17 pagesEdison Opto Datasheet Federal 3535 3W LC Series Cool White - SAPv0.7Juan CecconiNo ratings yet

- Conducted EMI Issues in A 600-W Single-Phase Boost PFC DesignDocument8 pagesConducted EMI Issues in A 600-W Single-Phase Boost PFC DesignJuan CecconiNo ratings yet

- Invoice 85701386Document4 pagesInvoice 85701386Juan CecconiNo ratings yet

- TSCR420CX6 / TSCR421CX6: Taiwan SemiconductorDocument11 pagesTSCR420CX6 / TSCR421CX6: Taiwan SemiconductorJuan CecconiNo ratings yet

- Hardening Power Supplies To Line Voltage TransientsDocument3 pagesHardening Power Supplies To Line Voltage TransientsJuan CecconiNo ratings yet

- Integrating EMI Filters and Appliance Motor ControlsDocument11 pagesIntegrating EMI Filters and Appliance Motor ControlsJuan CecconiNo ratings yet

- TSCR400CX6 / TSCR402CX6: Taiwan SemiconductorDocument8 pagesTSCR400CX6 / TSCR402CX6: Taiwan SemiconductorJuan CecconiNo ratings yet

- Common Mode Filters Design Guide (2007) (Coilcraft)Document4 pagesCommon Mode Filters Design Guide (2007) (Coilcraft)mapo mfaNo ratings yet

- Applications of Non Zero Crossing Triac Drivers MOC3011Document6 pagesApplications of Non Zero Crossing Triac Drivers MOC3011David ReyesNo ratings yet

- System Design and Layout Techniques For Noise Reduction in MCU-Based SystemsDocument12 pagesSystem Design and Layout Techniques For Noise Reduction in MCU-Based SystemsJuan CecconiNo ratings yet

- TPS560430 Evaluation Module: User's GuideDocument10 pagesTPS560430 Evaluation Module: User's GuideJuan CecconiNo ratings yet

- Qex 1Document9 pagesQex 1Aamir HabibNo ratings yet

- Cascode BJT Amplifier Experiment AnalysisDocument6 pagesCascode BJT Amplifier Experiment AnalysisRajesh NatarajanNo ratings yet

- TransistorsDocument41 pagesTransistorsJacobNo ratings yet

- Zlib - Pub Basic ElectronicsDocument629 pagesZlib - Pub Basic ElectronicsJean GoujonNo ratings yet

- Crown Ma3600vzDocument104 pagesCrown Ma3600vzIleana RuvalcabaNo ratings yet

- GATE 2009 Paper Q1-20Document16 pagesGATE 2009 Paper Q1-20mass1984No ratings yet

- ECE312 Lec03Document46 pagesECE312 Lec03peter brownNo ratings yet

- Lic Ii Ece NotesDocument122 pagesLic Ii Ece NotesJubin JainNo ratings yet

- 5555syllabi Physics 2014Document52 pages5555syllabi Physics 2014Bharath K AjithNo ratings yet

- EEE 231 CoursecontentDocument3 pagesEEE 231 Coursecontentfakiha11No ratings yet

- Cambridge Semiconductor MCQsDocument47 pagesCambridge Semiconductor MCQsSumanta BhattacharyyaNo ratings yet

- EC8311-Electronics Lab ManualDocument108 pagesEC8311-Electronics Lab ManualReena RajNo ratings yet

- Introduction To TransistorsDocument24 pagesIntroduction To TransistorsMan CangkulNo ratings yet

- Ecd LR 2Document6 pagesEcd LR 2Junaid kaleemNo ratings yet

- Shraga Kraus ThesisDocument230 pagesShraga Kraus ThesisThib'No ratings yet

- LICA Lecture Notes by A.mounikaDocument77 pagesLICA Lecture Notes by A.mounikaAnonymous 4u5XkWGONo ratings yet

- ElectronicMechanic (NSQF) 2ndSEMtpDocument179 pagesElectronicMechanic (NSQF) 2ndSEMtpMd SalmanNo ratings yet

- BJT IntroductionDocument4 pagesBJT IntroductionMr KNo ratings yet

- High Voltage IC Amplifier Circuit for AudioDocument3 pagesHigh Voltage IC Amplifier Circuit for Audiojeanpaul CAYTANNo ratings yet

- EC-8453 Linear Integrated Circuits QA BankDocument7 pagesEC-8453 Linear Integrated Circuits QA Banksanthosh sekarNo ratings yet

- Object Oriented Programming (Mechanical Engineering)Document13 pagesObject Oriented Programming (Mechanical Engineering)andhracollegesNo ratings yet

- Bel PapersDocument39 pagesBel PapersAbhijeet SinghNo ratings yet

- Radio and Radar QuestionsDocument98 pagesRadio and Radar QuestionsJohnny MaisonNo ratings yet

- Boylestad - MCQ in Bipolar Junction Transistors - Pinoybix EngineeringDocument22 pagesBoylestad - MCQ in Bipolar Junction Transistors - Pinoybix EngineeringparantnNo ratings yet

- AD636Document16 pagesAD636Cristiano SilvaNo ratings yet

- TRANSISTOR AUDIO AMPLIFIER MANUAL by Clive SinclairDocument44 pagesTRANSISTOR AUDIO AMPLIFIER MANUAL by Clive SinclairJean DUPONDNo ratings yet

- Power Amplifier DistortionDocument18 pagesPower Amplifier DistortionHk SoniNo ratings yet

- A REVIEW ON LDO PASS ELEMENTSDocument5 pagesA REVIEW ON LDO PASS ELEMENTSChristina ReyesNo ratings yet

- Electronic CircuitsDocument18 pagesElectronic CircuitsMythily VedhagiriNo ratings yet

- Unitwise Objective Question With AnswerDocument19 pagesUnitwise Objective Question With AnswerKutty ShivaNo ratings yet