Professional Documents

Culture Documents

2 In-Sem Exam - BEE034A - SET-1 DR Avireni Srinivasulu

Uploaded by

HimanshuOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

2 In-Sem Exam - BEE034A - SET-1 DR Avireni Srinivasulu

Uploaded by

HimanshuCopyright:

Available Formats

Registration No.

SET A

JECRC UNIVERSITY

IInd In-Sem Examination, 21 April 2020

B.Tech. (ECE), VI-Semester

VLSI DESIGN (BEE034A)

Time: 1:30 Hrs. Max Marks: 50

Instructions:

1. Attempt all the questions.

2. Illustrate your answers with suitable examples and diagrams, wherever

necessary.

3. Write relevant question numbers before writing the answer.

Course Outcomes (COs)

CO1: Able to understand and analyze sequential MOS logic circuits.

CO2: Able to understand and analyze design rules, stick diagrams, and layouts.

Q1. Answer the following questions. (10 × 1 M = 10 Marks)

1) [CO1] The only difference between a combinational circuit and a flip-flop is

that _____________ [ ]

2) [CO1] The flip-flop is only activated by _____________

a) Positive edge trigger b) Negative edge trigger

c) Either positive or Negative edge trigger d) Sinusoidal trigger

3) [CO1] In a positive edge triggered JK flip flop, a low J and low K produces?

a) High state b) Low state

c) Toggle state d) No Change State

4) [CO1] Inverters in latch form a feedback loop which is always [ ]

a) negative b) positive c) infinite d) changing

5) [CO1] A shift register is a cascade of ________ [ ]

a) 1-bit memory b) two latches

c) two NAND gates d) none of these

6) [CO2] Which color is used for metal-1 layer? [ ]

a) red b) green c) light blue d) yellow

7) [CO2] When two or more cuts of same type cross or touch each other, that

represents ________________ [ ]

8) [CO2] Gate area can be given as [ ]

a) L/W b) 2L/W

c) L * W d) Π2(L*W)

9) [CO2] What should be the spacing between two wells at different potentials?

a) 4λ b) 6λ

c) 3λ d) 8λ

10) [CO2] When a poly crosses diffusion it represents a transistor. [True/False]

Q2. Answer the following questions. (4 × 2 M = 8 Marks)

1. [CO1] What is sequential circuit?

2. [CO1] What are the applications of T flip flop?

3. [CO2] What are the commonly used conducting layers in IC fabrication?

4. [CO2] The simplified layout of a logic circuit is shown in figure 1. Draw the

corresponding circuit diagram?

A|

B|

F

A

B

Fig. 1

A

Q3. Answer the following questions. (2 × 6 M = 12 Marks)

1. [CO1] Draw a device level circuit diagram of a depletion-load (n-MOS) latch

circuit and explain its operation.

2. [CO2] Draw a stick diagram for a CMOS circuit implementing function

F A( B C ) CD .

Q4. Answer the following questions. (2 × 10 M = 20 Marks)

1. [CO1] Draw a device level circuit diagram of a CMOS SR latch based on

NAND gates and explain its operation.

2. [CO2] Draw the layout for the logic function F ( A B C )( D E ) . Assume

that the circuit is implemented in a 90 nm technology and also choose

necessary data.

*****

You might also like

- 2 In-Sem Exam - BEE034A - SET-1 DR Avireni Srinivasulu PDFDocument2 pages2 In-Sem Exam - BEE034A - SET-1 DR Avireni Srinivasulu PDFHimanshuNo ratings yet

- Phy Science (Em)Document4 pagesPhy Science (Em)WarHead SupremeNo ratings yet

- Bee MST 1Document1 pageBee MST 1PrerakNo ratings yet

- HSBTEDocument2 pagesHSBTEeducationtown24No ratings yet

- Ee10002 Oct Autumn Mid Sas 23Document3 pagesEe10002 Oct Autumn Mid Sas 23mdabdularain655No ratings yet

- Test Solid State Full ChapterDocument4 pagesTest Solid State Full ChapterTr Mazhar PunjabiNo ratings yet

- Ramaiah: Semester End Examinations February - MarchDocument2 pagesRamaiah: Semester End Examinations February - Marchsaikar.challaNo ratings yet

- Acseh0304 (DLD) 2Document5 pagesAcseh0304 (DLD) 2yt608118No ratings yet

- Question PaperDocument41 pagesQuestion PaperShubham DabhadeNo ratings yet

- Half-Yearly Exam (2022-23) 11th ChemistryDocument2 pagesHalf-Yearly Exam (2022-23) 11th Chemistryshaktiparashar2004No ratings yet

- (Template) EPU (6031) FIRST SERIES QPDocument3 pages(Template) EPU (6031) FIRST SERIES QPHead ShotNo ratings yet

- ACSBS0502Document4 pagesACSBS0502Anubhav awasthiNo ratings yet

- (C) and (D) Carrying 8 Marks EachDocument3 pages(C) and (D) Carrying 8 Marks Eachswarnim verma100% (1)

- School of Engineering and Technology: InstructionsDocument2 pagesSchool of Engineering and Technology: InstructionsRittik BhatiNo ratings yet

- M.SC (Chemistry) 2013 - 2014 PatternDocument133 pagesM.SC (Chemistry) 2013 - 2014 Patternrakesh jadhavNo ratings yet

- Signal Paper 3Document3 pagesSignal Paper 3imvuuser1No ratings yet

- A18-AC - (EEE, ECE & ECM) - 25-08-2021 - (Regular)Document1 pageA18-AC - (EEE, ECE & ECM) - 25-08-2021 - (Regular)BATHULA BALAKRISHNANo ratings yet

- SSED - Solved Problems For Chapter 0-1Document3 pagesSSED - Solved Problems For Chapter 0-1MINH NGUYỄN THẾNo ratings yet

- Demp Mid - 1 Question BankDocument3 pagesDemp Mid - 1 Question BankMᴀɴɪ TᴇᴊᴀNo ratings yet

- Signal 2Document2 pagesSignal 2imvuuser1No ratings yet

- CG Paper PUT - SECTION ADocument2 pagesCG Paper PUT - SECTION Akundan kumarNo ratings yet

- QP BSC 29012020 (Oct 2019)Document623 pagesQP BSC 29012020 (Oct 2019)jonnaNo ratings yet

- Test Papers (7th Sem)Document18 pagesTest Papers (7th Sem)shivansh2001mishraNo ratings yet

- Coordination Chemistry PDFDocument4 pagesCoordination Chemistry PDFBudhaditya BanerjeeNo ratings yet

- FM Unitwise Test AllDocument4 pagesFM Unitwise Test Allbodakevivek888No ratings yet

- What Does An Atom Look Like (Draw The Atomic Structure and Label) ?Document3 pagesWhat Does An Atom Look Like (Draw The Atomic Structure and Label) ?Sheda RumNo ratings yet

- Delhi Public School: General InstructionsDocument16 pagesDelhi Public School: General InstructionsAyush jhaNo ratings yet

- LDCA Previous Year PaperDocument4 pagesLDCA Previous Year Paperflipkart6392No ratings yet

- DiplomaDocument2 pagesDiplomaKishore AjayNo ratings yet

- Homework ThreeDocument4 pagesHomework ThreeAnuj JainNo ratings yet

- UC 103T Mid-Sem-3Document3 pagesUC 103T Mid-Sem-3Mehul darakNo ratings yet

- Co-Ordination Compound (Question Paper)Document4 pagesCo-Ordination Compound (Question Paper)Param shahNo ratings yet

- Model Question Paper: Unit - I Questions Marks BLL CODocument2 pagesModel Question Paper: Unit - I Questions Marks BLL COViju JigajinniNo ratings yet

- CH302 Assignments 2020BDocument5 pagesCH302 Assignments 2020BMike VhurinosharaNo ratings yet

- CADA QP-Ktunotes - in PDFDocument3 pagesCADA QP-Ktunotes - in PDFsachinNo ratings yet

- 11th Chemistry Annual 20-21 Set BDocument8 pages11th Chemistry Annual 20-21 Set BKeshav AgarwalNo ratings yet

- I B.Tech. II Semester Regular Examinations October 2021Document10 pagesI B.Tech. II Semester Regular Examinations October 2021AmarnathNo ratings yet

- 2019 Data Structure CS (EE) 402: Time Allotted: 3 Hrs Full Marks: 70Document4 pages2019 Data Structure CS (EE) 402: Time Allotted: 3 Hrs Full Marks: 70DEBJANI CHAKRABORTYNo ratings yet

- CAE 2 - SEEA1103 - Electrical and Electronics EngineeringDocument1 pageCAE 2 - SEEA1103 - Electrical and Electronics EngineeringNarendra ANo ratings yet

- Paper 1Document26 pagesPaper 1Akshay PatwardhanNo ratings yet

- 2024-Mock JEE Main-10 - PaperDocument16 pages2024-Mock JEE Main-10 - PaperAranyaman MohanNo ratings yet

- APR2013P21Document63 pagesAPR2013P21qsashutoshNo ratings yet

- S T L DDocument12 pagesS T L DMohan Krishna0% (1)

- Time: 3.00 Hours) /maximum Marks: 100: This Question Paper Contains 8 Printed PagesDocument8 pagesTime: 3.00 Hours) /maximum Marks: 100: This Question Paper Contains 8 Printed PagesOmpratapNo ratings yet

- Sample Question Paper Digital Techniques PDFDocument5 pagesSample Question Paper Digital Techniques PDFAshutosh PatilNo ratings yet

- DPP 5Document11 pagesDPP 5mstudy1009No ratings yet

- M.sc. - Chemistry April 16Document144 pagesM.sc. - Chemistry April 16Kundan DeoreNo ratings yet

- S.S.C Public Examination: Model Paper-2 General Science Paper - 1Document4 pagesS.S.C Public Examination: Model Paper-2 General Science Paper - 1Dhatri Subasri Navya KNo ratings yet

- C-Chemical Bonding and Mol - StructurexiDocument2 pagesC-Chemical Bonding and Mol - Structurexivsg12umtNo ratings yet

- Surveying & GeomaticsDocument2 pagesSurveying & Geomaticsmanojyadav191985No ratings yet

- Papaer JamDocument12 pagesPapaer JamdeeptiNo ratings yet

- Chemistry Question Paper Feb 2023Document7 pagesChemistry Question Paper Feb 2023bhalchandrachavan2006No ratings yet

- F.Y. B.Arch. (Semester - I) Building Technology and Materials - I (2015 Pattern)Document18 pagesF.Y. B.Arch. (Semester - I) Building Technology and Materials - I (2015 Pattern)Tanaya ChiplunkarNo ratings yet

- Btech It 5 Sem Compiler Design Kit052 2021Document1 pageBtech It 5 Sem Compiler Design Kit052 2021Aanchal SinghNo ratings yet

- A Brief Introduction To The Written TestDocument15 pagesA Brief Introduction To The Written TestMuhammad ZakriyaNo ratings yet

- All Districts Que PprsDocument145 pagesAll Districts Que PprsSfbswfng VsgjtdckNo ratings yet

- LCD Set A PDFDocument2 pagesLCD Set A PDFAsha JohnNo ratings yet

- Microelectronics II: EE 311A, January-May 2021Document2 pagesMicroelectronics II: EE 311A, January-May 2021Amit KumarNo ratings yet

- CHP 7 FullDocument35 pagesCHP 7 FullMahesh Babu SamanapallyNo ratings yet

- Vighnesh Hegde Home Automation Using WiFiDocument1 pageVighnesh Hegde Home Automation Using WiFiHimanshuNo ratings yet

- OGghSZteEemnpBK2VMQaIg - C1 Course Challenge DrawingDocument1 pageOGghSZteEemnpBK2VMQaIg - C1 Course Challenge DrawingHimanshuNo ratings yet

- 35Document3 pages35HimanshuNo ratings yet

- Embeddded System 3rd Sessional April2020 PDFDocument2 pagesEmbeddded System 3rd Sessional April2020 PDFHimanshuNo ratings yet

- Syllabus For Electronics and Communication Engineering (EC) : Linear AlgebraDocument3 pagesSyllabus For Electronics and Communication Engineering (EC) : Linear Algebraapi-273759951No ratings yet

- Window MethodDocument6 pagesWindow MethodHimanshuNo ratings yet

- Sgvu Programs and Fees 2020: School/ Centre Name Program Name Duration Academic Qualification Annual Fee (INR)Document4 pagesSgvu Programs and Fees 2020: School/ Centre Name Program Name Duration Academic Qualification Annual Fee (INR)HimanshuNo ratings yet

- Jecrc University, Jaipur Third in Semester Examination Form Even Semester - 2020Document1 pageJecrc University, Jaipur Third in Semester Examination Form Even Semester - 2020HimanshuNo ratings yet

- Control Systems Assignment QuestionsDocument7 pagesControl Systems Assignment QuestionsHimanshuNo ratings yet

- AcademicsDocument2 pagesAcademicsHimanshuNo ratings yet

- CAT Number System Formulas PDFDocument22 pagesCAT Number System Formulas PDFHimanshuNo ratings yet

- Cyborg 7795Document10 pagesCyborg 7795HimanshuNo ratings yet

- Chapter14 PDFDocument11 pagesChapter14 PDFHimanshuNo ratings yet

- Vlsi Cad:: Logic To LayoutDocument13 pagesVlsi Cad:: Logic To LayoutHimanshuNo ratings yet

- Radar and Satellite Communication Types of Display PDFDocument3 pagesRadar and Satellite Communication Types of Display PDFHimanshuNo ratings yet

- Radar and Satellite Communication Unit1 PDFDocument5 pagesRadar and Satellite Communication Unit1 PDFHimanshuNo ratings yet

- Himanshu IOTEDUDocument3 pagesHimanshu IOTEDUHimanshuNo ratings yet

- Radar and Satellite Communication 28898Document4 pagesRadar and Satellite Communication 28898HimanshuNo ratings yet

- De 2020 1140 1Document4 pagesDe 2020 1140 1HimanshuNo ratings yet

- Toij 2020 03 26 PDFDocument16 pagesToij 2020 03 26 PDFHimanshuNo ratings yet

- Toij 2020 03 25 PDFDocument18 pagesToij 2020 03 25 PDFHimanshuNo ratings yet

- University of Rajasthan Admit Card PDFDocument1 pageUniversity of Rajasthan Admit Card PDFHimanshuNo ratings yet

- How To Use HumidityDocument1 pageHow To Use HumidityHimanshuNo ratings yet

- How To Use HumidityDocument1 pageHow To Use HumidityHimanshuNo ratings yet

- How To Use HumidityDocument1 pageHow To Use HumidityHimanshuNo ratings yet

- Himanshu IOTEDUDocument3 pagesHimanshu IOTEDUHimanshuNo ratings yet

- Radar and Satellite Communication Types of DisplayDocument3 pagesRadar and Satellite Communication Types of DisplayHimanshuNo ratings yet

- 06-Inv Noninv AmpDocument3 pages06-Inv Noninv AmpharshNo ratings yet

- ZerocrossingdetectorDocument1 pageZerocrossingdetectorsandeep_036No ratings yet

- D D D D D D D D: TL5001, TL5001A Pulse-Width-Modulation Control CircuitsDocument32 pagesD D D D D D D D: TL5001, TL5001A Pulse-Width-Modulation Control CircuitsLuisNo ratings yet

- 12 25 Geo EsDocument5 pages12 25 Geo EsIvan VillarrealNo ratings yet

- CD4093BM/CD4093BC Quad 2-Input NAND Schmitt Trigger: General DescriptionDocument6 pagesCD4093BM/CD4093BC Quad 2-Input NAND Schmitt Trigger: General DescriptionCristian MorenoNo ratings yet

- CTCSS Encoder: Features ApplicationsDocument12 pagesCTCSS Encoder: Features ApplicationsBlagoja GjakovskiNo ratings yet

- Opa1632 Used in AMB Laboratories SchematicsDocument35 pagesOpa1632 Used in AMB Laboratories SchematicscosNo ratings yet

- DIC QuestionsDocument2 pagesDIC QuestionsAshish KrNo ratings yet

- OscilatorDocument8 pagesOscilatorericoNo ratings yet

- PWM Pulse Convert To Voltage1Document3 pagesPWM Pulse Convert To Voltage1Benjamin HouseNo ratings yet

- UMN EE2301 Final ExamDocument10 pagesUMN EE2301 Final ExamchrisNo ratings yet

- Analysis of Energy Efficient PTL Based Full Adders Using Different Nanometer TechnologiesDocument6 pagesAnalysis of Energy Efficient PTL Based Full Adders Using Different Nanometer TechnologiesDwarakaManeekantaAddagiriNo ratings yet

- Varactor DiodeDocument3 pagesVaractor DiodeKenNo ratings yet

- Amplifiers: Technical Specifications Physical SpecificationsDocument1 pageAmplifiers: Technical Specifications Physical SpecificationsAmal Kumar DeNo ratings yet

- Table of ContentsDocument5 pagesTable of ContentsHa FaiazNo ratings yet

- PIC16F873 Voltage RegulatorDocument2 pagesPIC16F873 Voltage RegulatorMalamig SajapanNo ratings yet

- Uaa 2022Document6 pagesUaa 2022TZM BucNo ratings yet

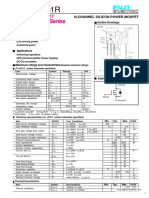

- Super FAP-G Series: Fuji Power MosfetDocument4 pagesSuper FAP-G Series: Fuji Power MosfetsaikumarNo ratings yet

- 4-Bit Binary To Decimal Decoder (BDD)Document6 pages4-Bit Binary To Decimal Decoder (BDD)Harsh Purwar100% (2)

- RT8205 PDFDocument28 pagesRT8205 PDFManuel Alberto CaceresNo ratings yet

- STV9302B: Vertical Deflection Booster For 2-A TV (50-60 HZ) Applications With 70-V Flyback GeneratorDocument15 pagesSTV9302B: Vertical Deflection Booster For 2-A TV (50-60 HZ) Applications With 70-V Flyback GeneratorTecnico GenioNo ratings yet

- Load RegulationDocument5 pagesLoad RegulationchanchaalNo ratings yet

- Panel Boost UpDocument5 pagesPanel Boost UpsachinNo ratings yet

- Phase Modulation: Prepared By: Engr. Iris T. AgneDocument16 pagesPhase Modulation: Prepared By: Engr. Iris T. AgneJayson CozNo ratings yet

- Ir 1153Document20 pagesIr 1153ytnateNo ratings yet

- Introduction To CMOS Logic CircuitsDocument176 pagesIntroduction To CMOS Logic CircuitsrdanwaraNo ratings yet

- Incremental Encoder Output Signal OverviewDocument3 pagesIncremental Encoder Output Signal OverviewmicaNo ratings yet

- Finalexam SolutionsDocument8 pagesFinalexam SolutionsJonah BallNo ratings yet

- Digital Logic - Digital Electronics Notes For GATE PDF DownloadDocument97 pagesDigital Logic - Digital Electronics Notes For GATE PDF DownloadKrishna arjunaNo ratings yet

- Transistor-Zener Diode Regulator CircuitsDocument7 pagesTransistor-Zener Diode Regulator Circuitsmohamed lamine elbiskriNo ratings yet