Professional Documents

Culture Documents

NCP5901 VR12 Compatible Synchronous Buck MOSFET Drivers: Soic 8 NB D Suffix CASE 751 Dfn8 MN Suffix Case 506aa

Uploaded by

Deilyn RivasOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

NCP5901 VR12 Compatible Synchronous Buck MOSFET Drivers: Soic 8 NB D Suffix CASE 751 Dfn8 MN Suffix Case 506aa

Uploaded by

Deilyn RivasCopyright:

Available Formats

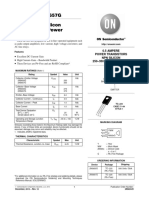

NCP5901

VR12 Compatible

Synchronous Buck MOSFET

Drivers

The NCP5901 is a high performance dual MOSFET gate driver

optimized to drive the gates of both high−side and low−side power http://onsemi.com

MOSFETs in a synchronous buck converter. It can drive up to 3 nF

load with a 25 ns propagation delay and 20 ns transition time.

Adaptive anti−cross−conduction and power saving operation

circuit can provide a low switching loss and high efficiency solution 8

for notebook and desktop systems. Bidirectional EN pin can provide 1

1

a fault signal to controller when the gate driver fault detect under

SOIC−8 NB DFN8

OVP, UVLO occur. Also, an under−voltage lockout function D SUFFIX MN SUFFIX

guarantees the outputs are low when supply voltage is low. CASE 751 CASE 506AA

Features

• Faster Rise and Fall Times

MARKING DIAGRAMS

• Adaptive Anti−Cross−Conduction Circuit

8

• Pre OV function

N5901

• ZCD Detect ALYW

• Floating Top Driver Accommodates Boost Voltages of up to 35 V G

1

• Output Disable Control Turns Off Both MOSFETs

• Under−voltage Lockout N5901 = Specific Device Code

A = Assembly Location

• Power Saving Operation Under Light Load Conditions

L = Wafer Lot

• Direct Interface to NCP6151 and Other Compatible PWM Y = Year

Controllers W = Work Week

G = Pb−Free Package

• Thermally Enhanced Package

• These are Pb−Free Devices 1

AJMG

Typical Applications G

• Power Solutions for Desktop Systems AJ = Specific Device Code

M = Date Code

G = Pb−Free Device

ORDERING INFORMATION

Device Package Shipping†

NCP5901MNTBG DFN8 3000 / Tape & Reel

(Pb−Free)

NCP5901DR2G SOIC−8 2500 / Tape & Reel

(Pb−Free)

†For information on tape and reel specifications,

including part orientation and tape sizes, please

refer to our Tape and Reel Packaging Specification

Brochure, BRD8011/D.

© Semiconductor Components Industries, LLC, 2013 1 Publication Order Number:

June, 2013 − Rev. 2 NCP5901/D

Free Datasheet http://www.datasheet4u.com/

NCP5901

BST 1 DRVH

PWM SW

FLAG

EN 9 GND

VCC DRVL

(Top View)

Figure 1. Pin Diagram

VCC BST

DRVH

PWM Logic

SW

Anti−Cross

Conduction

VCC

DRVL

EN

ZCD

UVLO Detection

Pre−OV

Fault

Figure 2. Block Diagram

Table 1. Pin Descriptions

Pin No. Symbol Description

1 BST Floating bootstrap supply pin for high side gate driver. Connect the bootstrap capacitor between this pin

and the SW pin.

2 PWM Control input. The PWM signal has three distinctive states: Low = Low Side FET Enabled, Mid = Diode

Emulation Enabled, High = High Side FET Enabled.

3 EN Logic input. A logic high to enable the part and a logic low to disable the part.

4 VCC Power supply input. Connect a bypass capacitor (0.1 mF) from this pin to ground.

5 DRVL Low side gate drive output. Connect to the gate of low side MOSFET.

6 GND Bias and reference ground. All signals are referenced to this node (QFN Flag).

7 SW Switch node. Connect this pin to the source of the high side MOSFET and drain of the low side MOSFET.

8 DRVH High side gate drive output. Connect to the gate of high side MOSFET.

9 FLAG Thermal flag. There is no electrical connection to the IC. Connect to ground plane.

http://onsemi.com

2

Free Datasheet http://www.datasheet4u.com/

NCP5901

12V_POWER

CR1

MMSD4148 TP1

R164 C4 +

0.027uF Q1 C1 C2 C3 CE9

R1

TP2 NTMFS4821N 4.7uF 4.7uF 4.7uF 390uF

1.02 0.0

NCP5901 TP3 R142

R143

0.0 VREG_SW1_HG 0.0

TP4 BST HG TP5

L VCCP

VREG_SW1_OUT

PWM PWM SW

235nH

DRON TP7

EN GND TP6 R3

VREG_SW1_LG Q9 Q10 2.2

VCC LG NTMFS4851N NTMFS4851N

JP13_ETCH CSN11

PAD

C5 TP8 C6

1uF 2700pF

JP14_ETCH CSP11

Figure 3. Application Circuit

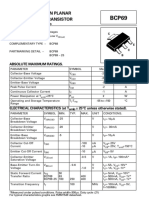

Table 2. ABSOLUTE MAXIMUM RATINGS

Pin Symbol Pin Name VMAX VMIN

VCC Main Supply Voltage Input 15 V −0.3 V

BST Bootstrap Supply Voltage 35 V wrt/ GND −0.3 V wrt/SW

40 V ≤ 50 ns wrt/ GND

15 V wrt/ SW

SW Switching Node 35 V −5 V

(Bootstrap Supply Return) 40 V ≤ 50 ns −10 V (200 ns)

DRVH High Side Driver Output BST+0.3 V −0.3 V wrt/SW

−2 V (<200 ns) wrt/SW

DRVL Low Side Driver Output VCC+0.3 V −0.3 V DC

−5 V (<200 ns)

PWM DRVH and DRVL Control Input 6.5 V −0.3 V

EN Enable Pin 6.5 V −0.3 V

GND Ground 0V 0V

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the

Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect

device reliability.

Table 3. THERMAL INFORMATION (All signals referenced to AGND unless noted otherwise)

Symbol Parameter Value Unit

RqJA Thermal Characteristic SOIC Package (Note 1) 123 °C/W

DFN Package (Note 1) 74

TJ Operating Junction Temperature Range (Note 2) 0 to 150 °C

TA Operating Ambient Temperature Range −10 to +125 °C

TSTG Maximum Storage Temperature Range −55 to +150 °C

MSL Moisture Sensitivity Level SOIC Package 1

DFN Package 1

* The maximum package power dissipation must be observed.

1. I in2 Cu, 1 oz thickness.

2. Operation at −40°C to −10°C guaranteed by design, not production tested.

http://onsemi.com

3

Free Datasheet http://www.datasheet4u.com/

NCP5901

Table 4. ELECTRICAL CHARACTERISTICS (Unless otherwise stated: −10°C < TA < +125°C; 4.5 V < VCC < 13.2 V,

4.5 V < BST−SWN < 13.2 V, 4.5 V < BST < 30 V, 0 V < SWN < 21 V)

Parameter Test Conditions Min. Typ. Max. Units

SUPPLY VOLTAGE

VCC Operation Voltage 4.5 13.2 V

Power ON Reset Threshold 2.75 3.2 V

UNDERVOLTAGE LOCKOUT

VCC Start Threshold 3.8 4.35 4.5 V

VCC UVLO Hysteresis 150 200 250 mV

Output Overvoltage Trip Threshold at Power Startup time, VCC > POR 2.1 2.25 2.4 V

Startup

SUPPLY CURRENT

Normal Mode Icc + Ibst, EN = 5 V, PWM = OSC, Fsw = 100 KHz, 12.2 mA

Cload = 3 nF for DRVH, 3 nF for DRVL

Standby Current Icc + Ibst, EN = GND 0.5 1.9 mA

Standby Current ICC + IBST, EN = HIGH, PWM = LOW, 2.1 mA

No loading on DRVH & DRVL

Standby Current ICC + IBST, EN = HIGH, PWM = HIGH, 2.2 mA

No loading on DRVH & DRVL

PWM INPUT

PWM Input High 3.4 V

PWM Mid−State 1.3 2.7 V

PWM Input Low 0.7 V

ZCD Blanking Timer 250 ns

HIGH SIDE DRIVER (VCC = 12 V)

Output Impedance, Sourcing Current VBST − VSW = 12 V 2.0 3.5 W

Output Impedance, Sinking Current VBST − VSW = 12 V 1.0 2.0 W

DRVH Rise Time trDRVH VVCC = 12 V, 3 nF load, VBST−VSW = 12 V 16 30 ns

DRVH Fall Time tfDRVH VVCC = 12 V, 3 nF load, VBST−VSW = 12 V 11 25 ns

DRVH Turn−Off Propagation Delay CLOAD = 3 nF 8.0 30 ns

tpdhDRVH

DRVH Turn−On Propagation Delay CLOAD = 3 nF 30 ns

tpdlDRVH

SW Pull Down Resistance SW to PGND 45 kW

DRVH Pull Down Resistance DRVH to SW, BST−SW = 0 V 45 kW

HIGH SIDE DRIVER (VCC = 5 V)

Output Impedance, Sourcing Current VBST − VSW = 5 V 4.5 W

Output Impedance, Sinking Current VBST − VSW = 5 V 2.9 W

DRVH Rise Time trDRVH VVCC = 5 V, 3 nF load, VBST − VSW = 5 V 30 ns

DRVH Fall Time tfDRVH VVCC = 5 V, 3 nF load, VBST − VSW = 5 V 27 ns

DRVH Turn−Off Propagation Delay CLOAD = 3 nF 20 ns

tpdhDRVH

DRVH Turn−On Propagation Delay CLOAD = 3 nF 27 ns

tpdlDRVH

SW Pull Down Resistance SW to PGND 45 kW

DRVH Pull Down Resistance DRVH to SW, BST−SW = 0 V 45 kW

http://onsemi.com

4

Free Datasheet http://www.datasheet4u.com/

NCP5901

Table 4. ELECTRICAL CHARACTERISTICS (Unless otherwise stated: −10°C < TA < +125°C; 4.5 V < VCC < 13.2 V,

4.5 V < BST−SWN < 13.2 V, 4.5 V < BST < 30 V, 0 V < SWN < 21 V)

Parameter Test Conditions Min. Typ. Max. Units

LOW SIDE DRIVER (VCC = 12 V)

Output Impedance, Sourcing Current 2.0 3.5 W

Output Impedance, Sinking Current 0.8 1.8 W

DRVL Rise Time trDRVL CLOAD = 3 nF 16 35 ns

DRVL Fall Time tfDRVL CLOAD = 3 nF 11 20 ns

DRVL Turn−Off Propagation Delay CLOAD = 3 nF 35 ns

tpdlDRVL

DRVL Turn−On Propagation Delay CLOAD = 3 nF 8.0 30 ns

tpdhDRVL

DRVL Pull Down Resistance DRVL to PGND, VCC = PGND 45 kW

LOW SIDE DRIVER (VCC = 5 V)

Output Impedance, Sourcing Current 4.5 W

Output Impedance, Sinking Current 2.4 W

DRVL Rise Time trDRVL CLOAD = 3 nF 30 ns

DRVL Fall Time tfDRVL CLOAD = 3 nF 22 ns

DRVL Turn−Off Propagation Delay CLOAD = 3 nF 27 ns

tpdlDRVL

DRVL Turn−On Propagation Delay CLOAD = 3 nF 12 ns

tpdhDRVL

DRVL Pull Down Resistance DRVL to PGND, VCC = PGND 45 kW

EN INPUT

Input Voltage High 2.0 V

Input Voltage Low 1.0 V

Hysteresis 500 mV

Normal Mode Bias Current −1 1 mA

Enable Pin Sink Current 4 30 mA

Propagation Delay Time 20 40 ns

SW Node

SW Node Leakage Current 20 mA

Zero Cross Detection Threshold Voltage SW to −20 mV, ramp slowly until BG goes off −6 mV

(Start in DCM mode) (Note 3)

Table 5. DECODER TRUTH TABLE

PWM INPUT ZCD DRVL DRVH

PWM High ZCD Reset Low High

PWM Mid Positive current through the inductor High Low

PWM Mid Zero current through the inductor Low Low

PWM Low ZCD Reset High Low

3. Guaranteed by design; not production tested.

http://onsemi.com

5

Free Datasheet http://www.datasheet4u.com/

NCP5901

1V

1V

Figure 4.

PWM

DRVH−SW

DRVL

IL

Figure 5. Timing Diagram

http://onsemi.com

6

Free Datasheet http://www.datasheet4u.com/

NCP5901

APPLICATIONS INFORMATION

The NCP5901 gate driver is a single phase MOSFET driver low, gate DRVH will go low after the propagation delay

designed for driving N−channel MOSFETs in a synchronous (tpd DRVH).

buck converter topology. The NCP5901 is designed to work The time to turn off the high side MOSFET is depending

with ON Semiconductor’s NCP6131 multi−phase controller. on the total gate charge of the high−side MOSFET. A timer

This gate driver is optimized for desktop applications. will be triggered once the high side MOSFET is turn off to

delay the turn on the low−side MOSFET.

Undervoltage Lockout

The DRVH and DRVL are held low until VCC reaches Low−Side Driver Timeout

4.5 V during startup. The PWM signals will control the gate In normal operation, the DRVH signal tracks the PWM

status when VCC threshold is exceeded. If VCC decreases to signal and turns off the Q1 high−side switch with a few 10

250 mV below the threshold, the output gate will be forced ns delay (tpdlDRVH) following the falling edge of the input

low until input voltage VCC rises above the startup threshold. signal. When Q1is turned off, DRVL is allowed to go high,

Q2 turns on, and the SW node voltage collapses to zero. But

Power−On Reset in a fault condition such as a high−side Q1 switch

Power−On Reset feature is used to protect a gate driver drain−source short circuit, the SW node cannot fall to zero,

avoid abnormal status driving the startup condition. When even when DRVH goes low. This driver has a timer circuit

the initial soft−start voltage is higher than 2.75 V, the gate to address this scenario. Every time the PWM goes low, a

driver will monitor the switching node SW pin. If SW pin DRVL on−time delay timer is triggered.

high than 2.25 V, bottom gate will be force to high for If the SW node voltage does not trigger a low−side

discharge the output capacitor. The fault mode will be latch turn−on, the DRVL on−time delay circuit does it instead,

and EN pin will force to be low, unless the driver is recycle. when it times out with tSW(TO) delay. If Q1 is still turned on,

When input voltage is higher than 4.5 V, and EN goes high, that is, its drain is shorted to the source, Q2 turns on and

the gate driver will normal operation, top gate driver creates a direct short circuit across the VDCIN voltage rail.

DRVH and bottom gate driver will follow the PWM signal The crowbar action causes the fuse in the VDCIN current

decode to a status. path to open. The opening of the fuse saves the load (CPU)

Bi−directional EN Signal from potential damage that the high−side switch short

Fault modes such as Power−On Reset and Undervoltage circuit could have caused.

Lockout will de−assert the EN pin, which will pull down Layout Guidelines

the DRON pin of controller as well. Thus the controller will Layout for DC−DC converter is very important. The

be shut down consequently. bootstrap and VCC bypass capacitors should be placed as

PWM Input and Zero Cross Detect (ZCD) close as to the driver IC.

The PWM input, along with EN and ZCD, control the Connect GND pin to local ground plane. The ground

state of DRVH and DRVL. plane can provide a good return path for gate drives and

When PWM is set high, DRVH will be set high after the reduce the ground noise. The thermal slug should be tied to

adaptive non−overlap delay. When PWM is set low, DRVL the ground plane for good heat dissipation. To minimize the

will be set high after the adaptive non−overlap delay. ground loop for low side MOSFET, the driver GND pin

When the PWM is set to the mid state, DRVH will be set should be close to the low−side MOSFET source pin. The

low, and after the adaptive non−overlap delay, DRVL will gate drive trace should be routed to minimize the length,

be set high. DRVL remains high during the ZCD blanking the minimum width is 20 mils.

time. When the timer is expired, the SW pin will be Gate Driver Power Loss Calculation

monitored for zero cross detection. After the detection, the The gate driver power loss consists of the gate drive loss

DRVL will be set low. and quiescent power loss.

Adaptive Nonoverlap The equation below can be used to calculate the power

The nonoverlap dead time control is used to avoid the dissipation of the gate driver. Where QGMF is the total gate

shoot through damage the power MOSFETs. When the charge for each main MOSFET and QGSF is the total gate

PWM signal pull high, DRVL will go low after a charge for each synchronous MOSFET.

propagation delay, the controller will monitors the fSW

ǒn MF

PDRV + [ QGMF ) n SF QGSFǓ ) ICC] VCC

switching node (SWN) pin voltage and the gate voltage of 2 n

the MOSFET to know the status of the MOSFET. When the Also shown is the standby dissipation factor (ICC ⋅ VCC)

low side MOSFET status is off an internal timer will delay of the driver.

turn on of the high–side MOSFET. When the PWM pull

http://onsemi.com

7

Free Datasheet http://www.datasheet4u.com/

NCP5901

PACKAGE DIMENSIONS

SOIC−8 NB

CASE 751−07

ISSUE AK

NOTES:

1. DIMENSIONING AND TOLERANCING PER

−X− ANSI Y14.5M, 1982.

A 2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A AND B DO NOT INCLUDE

MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006)

8 5 PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR

B S 0.25 (0.010) M Y M PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.127 (0.005) TOTAL

1 IN EXCESS OF THE D DIMENSION AT

4 MAXIMUM MATERIAL CONDITION.

−Y− K 6. 751−01 THRU 751−06 ARE OBSOLETE. NEW

STANDARD IS 751−07.

MILLIMETERS INCHES

G

DIM MIN MAX MIN MAX

A 4.80 5.00 0.189 0.197

C N X 45 _ B 3.80 4.00 0.150 0.157

SEATING C 1.35 1.75 0.053 0.069

PLANE D 0.33 0.51 0.013 0.020

−Z− G 1.27 BSC 0.050 BSC

H 0.10 0.25 0.004 0.010

0.10 (0.004) J 0.19 0.25 0.007 0.010

H M J K 0.40 1.27 0.016 0.050

D

M 0 _ 8 _ 0 _ 8 _

N 0.25 0.50 0.010 0.020

S 5.80 6.20 0.228 0.244

0.25 (0.010) M Z Y S X S

SOLDERING FOOTPRINT*

1.52

0.060

7.0 4.0

0.275 0.155

0.6 1.270

0.024 0.050

SCALE 6:1 ǒinches

mm Ǔ

*For additional information on our Pb−Free strategy and soldering

details, please download the ON Semiconductor Soldering and

Mounting Techniques Reference Manual, SOLDERRM/D.

http://onsemi.com

8

Free Datasheet http://www.datasheet4u.com/

NCP5901

PACKAGE DIMENSIONS

DFN8 2x2

CASE 506AA

ISSUE E

D NOTES:

A L L 1. DIMENSIONING AND TOLERANCING PER

B ASME Y14.5M, 1994 .

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION b APPLIES TO PLATED

L1 TERMINAL AND IS MEASURED BETWEEN

ÇÇ

0.15 AND 0.20 MM FROM TERMINAL TIP.

PIN ONE DETAIL A 4. COPLANARITY APPLIES TO THE EXPOSED

ÇÇ

REFERENCE E OPTIONAL PAD AS WELL AS THE TERMINALS.

CONSTRUCTIONS

MILLIMETERS

2X 0.15 C DIM MIN MAX

A 0.80 1.00

ÉÉ

A1 0.00 0.05

2X EXPOSED Cu MOLD CMPD

0.15 C A3 0.20 REF

ÉÉ

TOP VIEW b 0.20 0.30

D 2.00 BSC

D2 1.10 1.30

0.10 C DETAIL B A DETAIL B

E 2.00 BSC

E2 0.70 0.90

OPTIONAL e 0.50 BSC

CONSTRUCTION 0.30 REF

K

L 0.25 0.35

0.08 C L1 −−− 0.10

(A3)

NOTE 4 A1 SEATING

SIDE VIEW C PLANE

RECOMMENDED

SOLDERING FOOTPRINT*

DETAIL A

D2 8X

8X L 1.30 0.50

1 4 PACKAGE

OUTLINE

E2

0.90 2.30

K 8 5

8X b

e/2 1

0.10 C A B

e 8X

0.05 C NOTE 3

0.30 0.50

PITCH

BOTTOM VIEW

DIMENSIONS: MILLIMETERS

*For additional information on our Pb−Free strategy and soldering

details, please download the ON Semiconductor Soldering and

Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks,

copyrights, trade secrets, and other intellectual property. A listing of SCILLC’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent−Marking.pdf . SCILLC

reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products

for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including

without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different

applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical

experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components

in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product

could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall

indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney

fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was

negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws

and is not for resale in any manner.

PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: N. American Technical Support: 800−282−9855 Toll Free ON Semiconductor Website: www.onsemi.com

Literature Distribution Center for ON Semiconductor USA/Canada

P.O. Box 5163, Denver, Colorado 80217 USA Europe, Middle East and Africa Technical Support: Order Literature: http://www.onsemi.com/orderlit

Phone: 303−675−2175 or 800−344−3860 Toll Free USA/Canada Phone: 421 33 790 2910

Fax: 303−675−2176 or 800−344−3867 Toll Free USA/Canada Japan Customer Focus Center For additional information, please contact your loca

Email: orderlit@onsemi.com Phone: 81−3−5817−1050 Sales Representative

http://onsemi.com NCP5901/D

9

Free Datasheet http://www.datasheet4u.com/

You might also like

- DatasheetDocument5 pagesDatasheetDavid Alanoca100% (8)

- RA60H1317M RF Power MOSFET Amplifier Module DatasheetDocument9 pagesRA60H1317M RF Power MOSFET Amplifier Module DatasheetAbbas MaghazehiNo ratings yet

- CMOS Analog Circuit Design (Allen-2016)Document1,412 pagesCMOS Analog Circuit Design (Allen-2016)curliph0% (1)

- ncp5901 r2 OnDocument10 pagesncp5901 r2 OnakashNo ratings yet

- NCP 81258Document10 pagesNCP 81258Loc Nguyen HuyNo ratings yet

- NCP81152 ONSemiconductorDocument8 pagesNCP81152 ONSemiconductorwej10358No ratings yet

- +VCCGT Vegas 15341Document8 pages+VCCGT Vegas 15341Eric ArcherNo ratings yet

- NCP 1252Document17 pagesNCP 1252Riska Tri BanowatiNo ratings yet

- NCP45790 D-2317241Document13 pagesNCP45790 D-2317241SuBaRu GTNo ratings yet

- ncp81152 DDocument9 pagesncp81152 DNikhil khadeNo ratings yet

- Onsm S A0013302101 1Document16 pagesOnsm S A0013302101 1123No ratings yet

- Datasheet PDFDocument26 pagesDatasheet PDFalbertpaul0415No ratings yet

- ADP3110A_ONSemiconductorDocument8 pagesADP3110A_ONSemiconductorinfosolutionNo ratings yet

- NCP81253 5 V MOSFET Driver Compatible With Single-Phase IMVP8 ControllersDocument10 pagesNCP81253 5 V MOSFET Driver Compatible With Single-Phase IMVP8 ControllersBlue StacksNo ratings yet

- NCP81253 5 V MOSFET Driver Compatible With Single-Phase IMVP8 ControllersDocument11 pagesNCP81253 5 V MOSFET Driver Compatible With Single-Phase IMVP8 ControllersTom TomNo ratings yet

- NCV8871 Automotive Grade Non-Synchronous Boost Controller: SOIC 8 D Suffix CASE 751Document12 pagesNCV8871 Automotive Grade Non-Synchronous Boost Controller: SOIC 8 D Suffix CASE 751Albaro LedesmaNo ratings yet

- NCP1607 Cost Effective Power Factor Controller: Marking DiagramsDocument23 pagesNCP1607 Cost Effective Power Factor Controller: Marking DiagramslewisneoNo ratings yet

- NCP1250 D-2317076Document26 pagesNCP1250 D-2317076ricardo mauro oliveiraNo ratings yet

- NCP1607 DatasheetDocument23 pagesNCP1607 DatasheetingucvNo ratings yet

- NCP5212A, NCP5212T Single Synchronous Step-Down Controller: QFN16 Case 485apDocument19 pagesNCP5212A, NCP5212T Single Synchronous Step-Down Controller: QFN16 Case 485apokeinfoNo ratings yet

- NCP1252 Current Mode PWM Controller For Forward and Flyback ApplicationsDocument20 pagesNCP1252 Current Mode PWM Controller For Forward and Flyback Applicationspolice017789No ratings yet

- 1608b-pqbj Fuente MonoDocument24 pages1608b-pqbj Fuente MonohernanNo ratings yet

- CS3361 Alternator Voltage Regulator FET Driver: FeaturesDocument8 pagesCS3361 Alternator Voltage Regulator FET Driver: FeaturesQUYENNo ratings yet

- cs3361-FET DriverDocument10 pagescs3361-FET DriverSiam_SquareNo ratings yet

- Ncp81205a DDocument28 pagesNcp81205a DBlue Stacks100% (1)

- NCP3488 MOSFET Driver With Dual Outputs For Synchronous Buck ConvertersDocument7 pagesNCP3488 MOSFET Driver With Dual Outputs For Synchronous Buck ConvertersRoidysNo ratings yet

- NCP 1252Document20 pagesNCP 1252JonathanNo ratings yet

- ncv8141d2tg - 1119029 - Regulador - Modulo Direccion ChinacamionetaDocument14 pagesncv8141d2tg - 1119029 - Regulador - Modulo Direccion ChinacamionetaChristiam OrtegaNo ratings yet

- NCP1654 ONSemiconductorDocument23 pagesNCP1654 ONSemiconductorthanhNo ratings yet

- NCP1250 DDocument24 pagesNCP1250 DAnanias Sousa da SilvaNo ratings yet

- NCP1653, NCP1653A Compact, Fixed-Frequency, Continuous Conduction Mode PFC ControllerDocument21 pagesNCP1653, NCP1653A Compact, Fixed-Frequency, Continuous Conduction Mode PFC ControllerEfrén GonzálezNo ratings yet

- NCP1606 Cost Effective Power Factor Controller: Marking DiagramsDocument22 pagesNCP1606 Cost Effective Power Factor Controller: Marking DiagramsIvan Alberto Pinituj GarciaNo ratings yet

- NCP1582, NCP1582A, NCP1583 Low Voltage Synchronous Buck ControllersDocument16 pagesNCP1582, NCP1582A, NCP1583 Low Voltage Synchronous Buck ControllersDaiverJuarezNo ratings yet

- NCP1606 Cost Effective Power Factor Controller: Marking DiagramsDocument22 pagesNCP1606 Cost Effective Power Factor Controller: Marking DiagramsVanessa FumesNo ratings yet

- ncv8518 - Regulador Voltaje Chevrolet Sonic BCMDocument12 pagesncv8518 - Regulador Voltaje Chevrolet Sonic BCMChristiam OrtegaNo ratings yet

- NCP 81174Document18 pagesNCP 81174techgamebr85No ratings yet

- Power Factor Controller For Compact and Robust, Continuous Conduction Mode Pre-Converters NCP1654Document24 pagesPower Factor Controller For Compact and Robust, Continuous Conduction Mode Pre-Converters NCP1654Ed LabNo ratings yet

- ncp1251 DDocument25 pagesncp1251 DAmilcar SilvaNo ratings yet

- NCV59744 Linear Voltage Regulator With Bias Rail, 3 A, Very Low Dropout and Programmable Soft-StartDocument12 pagesNCV59744 Linear Voltage Regulator With Bias Rail, 3 A, Very Low Dropout and Programmable Soft-StartAdrian WongNo ratings yet

- MJL21193 (PNP), MJL21194 (NPN) Silicon Power TransistorsDocument7 pagesMJL21193 (PNP), MJL21194 (NPN) Silicon Power TransistorsAshrafuz ZamanNo ratings yet

- Ic - NCP1631Document24 pagesIc - NCP1631Alexandre SoaresNo ratings yet

- NCP1380 Quasi-Resonant Current-Mode Controller For High-Power Universal Off-Line SuppliesDocument26 pagesNCP1380 Quasi-Resonant Current-Mode Controller For High-Power Universal Off-Line SupplieszokiNo ratings yet

- NCP1377PGDocument17 pagesNCP1377PGMeP-SI CRDNo ratings yet

- 2n5655gDocument5 pages2n5655gcarlos robertoNo ratings yet

- NJD2873 Power Transistors: NPN Silicon DPAK For Surface Mount ApplicationsDocument5 pagesNJD2873 Power Transistors: NPN Silicon DPAK For Surface Mount ApplicationsAngel Orlando Monrroy MéndezNo ratings yet

- NCP1230 DDocument21 pagesNCP1230 DperoNo ratings yet

- LD7523Document18 pagesLD7523AssembleiaDeDeusSepherEloahNo ratings yet

- 35V Voltage Resistance 1A LDO Regulator: DatasheetDocument20 pages35V Voltage Resistance 1A LDO Regulator: DatasheetDaniela GarciaNo ratings yet

- LD7577 DS 01 PDFDocument18 pagesLD7577 DS 01 PDFLucilia Dos Santos100% (2)

- NCP1337 PWM Current-Mode Controller For Free Running Quasi-Resonant OperationDocument15 pagesNCP1337 PWM Current-Mode Controller For Free Running Quasi-Resonant OperationJavier RodriguezNo ratings yet

- LD7578J LeadtrendDocument19 pagesLD7578J Leadtrendnagahara.eduardoNo ratings yet

- LD7523 PDFDocument18 pagesLD7523 PDFAmalio MamaniNo ratings yet

- LD7537 PWM ControlerDocument16 pagesLD7537 PWM ControlerAbu AsyifaNo ratings yet

- Electronic Compass IC - HM55B (Datasheet)Document7 pagesElectronic Compass IC - HM55B (Datasheet)Anirudha Mhase100% (1)

- Nud3124 D-1814421Document12 pagesNud3124 D-1814421Ehsan AsgariNo ratings yet

- Transistor Q 401, 402 mps6560-d-1193587Document4 pagesTransistor Q 401, 402 mps6560-d-1193587Sivaram Prasad. KNo ratings yet

- NC7WZ04 D-1812077Document12 pagesNC7WZ04 D-1812077Michał PestrakiewiczNo ratings yet

- BookDocument8 pagesBookThakuri Man SinghNo ratings yet

- R1283x SERIES: 2ch DC/DC For CCD & OLEDDocument26 pagesR1283x SERIES: 2ch DC/DC For CCD & OLEDarnaud.herbertNo ratings yet

- NCP1560 Full Featured Voltage Mode PWM Controller: SO 16 D Suffix CASE 751BDocument20 pagesNCP1560 Full Featured Voltage Mode PWM Controller: SO 16 D Suffix CASE 751BraveendraNo ratings yet

- NSS40201L D-1813517Document8 pagesNSS40201L D-1813517Carlos Ortega MartinezNo ratings yet

- 12.5 Oh GR CN ZDL SP Hdil CalDocument22 pages12.5 Oh GR CN ZDL SP Hdil CalStephanyNo ratings yet

- 2sa1941 & 2SC5198 - 140V - 10a - 100W - Audio AmplifierDocument4 pages2sa1941 & 2SC5198 - 140V - 10a - 100W - Audio Amplifiercris_powerNo ratings yet

- Brief: High-Definition Satellite System-On-ChipDocument2 pagesBrief: High-Definition Satellite System-On-ChipDeilyn RivasNo ratings yet

- P-Channel Mos Field Effect Transistor For High Speed SwitchingDocument8 pagesP-Channel Mos Field Effect Transistor For High Speed SwitchingDeilyn RivasNo ratings yet

- Ir Codes 10 02 14Document31 pagesIr Codes 10 02 14bejanNo ratings yet

- b2 DatasheetDocument1 pageb2 Datasheetari_kotagedeNo ratings yet

- Jtag CPLD PDFDocument1 pageJtag CPLD PDFDeilyn RivasNo ratings yet

- Toshiba Transistor Silicon PNP Epitaxial Type (PCT Process) 2SA1013Document5 pagesToshiba Transistor Silicon PNP Epitaxial Type (PCT Process) 2SA1013ias2008No ratings yet

- Ippsb-Db: Mainboard User GuideDocument19 pagesIppsb-Db: Mainboard User GuideDeilyn RivasNo ratings yet

- Ippsb-Db: Mainboard User GuideDocument19 pagesIppsb-Db: Mainboard User GuideDeilyn RivasNo ratings yet

- BAV23A/C/S Features Mechanical Data: Surface Mount High Voltage Dual Switching DiodeDocument5 pagesBAV23A/C/S Features Mechanical Data: Surface Mount High Voltage Dual Switching DiodeDeilyn RivasNo ratings yet

- Surface Mountable PTC Resettable Fuse: JK-NSMD Series: FeaturesDocument7 pagesSurface Mountable PTC Resettable Fuse: JK-NSMD Series: FeaturesDeilyn RivasNo ratings yet

- Downgrading From U-Boot 1.1.4/1.1.6 To U-Boot 1.1.3 On Cc9P9360 Modules To Run Old Wince5.X or Lxnetes-3.X Firmware, Using Nvram From EepromDocument2 pagesDowngrading From U-Boot 1.1.4/1.1.6 To U-Boot 1.1.3 On Cc9P9360 Modules To Run Old Wince5.X or Lxnetes-3.X Firmware, Using Nvram From EepromDeilyn Rivas0% (1)

- Aod472 PDFDocument6 pagesAod472 PDFJuan Carlos ChavezNo ratings yet

- Quad 3-state buffer datasheetDocument5 pagesQuad 3-state buffer datasheetbl19cm7No ratings yet

- Schematics 797930Document6 pagesSchematics 797930Deilyn RivasNo ratings yet

- Sot223 PNP Silicon Planar Medium Power Transistor: Absolute Maximum RatingsDocument1 pageSot223 PNP Silicon Planar Medium Power Transistor: Absolute Maximum RatingsDeilyn RivasNo ratings yet

- Trenchmos Transistor Buk7840-55 Standard Level Fet: General Description Quick Reference DataDocument9 pagesTrenchmos Transistor Buk7840-55 Standard Level Fet: General Description Quick Reference DataDeilyn RivasNo ratings yet

- SEMICONDUCTOR KTA1241 TECHNICAL DATA EPITAXIAL PLANAR PNPDocument2 pagesSEMICONDUCTOR KTA1241 TECHNICAL DATA EPITAXIAL PLANAR PNPDeilyn RivasNo ratings yet

- Layout Guidelines For ControllersDocument7 pagesLayout Guidelines For Controllersnrupavesh nNo ratings yet

- TC3162L2M ADSL2/2+ Bridge/Router Processor Data SheetDocument1 pageTC3162L2M ADSL2/2+ Bridge/Router Processor Data SheetPlastipack C.A.No ratings yet

- Power Amplifier Applications Power Switching Applications: Maximum RatingsDocument5 pagesPower Amplifier Applications Power Switching Applications: Maximum RatingsDeilyn RivasNo ratings yet

- Low-Cost Multichemistry Battery Chargers: General Description FeaturesDocument29 pagesLow-Cost Multichemistry Battery Chargers: General Description FeaturesDeilyn RivasNo ratings yet

- LP141WX3 TLN1Document31 pagesLP141WX3 TLN1Deilyn RivasNo ratings yet

- Internal-Switch Boost Regulator With Integrated High-Voltage Level Shifter and Op AmpDocument17 pagesInternal-Switch Boost Regulator With Integrated High-Voltage Level Shifter and Op AmpDeilyn RivasNo ratings yet

- Introduction To PIC Programming: Baseline Architecture and Assembly LanguageDocument19 pagesIntroduction To PIC Programming: Baseline Architecture and Assembly LanguageDeilyn RivasNo ratings yet

- A1013 Utc PDFDocument3 pagesA1013 Utc PDFDeilyn RivasNo ratings yet

- 2SC2625Document4 pages2SC2625marciovirtuatec1013No ratings yet

- 74HC4050ADocument9 pages74HC4050ADeilyn RivasNo ratings yet

- MC 34704Document54 pagesMC 34704Ankit SinghNo ratings yet

- BD9486FDocument37 pagesBD9486F94430s19684No ratings yet

- 8V To 35V, 3.0A 1ch Buck Converter With Integrated FET: DatasheetDocument21 pages8V To 35V, 3.0A 1ch Buck Converter With Integrated FET: DatasheetArdhi Purna bagasNo ratings yet

- Device matching mechanisms and layout techniquesDocument41 pagesDevice matching mechanisms and layout techniquesvarun186No ratings yet

- EE 120 - Integrated Circuit FamiliesDocument15 pagesEE 120 - Integrated Circuit FamiliesAids SumaldeNo ratings yet

- (SiC-En-2013-2) A Comparative Performance Study of An Interleaved Boost Converter Using Commercial Si and SiC Diodes For PV ApplicationsDocument11 pages(SiC-En-2013-2) A Comparative Performance Study of An Interleaved Boost Converter Using Commercial Si and SiC Diodes For PV Applicationsnuaa_qhhNo ratings yet

- Connecting IGBTs in Parallel FundamentalsDocument6 pagesConnecting IGBTs in Parallel FundamentalsonafetsNo ratings yet

- 62 Power Semiconductor DevicesDocument73 pages62 Power Semiconductor DevicesIsabela SmithNo ratings yet

- 212 Fall 2005 PDFDocument176 pages212 Fall 2005 PDFcombatps1No ratings yet

- 3S0680RFB-Fairchild SemiconductorDocument12 pages3S0680RFB-Fairchild SemiconductorDeveloper AwladNo ratings yet

- TriennaleDocument129 pagesTriennaleJesus UrrestiNo ratings yet

- Manjula Summary - 22516081Document30 pagesManjula Summary - 22516081Nagireddy KalluriNo ratings yet

- DDCA Ch1Document99 pagesDDCA Ch1Dheer MehrotraNo ratings yet

- Etat de L'art Et Prospectives Sur Les Composants de Puissance Grand GapDocument16 pagesEtat de L'art Et Prospectives Sur Les Composants de Puissance Grand GapkmcablacNo ratings yet

- Arduino Power Inverter CircuitsDocument8 pagesArduino Power Inverter CircuitsjuliocastNo ratings yet

- Chengzhou WangDocument159 pagesChengzhou WangAnonymous n30qTRQPoINo ratings yet

- Critikon Dinamap Recorder Modul - Service ManualDocument32 pagesCritikon Dinamap Recorder Modul - Service ManualJulio Benancio ZuluagaNo ratings yet

- Ultrasensitive Photodetectors Based On Monolayer MDocument6 pagesUltrasensitive Photodetectors Based On Monolayer MNicholas MilsonNo ratings yet

- ZRAM-Zero Capacitor RAM: Jennis Thomas Roll No:EPAHECS025 S7 Computer Science and EngineeringDocument39 pagesZRAM-Zero Capacitor RAM: Jennis Thomas Roll No:EPAHECS025 S7 Computer Science and EngineeringJennis ThomasNo ratings yet

- APM4305KDocument10 pagesAPM4305KvannadioNo ratings yet

- Excellent DC Characteristics of Hemts On Semi-Insulating Silicon Carbide SubstrateDocument2 pagesExcellent DC Characteristics of Hemts On Semi-Insulating Silicon Carbide Substraterahil7860No ratings yet

- High-Side Current Sensing: Difference Amp vs. Current Sense AmpDocument3 pagesHigh-Side Current Sensing: Difference Amp vs. Current Sense Ampyatheesh_kcNo ratings yet

- STM4639T: P-Channel Enhancement Mode Field Effect TransistorDocument8 pagesSTM4639T: P-Channel Enhancement Mode Field Effect TransistorMessias SouzaNo ratings yet

- (SiC-En-2013-22) Molding Compounds Adhesion and Influence On Reliability of Plastic Packages For SiC-Based Power MOS DevicesDocument13 pages(SiC-En-2013-22) Molding Compounds Adhesion and Influence On Reliability of Plastic Packages For SiC-Based Power MOS Devicesnuaa_qhhNo ratings yet

- Driver Circuits - PowerGuru - Power Electronics Information PortalDocument5 pagesDriver Circuits - PowerGuru - Power Electronics Information PortaldevchandarNo ratings yet

- OB2301W On BrightElectronicsDocument11 pagesOB2301W On BrightElectronicsIlago BenignoNo ratings yet

- B.E CSE Full Time Curriculam-2010 PDFDocument135 pagesB.E CSE Full Time Curriculam-2010 PDFJai SharmaNo ratings yet

- Modified Sine Wave UPS Report (UET, Lahore)Document43 pagesModified Sine Wave UPS Report (UET, Lahore)Ahsan Mubashir0% (2)