Professional Documents

Culture Documents

Basic Interview Questions On DFT

Uploaded by

deepaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Basic Interview Questions On DFT

Uploaded by

deepaCopyright:

Available Formats

Basic Interview Questions on DFT.

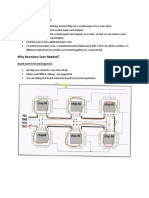

2.Scan:

•

What is the significance of scan-compression/EDT during ATPG?To decrease the TDV and

TAT

•

What is the reason for increase in pattern count for compressed mode?Because the chain

lenght is small,more number of chains exist.More number of control bits toidentify faults in

EDT.

•

The actual compression achieved will be less than the specified compression

factor.Why?Because of extra cycles(initialization cycles) in EDT.

•

Deciding factors of scan design? Number of channels on tester, memory available on

channel and number of scan pins.

•

Scan length, Scan chains, hierarchical scan concept?

•

How scan chains are handled from a 3

rd

party IP in the chip?By using "add subchain command"

•

Use of LOCKUP latch?a) When two clock domains exist , b) When one domain with different

edges trigger the flops,c) When clock skew is more than half cycle of hold time.

•

Difference between LOS and LOC?Look for the basic differences in the guide.Other

difference is that in LOS,there is a chance of testing unrequired functional paths because of

last shift is done when SE=1.

•

Scan considerations required for At-speed test?a) OCC that supports and generate 2 pulses

for capture cycle. b) Free running functional clocks.

•

What are advantages of LOS and disadvantages when compared to LOC?

•

How do you avoid limitations of LOS?a) Consider SE as clock, b) Pipeline scan enable.

•

How do we manage chain balancing and what is the requirement?

•

Timing issues specific to scan chain clock domain mixing?Hold issues.Use lockup latch to

avoid them.Clock skew to be decreased.

•

How to avoid hold issues when scan chain is stitched from +ve edge to –ve edge flop?

You might also like

- Basic Interview Questions On DFTDocument5 pagesBasic Interview Questions On DFTDeepak Chanda0% (2)

- DFT Interview Questions & AnswersDocument22 pagesDFT Interview Questions & Answersdeepa100% (4)

- DFT Interview Questions & AnswersDocument22 pagesDFT Interview Questions & Answersdeepa100% (4)

- Interview Questions Related To Scan, ATPG, EDT and SimulationDocument1 pageInterview Questions Related To Scan, ATPG, EDT and SimulationSiva SreeramdasNo ratings yet

- A Practical On Chip Clock Controller Circuit Design PDFDocument22 pagesA Practical On Chip Clock Controller Circuit Design PDFBodepu V SanthoshkumarNo ratings yet

- EdtDocument10 pagesEdtjagruthimsNo ratings yet

- Logic BIST Case Studies and Real IssuesDocument10 pagesLogic BIST Case Studies and Real IssuesprakashthamankarNo ratings yet

- Embedded Deterministic Test: by M. BalakrishnaDocument28 pagesEmbedded Deterministic Test: by M. Balakrishnasuryatejamula0% (1)

- Segregated QuestionsDocument1 pageSegregated QuestionsdeepaNo ratings yet

- Assignment - 6Document4 pagesAssignment - 6kishorNo ratings yet

- MbistDocument38 pagesMbistNaga NitheshNo ratings yet

- EDT IMP QuestionsDocument1 pageEDT IMP QuestionsMayur MestryNo ratings yet

- Tessent Samsung Han U2U18Document22 pagesTessent Samsung Han U2U18vasav1No ratings yet

- VLSIGURU SCAN INSERTION LABDocument2 pagesVLSIGURU SCAN INSERTION LABsenthilkumarNo ratings yet

- How To Use Embedded Instruments and IJTAG-JTAG An IEEE P1687 Tutorial PDFDocument10 pagesHow To Use Embedded Instruments and IJTAG-JTAG An IEEE P1687 Tutorial PDFAnjali TailorNo ratings yet

- Paper-Loc and LosDocument5 pagesPaper-Loc and LosRUPIREDDY PRAVEENNo ratings yet

- Boundary ScanDocument8 pagesBoundary Scanmechbull11No ratings yet

- ATPG IMP QuestionsDocument1 pageATPG IMP QuestionsMayur MestryNo ratings yet

- Full Scan Vs Partial Scan EgDocument5 pagesFull Scan Vs Partial Scan Egsenthilkumar100% (1)

- Asic Design Flow:: Specification FloorplanDocument9 pagesAsic Design Flow:: Specification Floorplanp gangadhar KumarNo ratings yet

- Boundary ScanDocument26 pagesBoundary Scansreeramya021No ratings yet

- On Chip Clock Controller For At-Speed TestingDocument4 pagesOn Chip Clock Controller For At-Speed TestingSachin*123No ratings yet

- Full and Fast SequentialDocument4 pagesFull and Fast SequentialdeepaNo ratings yet

- Case12d ObservationDocument3 pagesCase12d ObservationsenthilkumarNo ratings yet

- Scan Insertion Lab ObservationsDocument3 pagesScan Insertion Lab ObservationssenthilkumarNo ratings yet

- Tap ControllerDocument16 pagesTap ControllerMoin PashaNo ratings yet

- Fault classification and testing techniques in VLSI circuitsDocument24 pagesFault classification and testing techniques in VLSI circuitslavanyaNo ratings yet

- Why Boundary Scan Needed?Document39 pagesWhy Boundary Scan Needed?srikanth100% (1)

- EDT Lab Observations AnalysisDocument42 pagesEDT Lab Observations Analysispoojithas acharyaNo ratings yet

- Enhanced Timing Closure Using LatchesDocument6 pagesEnhanced Timing Closure Using LatchesMelody ShieldsNo ratings yet

- Scan InsertionDocument40 pagesScan InsertionAmena FarhatNo ratings yet

- Assignment 1Document3 pagesAssignment 1dheeraj.d JainNo ratings yet

- DFT (Design For Testability)Document21 pagesDFT (Design For Testability)lavanyaNo ratings yet

- MBIST Verification Best Practices ChallengesDocument5 pagesMBIST Verification Best Practices ChallengessureshNo ratings yet

- Testing of Repairable Embedded Memories in SoC Approach and ChallengesDocument6 pagesTesting of Repairable Embedded Memories in SoC Approach and Challengesassantiago1No ratings yet

- Jtag PresentationDocument21 pagesJtag PresentationNivaz ChockkalingamNo ratings yet

- Automating P1500 Wrapper CreationDocument24 pagesAutomating P1500 Wrapper CreationKrish GokulNo ratings yet

- VLSIGURU DFT TRAINING SCAN INSERTION LABDocument2 pagesVLSIGURU DFT TRAINING SCAN INSERTION LABsenthilkumarNo ratings yet

- Test PointsDocument21 pagesTest Pointsanusha killariNo ratings yet

- DFT Lbist PDFDocument10 pagesDFT Lbist PDFAman TyagiNo ratings yet

- Mirafara Interview QuestionsDocument1 pageMirafara Interview QuestionsMayur MestryNo ratings yet

- Why Masking Is Needed: Scan Chain Masking in The AcompactorDocument6 pagesWhy Masking Is Needed: Scan Chain Masking in The AcompactorIlaiyaveni IyanduraiNo ratings yet

- Scan Chain: Scan Chain Is A Technique Used in DesignDocument7 pagesScan Chain: Scan Chain Is A Technique Used in DesignpraveenNo ratings yet

- QC Interview Qns DFTDocument15 pagesQC Interview Qns DFTdeepaNo ratings yet

- DFT Interview QuestionsDocument1 pageDFT Interview Questionsnagabhairu anushaNo ratings yet

- Vlsi TV Lecture 10 BscanDocument37 pagesVlsi TV Lecture 10 BscanRana Babar AliNo ratings yet

- Cell-Aware ATPG Test Methods Improve Test Quality: A Brief History of IC TestDocument8 pagesCell-Aware ATPG Test Methods Improve Test Quality: A Brief History of IC Testsenthilkumar100% (1)

- DFT Tutorial PDFDocument5 pagesDFT Tutorial PDFVishwaNo ratings yet

- Hold and Setup Violation and SDFDocument2 pagesHold and Setup Violation and SDFIlaiyaveni IyanduraiNo ratings yet

- Lab4 Testing DFTDocument6 pagesLab4 Testing DFTDeepuNo ratings yet

- Digital Testing: Key Concepts of Scan-Path DesignDocument54 pagesDigital Testing: Key Concepts of Scan-Path DesignaguohaqdoNo ratings yet

- Sample Vlsi ResumeDocument2 pagesSample Vlsi ResumePavan KumarNo ratings yet

- (Notes) DESIGN FOR TESTABILITYDocument34 pages(Notes) DESIGN FOR TESTABILITYsarathkumarNo ratings yet

- Hierarchical Scan and Atpg For Two Stage PDFDocument3 pagesHierarchical Scan and Atpg For Two Stage PDFNeusilica school of VLSINo ratings yet

- Tracing CoverageDocument2 pagesTracing CoverageSrinath M SNo ratings yet

- Fastscan Tutorial v02Document55 pagesFastscan Tutorial v02Raghavendra MatturNo ratings yet

- Fault ClassificationDocument7 pagesFault ClassificationsuburaajNo ratings yet

- Training On EDT (1) - Copy (1) (3) 1Document52 pagesTraining On EDT (1) - Copy (1) (3) 1veena100% (1)

- Dftadvisor TutorialDocument36 pagesDftadvisor TutorialSrikiran DevarabhotlaNo ratings yet

- Lab ReportDocument17 pagesLab ReportYashwanthKumarNo ratings yet

- Importent Document For DFT PDFDocument10 pagesImportent Document For DFT PDFBharathi MahadevacharNo ratings yet

- DFT Interview QuestionsDocument5 pagesDFT Interview QuestionsHardik TrivediNo ratings yet

- Interview VlsiDocument47 pagesInterview VlsiKulwant Nagi100% (1)

- New DlauDocument52 pagesNew DlaudeepaNo ratings yet

- Interview VlsiDocument47 pagesInterview VlsiKulwant Nagi100% (1)

- Deepa PPT 49Document20 pagesDeepa PPT 49deepaNo ratings yet

- VLSIDesignDocument55 pagesVLSIDesignSumit KulshreshthaNo ratings yet

- Frequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimeDocument15 pagesFrequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimedeepaNo ratings yet

- HDL Programming Lab Manual Final UpdatedDocument77 pagesHDL Programming Lab Manual Final UpdateddeepaNo ratings yet

- Interview VlsiDocument47 pagesInterview VlsiKulwant Nagi100% (1)

- QC Interview Qns DFTDocument15 pagesQC Interview Qns DFTdeepaNo ratings yet

- Full and Fast SequentialDocument4 pagesFull and Fast SequentialdeepaNo ratings yet

- Coverage Improvement: by Deepa.BDocument13 pagesCoverage Improvement: by Deepa.BdeepaNo ratings yet

- NXP Interview QuestionsDocument29 pagesNXP Interview Questionsdeepa100% (1)

- QUALCOMM Interview Questions 1. Basic View of Compression?Document9 pagesQUALCOMM Interview Questions 1. Basic View of Compression?deepa100% (2)

- Wa0005 PDFDocument2 pagesWa0005 PDFsrinivasanNo ratings yet

- Memory BIST DiagramsDocument28 pagesMemory BIST DiagramsPrasad Kalyan100% (1)

- Setup & Hold ViolationDocument20 pagesSetup & Hold ViolationdeepaNo ratings yet

- Definite Integrals Part-3 (Improper Definite Integral)Document13 pagesDefinite Integrals Part-3 (Improper Definite Integral)deepaNo ratings yet

- Interview Questions DFTDocument1 pageInterview Questions DFTdeepaNo ratings yet

- Timing Issues: by Deepa .BDocument21 pagesTiming Issues: by Deepa .BdeepaNo ratings yet

- MemoryDocument29 pagesMemorydeepaNo ratings yet

- in Simulation, Parallel Patterns Are Failing But Serial Patterns Are Passing Why? (Vice-Versa)Document1 pagein Simulation, Parallel Patterns Are Failing But Serial Patterns Are Passing Why? (Vice-Versa)deepaNo ratings yet

- Interview Questions DFTDocument1 pageInterview Questions DFTdeepaNo ratings yet