Professional Documents

Culture Documents

Chapter 5 Control Design: Computer Architecture II (CT-404)

Uploaded by

Hpone PainfOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Chapter 5 Control Design: Computer Architecture II (CT-404)

Uploaded by

Hpone PainfCopyright:

Available Formats

Chapter 5 Control Design

1 Computer Architecture II (CT-404)

Previous Topic

Topic 01: Basic Concepts and Hardwired Control

2 Computer Architecture II (CT-404)

Topic 02: Designing Hardwired

Control Units

Multiplier Control

CPU Control Unit

Control Unit Design

3 Computer Architecture II (CT-404)

Multiplier Control

Fig. Twos-

complement

multiplier

with a set of

control

points.

Computer Architecture II (CT-404)

4

Implementing A Multiplier Control Unit

Begin

Yes

COUNT(7)=1?

S0 Q(0)=0?

No

No Yes

C2,C3,C4

S3 Yes

S1 C9, C10

Q(0)=0?

A:=A+M

A:=0

F:=M(7) and Q(0) or F No C2,C3, C7

COUNT:=0 C4,C5 S7

F:=0 S5 OUTBUS:=A

M:=INBUS

A:=A−M

C0,C1,C11

S4 Q(0):=0

S0

S C8 A(7):=F

2 S6 C6

A(6:0).Q:=A.Q(7:1) End

Q:=INBUS COUNT:=COUNT+1 OUTBUS:=Q

Cycle 0 Cycle 8 Cycle 9

Cycle 1 to 7

5 Computer Architecture II (CT-404) Fig. Flowchart for twos-complement multiplier

Implementing A Multiplier Control Unit

Fig. State table for the multiplier control

6 Computer Architecture II (CT-404)

Implementing A Multiplier Control Unit

The next state equations The output equations

7 Computer Architecture II (CT-404)

Implementing A Multiplier Control Unit

Fig. All-NAND

classical design

for the

multiplier

control unit

8 Computer Architecture II (CT-404)

Implementing A Multiplier Control Unit

Fig. All-NAND

one-hot design

for the

multiplier

control unit

9 Computer Architecture II (CT-404)

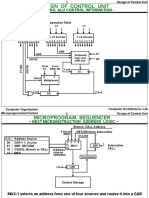

CPU Control Unit

Fig. Organization of an

accumulator-based

CPU

10 Computer Architecture II (CT-404)

CPU Control Unit

The accumulator-based CPU consists of a data path unit DPU

designed to execute the set of 10 basic single-address

instructions listed as follow:

Data transfer LD X

ST X

MOV DR, AC

MOV AC, DR

Data Processing ADD

SUB

AND

NOT

Program control BRA adr

BZ adr.

11 Computer Architecture II (CT-404)

Instruction Set of an accumulator-based

CPU

Data Transfer

HDL format Assembly Comment

format

AC := M(X) LD X Load X from M into AC

M(X) := AC ST X Store contents of AC in M as X

DR:= AC MOV DR, AC Copy contents of AC to DR

AC:= DR MOV AC, DR Copy contents of DR to AC

12 Computer Architecture II (CT-404)

Instruction Set of an accumulator-based

CPU

Data Processing

Assembly

HDL format Comment

format

AC := AC + DR ADD Add DR to AC

AC := AC - DR SUB Subtract DR from AC

AC := AC and DR AND And DR to AC

AC := not AC NOT Complement contents of

AC

13 Computer Architecture II (CT-404)

Instruction Set of an accumulator-based

CPU

Program Control

HDL format Assembly Comment

format

PC := M (adr) BRA adr Jump to instruction with

address adr

If AC := 0 then BZ adr Jump to instruction adr

PC := M (adr) if AC = 0

14 Computer Architecture II (CT-404)

Control points for accumulator-based

CPU

Fig. Control Signal Definition

15 Computer Architecture II (CT-404)

Fig. Organization of a hardwired control unit for the accumulator-based CPU.

16 Computer Architecture II (CT-404)

Implementing a Program Control Unit

Fig. State transition

graph for the

accumulator-based

CPU.

17 Computer Architecture II (CT-404)

The next state equations

The output equations

18 Computer Architecture II (CT-404)

Fig. One-hot implementation of the CPU state transition graph

19 Computer Architecture II (CT-404)

References

Hayes, John P. Computer Architecture and

Organization, 3rd ed. McGraw-Hill, 1998.

The third edition of Computer Architecture and

Organization is intended as a text for Computer

Technology courses at the undergraduate level.

Copyright (c) 1998 by The McGraw-Hill Companies,

Inc.

20 Computer Architecture II (CT-404)

Have a Nice Day!

21 Computer Architecture II (CT-404)

You might also like

- Chapter 5 Control Design: Computer Architecture II (CT-404)Document27 pagesChapter 5 Control Design: Computer Architecture II (CT-404)Hpone PainfNo ratings yet

- Lcdf3 Chap 10 p2Document32 pagesLcdf3 Chap 10 p2Ali Ahmad100% (1)

- L-4rr-lI/CSE Date: 27/0312023: Section-ADocument35 pagesL-4rr-lI/CSE Date: 27/0312023: Section-AQuazi Hasnat IrfanNo ratings yet

- MPI Compre PartA 2019 SolDocument2 pagesMPI Compre PartA 2019 SolVishweshRaviShrimaliNo ratings yet

- CEG 2136 - Fall 2008 - Final PDFDocument9 pagesCEG 2136 - Fall 2008 - Final PDFAmin DhouibNo ratings yet

- Mid Term Exam Solutions TCS 402Document18 pagesMid Term Exam Solutions TCS 402Obsii ChalaNo ratings yet

- 151811-2151707-Mci - Winter 2018Document2 pages151811-2151707-Mci - Winter 2018Bhautik Daxini100% (1)

- IES - Electronics Engineering - Digital Electronic CircuitsDocument66 pagesIES - Electronics Engineering - Digital Electronic Circuitsedwinaustine100% (4)

- PLC Programming Chapter 10 PLC Math InstructionsDocument18 pagesPLC Programming Chapter 10 PLC Math InstructionsReineNo ratings yet

- Cse 4223Document2 pagesCse 4223sayem12No ratings yet

- MTech QBDocument2 pagesMTech QBRaj Kumar SinghNo ratings yet

- CS 2202 - Digital Principles and Systems DesignDocument3 pagesCS 2202 - Digital Principles and Systems DesignDhilip PrabakaranNo ratings yet

- Basics of COA: 1. (MCQ) (GATE-2023: 2M)Document69 pagesBasics of COA: 1. (MCQ) (GATE-2023: 2M)dzz9wt7x9kNo ratings yet

- Mca 1 Sem Computer Organization and Architecture Kca105 2022Document1 pageMca 1 Sem Computer Organization and Architecture Kca105 2022kimog66911No ratings yet

- QuestionBank 15012019Document14 pagesQuestionBank 15012019Mohammed RafaatNo ratings yet

- Digital Electronics and CircuitsDocument12 pagesDigital Electronics and CircuitsGuruKPONo ratings yet

- 07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrDocument8 pages07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrObula ReddyNo ratings yet

- UC 8th Edition Ejercicios y SolucionesDocument13 pagesUC 8th Edition Ejercicios y SolucionesMarcelo RodríguezNo ratings yet

- Signature of Invigilator, Examiner, Marks, NAME, ROLL NO, Logic Circuits MCQDocument4 pagesSignature of Invigilator, Examiner, Marks, NAME, ROLL NO, Logic Circuits MCQsreekantha2013No ratings yet

- Computer Architecture Objective Type Questions and AnswersDocument129 pagesComputer Architecture Objective Type Questions and AnswersRajesh TiwaryNo ratings yet

- Ca Q&aDocument129 pagesCa Q&aRavi TejaNo ratings yet

- CSA Test PaperDocument65 pagesCSA Test Paperhimanshumis2022No ratings yet

- Deld QB EndsemDocument4 pagesDeld QB EndsemUV New MoviesNo ratings yet

- Microprocessor, Interfacing and System Design Analog-to-Digital Converter ModuleDocument26 pagesMicroprocessor, Interfacing and System Design Analog-to-Digital Converter ModuleSani RakibulNo ratings yet

- BEM2053 EM218 - Assignment 03 - SolutionDocument8 pagesBEM2053 EM218 - Assignment 03 - SolutionAbdirisak AhmedNo ratings yet

- COA Question Bank With SolutionDocument145 pagesCOA Question Bank With SolutionSandeep Kumar YadavNo ratings yet

- Programs For Cso Lab 8085 SRGI-2017Document7 pagesPrograms For Cso Lab 8085 SRGI-2017Avinash GaurNo ratings yet

- Computer Architecture MCQ-4Document6 pagesComputer Architecture MCQ-4Kuldeep KushwahaNo ratings yet

- EE496B Controls Lab Position and Velocity Control DesignDocument2 pagesEE496B Controls Lab Position and Velocity Control Designkasun prabhathNo ratings yet

- Computer Architecture-OBJECTIVE TYPE 75 QUESTIONS-GateDocument8 pagesComputer Architecture-OBJECTIVE TYPE 75 QUESTIONS-GatepranavbommiNo ratings yet

- 346Document60 pages346Anjan SenguptaNo ratings yet

- Chap 06 Ans Part 2Document18 pagesChap 06 Ans Part 2Janelle Joyce MuhiNo ratings yet

- RRB Junior Electronics Engineer Study Material 3Document66 pagesRRB Junior Electronics Engineer Study Material 3thirumalNo ratings yet

- CEG 2136 - Fall 2017 - Final Exam SampleDocument14 pagesCEG 2136 - Fall 2017 - Final Exam SampleAmin DhouibNo ratings yet

- Dte QBDocument54 pagesDte QBitachisan973No ratings yet

- Computer Architecture 3rd Edition by Moris Mano CH 05Document35 pagesComputer Architecture 3rd Edition by Moris Mano CH 05Sadaf RasheedNo ratings yet

- Design of Control Unit: - Decoding Alu Control InformationDocument4 pagesDesign of Control Unit: - Decoding Alu Control InformationDawood MaNo ratings yet

- Sheet FourDocument3 pagesSheet FourRana BadranNo ratings yet

- MPMC MemoryDocument10 pagesMPMC Memoryswaroop1122100% (1)

- Nodia and Company: Model Test Paper - I Gate Digital ElectronicsDocument7 pagesNodia and Company: Model Test Paper - I Gate Digital Electronicsdwivedi89No ratings yet

- CMOS Lab Assignment-1 Digital Circuit Schematics and SimulationsDocument1 pageCMOS Lab Assignment-1 Digital Circuit Schematics and SimulationsDhaval ShuklaNo ratings yet

- Microprocessor 49 Important MCQDocument8 pagesMicroprocessor 49 Important MCQAawez AkhterNo ratings yet

- Chap 1Document32 pagesChap 1Vinothsaravanan RNo ratings yet

- Embedded Micro Controller Test SolutionDocument9 pagesEmbedded Micro Controller Test SolutionalikaastridNo ratings yet

- Sequential Circuit Design Using PLDsDocument8 pagesSequential Circuit Design Using PLDsJacob ChakoNo ratings yet

- 8085 Instruction SetDocument17 pages8085 Instruction SetLukeNo ratings yet

- Basic Computer Organization and DesignDocument35 pagesBasic Computer Organization and DesignVinay KumarNo ratings yet

- BC0046 Microprocessor MQPDocument20 pagesBC0046 Microprocessor MQPMeet PandyaNo ratings yet

- Be Winter 2020Document2 pagesBe Winter 2020SonuNo ratings yet

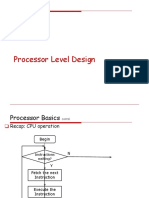

- 4 - Pocessor Level DesignDocument20 pages4 - Pocessor Level DesignJahid Fahim.No ratings yet

- CPU Organisation & Operation: Professor Kin K. Leung Heavily Based On Materials by Dr. Naranker DulayDocument25 pagesCPU Organisation & Operation: Professor Kin K. Leung Heavily Based On Materials by Dr. Naranker Dulayapi-19967001No ratings yet

- C-Language:) Configuration To Star Configuration. R R RDocument4 pagesC-Language:) Configuration To Star Configuration. R R Rthe crowNo ratings yet

- Lab 1Document11 pagesLab 1Maitha SaeedNo ratings yet

- Computer Applications and ManagementDocument11 pagesComputer Applications and ManagementParag PaliwalNo ratings yet

- IES - Electrical Engineering - MicroprocessorDocument31 pagesIES - Electrical Engineering - Microprocessors_subbulakshmiNo ratings yet

- QBank DPSD cs2202Document6 pagesQBank DPSD cs2202kunarajNo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- Introduction of G Drive - The Future of Z Drive - MandalayDocument25 pagesIntroduction of G Drive - The Future of Z Drive - MandalayHpone PainfNo ratings yet

- WHO CDS HIV 19.34 EngDocument4 pagesWHO CDS HIV 19.34 EngHpone PainfNo ratings yet

- National Intern (Roster), Multiple Positions: Background Information - MyanmarDocument7 pagesNational Intern (Roster), Multiple Positions: Background Information - MyanmarHpone PainfNo ratings yet

- WHO CDS HIV 19.34 EngDocument4 pagesWHO CDS HIV 19.34 EngHpone PainfNo ratings yet

- Nutrition and Diet Therapy 12Th Edition Roth Solutions Manual Full Chapter PDFDocument30 pagesNutrition and Diet Therapy 12Th Edition Roth Solutions Manual Full Chapter PDFgretchenmilesdxeh3100% (8)

- You Said It's Called Supreme Mathematics RightDocument2 pagesYou Said It's Called Supreme Mathematics RightAuMatu89% (9)

- Accounting for Inventory Valuation Methods Research ProposalDocument66 pagesAccounting for Inventory Valuation Methods Research ProposalAyman Ahmed Cheema100% (1)

- Candy Microwave OvenDocument31 pagesCandy Microwave OvencdimisNo ratings yet

- A Meta Analysis of Effectiveness of Interventions To I - 2018 - International JoDocument12 pagesA Meta Analysis of Effectiveness of Interventions To I - 2018 - International JoSansa LauraNo ratings yet

- Programme EnergyDocument9 pagesProgramme EnergyAbdulazizNo ratings yet

- Early Daoist Dietary Practices: Examining Ways To Health and Longevity. by Shawn ArthurDocument6 pagesEarly Daoist Dietary Practices: Examining Ways To Health and Longevity. by Shawn ArthurlsdkNo ratings yet

- Montageanleitung sf25 35 enDocument20 pagesMontageanleitung sf25 35 enPaulo santosNo ratings yet

- BonBonB What Map ReviewsDocument396 pagesBonBonB What Map Reviewstoyi kamiNo ratings yet

- Glover U Business Plan 2022 DigitalDocument25 pagesGlover U Business Plan 2022 DigitalJustin CarruthNo ratings yet

- Analie T. Caro: Personal ParticularsDocument4 pagesAnalie T. Caro: Personal ParticularsAnalie Tañamor CaroNo ratings yet

- HR Interview QuestionsDocument6 pagesHR Interview QuestionsnavneetjadonNo ratings yet

- Basic Sciences: Home MCQ's DiscussionsDocument10 pagesBasic Sciences: Home MCQ's Discussionsdileep9002392No ratings yet

- Frame Fit Specifications 2019 MTB Components Rev CDocument167 pagesFrame Fit Specifications 2019 MTB Components Rev Cpicko 86No ratings yet

- 5 Set Model Question Mathematics (116) MGMT XI UGHSSDocument13 pages5 Set Model Question Mathematics (116) MGMT XI UGHSSSachin ChakradharNo ratings yet

- Tentech MTD20KWe Digital Earth Tester Users Guide ManualDocument45 pagesTentech MTD20KWe Digital Earth Tester Users Guide ManualAnonymous voVeDickM100% (1)

- D117/D118 Service ManualDocument75 pagesD117/D118 Service ManualJohn JuquenNo ratings yet

- Invoice Being Charged Sued If or Violation Has This in Wrongful - RightfulDocument67 pagesInvoice Being Charged Sued If or Violation Has This in Wrongful - RightfulSteven SchoferNo ratings yet

- B2 - PlatoDocument1 pageB2 - PlatoVeda Leigh SyNo ratings yet

- Sample Action Research in MathDocument12 pagesSample Action Research in MathKresta BenignoNo ratings yet

- Latin Fathers On Spirit PDFDocument20 pagesLatin Fathers On Spirit PDFZakka LabibNo ratings yet

- MDD FormatDocument6 pagesMDD FormatEngineeri TadiyosNo ratings yet

- CS/CS/SB 1550: Prescription DrugsDocument49 pagesCS/CS/SB 1550: Prescription DrugsBrandon HoganNo ratings yet

- Appendix A. Second QuantizationDocument24 pagesAppendix A. Second QuantizationAgtc TandayNo ratings yet

- 3.0MP 4G Smart All Time Color Bullet Cam 8075Document2 pages3.0MP 4G Smart All Time Color Bullet Cam 8075IshakhaNo ratings yet

- Contineous Assessment 2 Group BDocument11 pagesContineous Assessment 2 Group BMasnoon MidhatNo ratings yet

- OSCEs For Dentistry Third Edition-With-AnswersDocument365 pagesOSCEs For Dentistry Third Edition-With-AnswersAnkita Arora100% (6)

- Quantum Dot PDFDocument22 pagesQuantum Dot PDFALI ASHRAFNo ratings yet

- SM6 Brochure PDFDocument29 pagesSM6 Brochure PDFkarani ninameNo ratings yet

- 3D Solar System With Opengl and C#Document4 pages3D Solar System With Opengl and C#Shylaja GNo ratings yet