Professional Documents

Culture Documents

Matching Dead Time to MOSFET Parameters in ZVS Circuits

Uploaded by

jean grangeonOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Matching Dead Time to MOSFET Parameters in ZVS Circuits

Uploaded by

jean grangeonCopyright:

Available Formats

VISHAY SILICONIX

www.vishay.com

Power MOSFETs Application Note AN845

Matching System Dead Time to MOSFET Parameters

in ZVS Circuits

by Sanjay Havanur

Medium- and high-voltage power MOSFETs are used in a variety of isolated converter topologies, such as half- or full-bridges

and single-ended boost and synchronous buck regulators. The bridges may be hard- or soft-switched; however, most of

today’s converters employ zero voltage switching (ZVS) to eliminate turn-on switching losses. The powertrain remains the same,

except the sequence in which devices are turned on and off needs to be modified. Synchronous buck converters, typically used

for front end pre-regulation in wide-input DC/DC brick converters, also switch the low-side MOSFET in ZVS mode. While the

hard switched bridges and boost converters do not have critical dead time requirements, all soft-switched ZVS bridges and

synchronous buck converters must operate within such limits. In low-voltage synchronous buck converters, the dead time

during the transitions between the low- and high-side MOSFETs is optimized by the controller or the driver. Shoot-through

protection is also implemented, either by sensing the falling edge of the gate drive or the switch node voltage. There are also

more sophisticated techniques that attempt to optimally adjust the delay on a continuous basis.

However, such fine tuning is not practical with higher-voltage drivers, so designers must fall back on fixed dead times during

transitions. Since long dead times lead to longer body diode conduction and a consequent loss of efficiency, it is always

desirable to provide an optimally minimized dead time without running into shoot-through conditions. This requires a detailed

understanding of the transition process and calculation of different intervals based on MOSFET and circuit parameters. While

optimum delays can be, and quite often are, determined empirically, analysis is necessary to account for variations and to

choose the right device for the highest efficiency. For an illustration of this analysis, in this article we will use a soft-switched full

bridge, which operates with a full duty ratio of 50 % per arm. Such a topology is also known as a DC transformer, and is popular

for generating an unregulated intermediate bus converter (IBC) output from a 48 VDC input. The concepts and parametric

tradeoffs discussed here can be extended to many other ZVS topologies as well.

Q1

ON

Tdt

Q2

ON

TXSR

Q4

Tdt ON

Q3

ON

APPLICATION NOTE

Ttrans =

+Vin

2x Tdt + TXSR

Transformer

Voltage

-Vin

Fig. 1 - Gate drive and transformer voltages in a full-duty ratio bridge

Revision: 06-Oct-14 1 Document Number: 67527

For technical questions, contact: powermosfettechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Application Note AN845

www.vishay.com

Vishay Siliconix

Matching System Dead Time to MOSFET Parameters

in ZVS Circuits

THE TRANSITION PROCESS

To start with, there are different ways to sequence a soft-switched full bridge, and each has its own benefits and pitfalls. One

particular sequence, where each transition is initiated by turning off the high-side MOSFET, is shown in Fig. 1. The flow of

current through different devices during the transition is shown in Fig. 2a through Fig. 2e. Initially Q1 and Q4 are conducting and

power is delivered to load (Fig. 2a). The transition is initiated by turning off Q1, and its current is diverted to the body diode of

Q2 (Fig. 2b). This interval lasts for Tdt.

Q1 Q3 Q1 Q3

Lpcb Lpcb

Llk + Llk +

T1

Vin Vin

+

SW1 +

LX1

- Ipri - Ipri LX2

SW2

Q2 Q4 Q2 Q4 T1

Fig. 2a - Q1 and Q4 are conducting Fig. 2b - Q1 is turned off and current is diverted to Q2

When Q1 is completely off, Q2 is turned on with ZVS. This is followed by a short duration (TXSR), during which the transformer

primary is shorted out and a magnetizing current circulates between the low-side MOSFETs (Fig. 2c). In phase-shifted bridge

converters, output regulation is achieved by varying the TXSR, but in DC transformers it is kept to a minimum. After the TXSR

delay, Q4 is turned off and the magnetizing current is diverted to Q3 (Fig. 2d). The transition is complete when Q3 is turned on

with ZVS after another interval of Tdt (Fig. 2e).

Q1 Q3

Lpcb Q1 Q3 Lpcb

Llk +

Llk +

Vin Vin

+ +

LX1

- Imag - Imag

LX2

Q2 Q4

T1 Q2 Q4 T1

ZVS Turn

ON for Q2

Fig. 2c - Q2 is turned on with ZVS Fig. 2d - Q4 is turned off and magnetizing current is diverted to

Q3

ZVS Turn

ON for Q3

APPLICATION NOTE

Lpcb Q1 Q3

Llk +

Vin

+ SW1

- Ipri SW2

Q2 Q4 T1

Fig. 2e - Q3 is turned on with ZVS

The total transition time is given by the equation Ttrans = 2 x Tdt + TXSR.

Revision: 06-Oct-14 2 Document Number: 67527

For technical questions, contact: powermosfettechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Application Note AN845

www.vishay.com

Vishay Siliconix

Matching System Dead Time to MOSFET Parameters

in ZVS Circuits

The interval TXSR is not critical to the primary transition; it can be zero in theory. However, a minimum value is demanded by the

secondary synchronous rectifier. If output rectifiers are replaced by synchronous MOSFETs, their drive signals must toggle

during the TXSR dead band. This is true whether SSRs are self driven or control driven; the secondary drive pulses are matched

to the primary in both cases. The only difference is that in a self-driven scheme, TXSR needs to be higher since the transformer

secondary rise and fall times are much slower. Another factor to consider is that High → Low and Low → High transitions are

not symmetric with IC-based gate drivers, which may add a delay during the level shifting of the input signals. This is different

from, and in addition to, the normal propagation delay through the drive stages. The level shift delay reduces available dead

time even further during H → L transitions, but is actually beneficial during L → H transitions and increases available dead time.

Most drivers try to match the total delays within a few nanoseconds, but the difference, denoted as TLSH, needs to be taken into

account.

It is clear that ZVS turn-on is achieved only if, within the available dead time Tdt,

a) The gate capacitance of the outgoing MOSFET is discharged to below Vth, and

b) The output capacitor of the incoming MOSFET is fully discharged close to zero.

Fig. 3 shows the simplified gate turn-off circuit used in the analysis. Since all capacitances are functions of VDS, the equivalent

charge specifications will be used in the calculations. There are three distinct stages for the gate discharge, as shown in Fig. 4.

Vgss

Rgoff = Crss L Qsw

Rg + Rgext + Rsink

+

Vgp

Vin

Rgext Rg

Rsink V th

Toff

Ciss

Igoff MOSFET

Driver

TGSP TGPT

T0 T1 T2 T3 T4

Fig. 3 - Simplified gate drive circuit Fig. 4 - Gate turn-off voltage and time intervals

T0 - T1: Ciss is discharged from the gate supply voltage VGSS to plateau Vgp, assuming constant turn-off current. During this

interval the Igoff current is limited by the drive capability rather than gate resistors

T1 - T2: Conventional plateau time where VDS rises to VIN and beyond due to ringing. The gate current is now limited by the

APPLICATION NOTE

total resistance in the gate loop

T2 - T3: Current fall time in the outgoing MOSFET

The three intervals can be calculated using the equations:

V gss – V gp Q sw

T GSP = C iss0 × --------------------------- T GPT = R igoff × ----------- R goff = R g + R ext + R sin k

I goff V gp

Revision: 06-Oct-14 3 Document Number: 67527

For technical questions, contact: powermosfettechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Application Note AN845

www.vishay.com

Vishay Siliconix

Matching System Dead Time to MOSFET Parameters

in ZVS Circuits

The value Ciss0 used for TGSP is not from the datasheet tables, but at VDS = 0 V, when the MOSFET is fully on. For ultra-low

RDS(on) MOSFETs with extremely high cell densities, trench gates, and charge balancing structures, Ciss0 can be 4 times to

5 times higher than the Ciss specified at mid voltage. There is no power loss, but this interval can eat up a major part of the

available dead time. The formula for TGPT defines the sum of voltage rise time and current fall time during turn-off based on the

drive conditions. But this is an inadequate approximation, since the current fall time depends on a number of external

parameters such as PCB trace inductance, the source inductance of the package, and the input voltage. These factors

dominate the di/dt of the primary loop current over gate drive. However, the focus here is on achieving zero voltage status for

the incoming MOSFET, which may be determined using another approach. As the current in the high-side MOSFET goes to

zero, the same is taken up by its complement on the low side. This enables a simple estimate of the time required to discharge

the output capacitance as one quarter of one resonant cycle of LPCB and Coss,

π L PCB × Q oss

T DSD = --- × --------------------------------

-

2 V IN

It is assumed that the PCB trace inductance is much smaller than the leakage inductance Llk, and during TDSD the transformer

loop current does not change. With this we are in a position to state the complete timing requirement for the dead time Tdt,

T dt ≥ T LSH + T GSP + T GPT + T DSD

This final result is somewhat conservative for devices with high Vth values. The higher rise time needed before gate voltage can

reach Vth adds to the dead time.

TEST RESULTS ON IBC CONVERTER

The above analysis was verified with the SiR882ADP high-performance MOSFET targeted for high-frequency DC/DC

converters. The relevant specifications of the device are shown in Table 1. The test platform was a 48 V to 9.6 V IBC converter

operating at 200 kHz. The original design set the dead time at 20 ns. From the Table 1 values, it is clear that this dead time is

quite insufficient.

TABLE1: DEADTIME CALCULATIONS FOR SiR882ADP

SiR882ADP CIRCUIT PARAMETERS

RDS(on) 7.4 mΩ VIN 48

V

Ciss 1975 Vges 10

pF

Ciss0 4500 Igoff 2 A

Qsw 9.8 LPCB 20 nH

nC

Qoss 64 Rsink 2

Vgp 3 V Rgext 2 Ω

APPLICATION NOTE

Rg 1 Ω Rgoff 5

TGSP 15.75 TLSH 10

ns ns

TGPT 16.2 TDSD 8.11

Fig. 5a to Fig. 5c show the switching node waveforms for three different dead times: 50 ns, 75 ns, and 20 ns. Fig. 6 shows the

power loss of the entire converter as a function of different dead times. Optimal switching with minimum loss occurs at a dead

time of 50 ns, as calculated. At 20 ns, the low-side MOSFET is turned on with the switch node voltage at VIN, resulting in

shoot-through losses. While the waveforms at 75 ns look clean and offer an extra safety margin, the duration of diode

conduction also increases. Fig. 6 shows its impact: diode losses steadily adding up with increasing current.

Revision: 06-Oct-14 4 Document Number: 67527

For technical questions, contact: powermosfettechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Application Note AN845

www.vishay.com

Vishay Siliconix

Matching System Dead Time to MOSFET Parameters

in ZVS Circuits

Loss Comparison at Vin = 48 V

14

SiR882A in IBC Converter

SiR882A at 20 ns

12 SiR882A at 75 ns

SiR882A at 50 ns

10

Loss (W)

8

2

0 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30

Load Current (A)

Fig. 5a - Switching waveforms at a dead time of 50 ns Fig. 6 - Total loss as a function of dead time

SiR882 Efficiency Comparison at Vin = 48V

96.5 %

96.0 %

95.5 %

95.0 %

Efficiency

94.5 %

94.0 %

SiR882A at 20 ns

93.5 % Sample H at 20 ns

93.0 % Sample F at 20 ns

SiR882A at 50 ns

92.5 %

0 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30

Load Current (A)

Fig. 5b - Switching waveforms at a dead time of 75 ns Fig. 7 - System efficiency comparison

APPLICATION NOTE

Fig. 5c - Switching waveforms at a dead time of 20 ns

Revision: 06-Oct-14 5 Document Number: 67527

For technical questions, contact: powermosfettechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Application Note AN845

www.vishay.com

Vishay Siliconix

Matching System Dead Time to MOSFET Parameters

in ZVS Circuits

DILIGENCE BEFORE DROP IN

It is quite common for designers to try out a promising new part in an existing design. It is also equally common to do this by

just dropping in the new part in place of the existing one and run an automated efficiency test program. Unfortunately, the results

are almost never reliable. As seen above, the power losses are quite dependent on how well the dead time is matched to the

device characteristics. Modern trench devices with dense cell structures offer the benefit of very low RDS(on), but also come with

larger Ciss0, Qgd, and Qoss values. While they offer better figure of merit (FOM) and improved efficiencies, designers need to fine

tune their circuits to realize their full potential. Evaluating them by dropping devices into existing circuits, without regard to

individual switching characteristics, can lead to misleading results and prevent designers from choosing a better solution to

improve overall performance.

This can be further illustrated by comparing three different devices in the same circuit. Table 2 shows the calculated optimum

dead times for the SiR882ADP MOSFET against two other samples. Fig. 7 shows the measured efficiency of all devices at

different dead times. Sample H was the original device used in the IBC converter with a dead time of 20 ns. It has the highest

gate threshold voltage Vth and is more immune to shoot-through even with reduced dead times. Both the lower RDS(on) devices

show worse efficiency simply because they were dropped into a circuit that was not designed for them. With nearly half the

RDS(on), sample F shows only marginally better efficiency performance; until about 50 % of the load, it is actually worse than the

highest RDS(on) competitor. The SiR882ADP also comes off much worse at 20 ns, but at the optimum value of 50 ns

demonstrates its benefits.

TABLE 2: COMPARISON OF COMPETITIVE DEVICES

MOSFET PART NUMBER SAMPLE H SAMPLE F SiR882ADP UNIT

Typical RDS(on) 12 6.3 7.2 mΩ

Calculated Optimum Dead Time 38.3 38.9 50.1 ns

CONCLUSIONS

Unlike hard-switched converters, ZVS designs like IBC or phase-shifted bridges must work under strict dead time limits during

switching transitions. Insufficient dead time during turn off can result in the loss of ZVS, poor efficiency, and in the worst case,

failure of the device due to shoot-through. The minimum dead time required varies from one device technology to another, even

when they all come from the same manufacturer, but can be easily calculated from the published device parameters. Dead time

optimization based on the analysis presented here can help to exploit the advances in device technology and achieve better

performance even from legacy designs.

APPLICATION NOTE

Revision: 06-Oct-14 6 Document Number: 67527

For technical questions, contact: powermosfettechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

You might also like

- QSC K8 K10 K12 KSub Service ManualDocument70 pagesQSC K8 K10 K12 KSub Service Manualboroda2410100% (7)

- QSC Audio Product Document Title Under 40 CharactersDocument8 pagesQSC Audio Product Document Title Under 40 Charactersjean grangeonNo ratings yet

- QSC k8 k10 k12 Ksub K Series SCHDocument22 pagesQSC k8 k10 k12 Ksub K Series SCHOscar Pacheco100% (4)

- An010 en PDFDocument15 pagesAn010 en PDFAnonymous Z1RHn9ENo ratings yet

- L6565 Quasi-Resonant Controller: November 2002Document35 pagesL6565 Quasi-Resonant Controller: November 2002Alberto MontillaNo ratings yet

- DC-DC Fast Input Slew RateDocument6 pagesDC-DC Fast Input Slew RateCarlos Agorreta ZafraNo ratings yet

- AN-H58 Improving The Efficiency of A HV9930/AT9933 Controlled Boost-Buck ConverterDocument3 pagesAN-H58 Improving The Efficiency of A HV9930/AT9933 Controlled Boost-Buck ConverterJohnNo ratings yet

- Practical Circuitry For Measurement and Control ProblemsDocument40 pagesPractical Circuitry For Measurement and Control Problemsf_hayatiNo ratings yet

- Evaluation of TCM and CRCM Modulation For Totem Pole PFCDocument7 pagesEvaluation of TCM and CRCM Modulation For Totem Pole PFCMuhammad Arsalan FarooqNo ratings yet

- Chapter 7 Multi Vibrators and Wave Shaping CircuitsDocument8 pagesChapter 7 Multi Vibrators and Wave Shaping CircuitsJibril JundiNo ratings yet

- AN149f PDFDocument22 pagesAN149f PDFranjitheee1292No ratings yet

- TPS55340-Q1 Integrated 5-A, Wide Input Range Boost, SEPIC, or Flyback DC/DC ConverterDocument37 pagesTPS55340-Q1 Integrated 5-A, Wide Input Range Boost, SEPIC, or Flyback DC/DC ConverterMario RossiNo ratings yet

- Features Description: LTC7004 Fast 60V High Side NMOS Static Switch DriverDocument19 pagesFeatures Description: LTC7004 Fast 60V High Side NMOS Static Switch DriverLim VanthienNo ratings yet

- GAST - Gas Turbine Governor: LO1 Max Min Switch1 DF/DT 0Document4 pagesGAST - Gas Turbine Governor: LO1 Max Min Switch1 DF/DT 0MarcosNo ratings yet

- DC-DC ConvertersDocument134 pagesDC-DC ConvertersBELAJI BASIMNo ratings yet

- Basics of electric locomotive power and systemDocument23 pagesBasics of electric locomotive power and systemAshutosh Pandey100% (1)

- HV7355DB1 150V, 1.5A, Unipolar Ultrasound Pulser Demoboard: General DescriptionDocument9 pagesHV7355DB1 150V, 1.5A, Unipolar Ultrasound Pulser Demoboard: General DescriptionAhmed YasserNo ratings yet

- 110kV transmission line bill of materialDocument10 pages110kV transmission line bill of materialTuấn Anh NguyễnNo ratings yet

- Sboa 313 ADocument6 pagesSboa 313 AKaushlendra KumarNo ratings yet

- Non-Inverting Comparator With Hysteresis Circuit: Analog Engineer's Circuit: AmplifiersDocument6 pagesNon-Inverting Comparator With Hysteresis Circuit: Analog Engineer's Circuit: AmplifiersmohamadziNo ratings yet

- Relaxation Oscillator Circuit: Analog Engineer's Circuit: AmplifiersDocument5 pagesRelaxation Oscillator Circuit: Analog Engineer's Circuit: AmplifiersMammeri ElhachemiNo ratings yet

- Standard Linear and Logic Computing Solutions: David YaegerDocument92 pagesStandard Linear and Logic Computing Solutions: David Yaegersluz2000000No ratings yet

- TL032CDocument63 pagesTL032Cameer_jaburNo ratings yet

- Mi21mtech11003 - BM5023 - 2021 - Lab 2Document7 pagesMi21mtech11003 - BM5023 - 2021 - Lab 2Subhranil RoyNo ratings yet

- TL2843B Q1 etcTIDocument18 pagesTL2843B Q1 etcTIrahma jayaNo ratings yet

- LM 5010Document32 pagesLM 5010ed251No ratings yet

- How To Measure The Control Loop of DCS-Control™ DevicesDocument5 pagesHow To Measure The Control Loop of DCS-Control™ DevicesZamfirMarianNo ratings yet

- Slua 923Document10 pagesSlua 923david reyesNo ratings yet

- Click To Add Text Click To Add TextDocument23 pagesClick To Add Text Click To Add TextNoor SabaNo ratings yet

- Opamp TIDocument5 pagesOpamp TIAmogh Gajaré100% (1)

- How To Reduce Current Spikes at AC Zero-Crossing For Totem-Pole PFCDocument6 pagesHow To Reduce Current Spikes at AC Zero-Crossing For Totem-Pole PFCdiablo diablolordNo ratings yet

- H2PToday1806_design_TexasInstruments_Part 5Document10 pagesH2PToday1806_design_TexasInstruments_Part 5lcisnydeksdtaujutlNo ratings yet

- New IHR IGBT TechnologyDocument4 pagesNew IHR IGBT TechnologyvittorioNo ratings yet

- Tps 24713Document40 pagesTps 24713zomya kulkarniNo ratings yet

- Circuit Idea 20211104Document2 pagesCircuit Idea 20211104Nilay Ceren ÖZTÜRKNo ratings yet

- Answitch PDFDocument16 pagesAnswitch PDFAshok KumarNo ratings yet

- Module-3 (DC Chopper)Document76 pagesModule-3 (DC Chopper)Prasann KatiyarNo ratings yet

- L6565 Quasi-Resonant ControllerDocument28 pagesL6565 Quasi-Resonant ControllerboipouNo ratings yet

- Design Considerations Bidirectional DC DC ConvertersDocument9 pagesDesign Considerations Bidirectional DC DC ConvertersHernandaBudiSantosoNo ratings yet

- Biasing Requirements For TXS, TXB, and LSF Auto-Bidirectional TranslatorsDocument7 pagesBiasing Requirements For TXS, TXB, and LSF Auto-Bidirectional TranslatorsspotNo ratings yet

- Totem-Pole Paper - 0Document9 pagesTotem-Pole Paper - 0wartchev39No ratings yet

- CircuitsDocument41 pagesCircuitsriajulNo ratings yet

- Practical Feedback Loop Design Considerations For Flyback Converter Using UCC28740Document7 pagesPractical Feedback Loop Design Considerations For Flyback Converter Using UCC28740jay lowkeyNo ratings yet

- DC Motor Drive: Power ElectronicsDocument19 pagesDC Motor Drive: Power ElectronicsRishabh MalpotraNo ratings yet

- Design high frequency push-pull DC/DC converterDocument5 pagesDesign high frequency push-pull DC/DC converterEdoardoNo ratings yet

- LM25085A 42V Constant On-Time PFET Buck Switching Controller With 0.9V ReferenceDocument31 pagesLM25085A 42V Constant On-Time PFET Buck Switching Controller With 0.9V ReferenceStuxnetNo ratings yet

- AN017 Switching Mode Power SupplyDocument6 pagesAN017 Switching Mode Power SupplyHerbert LopesNo ratings yet

- T 10-B Lvds T V: Riple IT Ransmitter FOR IdeoDocument11 pagesT 10-B Lvds T V: Riple IT Ransmitter FOR IdeoDavid MontielNo ratings yet

- Application Note AN-1121: Practical Layout For Current Sensing Circuit of IRMCF300 Series ICDocument14 pagesApplication Note AN-1121: Practical Layout For Current Sensing Circuit of IRMCF300 Series ICHaris AmrullahNo ratings yet

- LT1016Document20 pagesLT1016api-3825669No ratings yet

- Jeong2015 PDFDocument4 pagesJeong2015 PDFAli ErNo ratings yet

- Possible Ways To Add Resonant Components To The PWM Switch Cell: Classification of Resonant-Switch ConvertersDocument11 pagesPossible Ways To Add Resonant Components To The PWM Switch Cell: Classification of Resonant-Switch ConvertersdjyNo ratings yet

- On Load Single Phase Solid State Tap ChangerDocument5 pagesOn Load Single Phase Solid State Tap ChangerArmandinho CaveroNo ratings yet

- High Efficiency 10A Synchronous Buck Converter: Features General DescriptionDocument2 pagesHigh Efficiency 10A Synchronous Buck Converter: Features General DescriptionDanielle ButlerNo ratings yet

- Isl6115a DST 20040317Document10 pagesIsl6115a DST 20040317Muhammad Januar SusantoNo ratings yet

- Chapter 5 MultivibratorsDocument9 pagesChapter 5 MultivibratorsRofiq NuryakinNo ratings yet

- Power Supply Trainer Using Lm723 IcDocument8 pagesPower Supply Trainer Using Lm723 IcDinesh Kumar MehraNo ratings yet

- AN4104 Forward Converter Type PC SMPS With FPS: Sangtae-Im PD DivisionDocument17 pagesAN4104 Forward Converter Type PC SMPS With FPS: Sangtae-Im PD DivisionJose Miguel Rodriguez CarreñoNo ratings yet

- Diseño output ripple en DCDCDocument10 pagesDiseño output ripple en DCDCherraezjorge8No ratings yet

- ECN3297TF HitachiDocument17 pagesECN3297TF HitachiachillesNo ratings yet

- Troubleshooting TCD Codes for MUSE ED InvertersDocument11 pagesTroubleshooting TCD Codes for MUSE ED InvertersMoises PerelloNo ratings yet

- AN1059Document20 pagesAN1059rlevrinoNo ratings yet

- Battery Cell Balancing GuideDocument8 pagesBattery Cell Balancing GuidelitieuduyNo ratings yet

- Switching FETs and the Importance of Dead Time ControlDocument3 pagesSwitching FETs and the Importance of Dead Time Controljean grangeonNo ratings yet

- Understanding Dead-Time Based On TPS51225/275/285: Application ReportDocument10 pagesUnderstanding Dead-Time Based On TPS51225/275/285: Application Reportjean grangeonNo ratings yet

- IR Audio Product GuideDocument8 pagesIR Audio Product Guidejean grangeonNo ratings yet

- DC to DC Converter Circuit 1400W Using SG3525 ICDocument2 pagesDC to DC Converter Circuit 1400W Using SG3525 ICjean grangeonNo ratings yet

- Infineon AN1198 BridgingDocument12 pagesInfineon AN1198 Bridgingjean grangeonNo ratings yet

- IRFI4024H-117P: DescriptionDocument6 pagesIRFI4024H-117P: Descriptionjean grangeonNo ratings yet

- IRF DatasheetDocument7 pagesIRF DatasheetJohn ForeroNo ratings yet

- MAX220-MAX249 +5V-Powered, Multichannel RS-232 Drivers/ReceiversDocument39 pagesMAX220-MAX249 +5V-Powered, Multichannel RS-232 Drivers/ReceiversHugo SantanaNo ratings yet

- Irfi4212h 117pDocument7 pagesIrfi4212h 117pAbdul KurniadiNo ratings yet

- Irfi4212h 117pDocument7 pagesIrfi4212h 117pAbdul KurniadiNo ratings yet

- Philips G90-AEDocument9 pagesPhilips G90-AEaulin64_845645735No ratings yet

- Infineon Irs20957spbf Ds v01 02 enDocument18 pagesInfineon Irs20957spbf Ds v01 02 enLindomar ChavesNo ratings yet

- Schematic - TOTEMPOLE BALAP - Sheet - 1 - 20190930201614Document1 pageSchematic - TOTEMPOLE BALAP - Sheet - 1 - 20190930201614jean grangeonNo ratings yet

- LED circuit board component layoutDocument1 pageLED circuit board component layoutjean grangeonNo ratings yet

- Philips G90-AEDocument9 pagesPhilips G90-AEaulin64_845645735No ratings yet

- Iraudamp6: 250W/8 X 2 Channel Class D Audio Power Amplifier Using The IRS20957S and IRF6785Document46 pagesIraudamp6: 250W/8 X 2 Channel Class D Audio Power Amplifier Using The IRS20957S and IRF6785jean grangeonNo ratings yet

- Specification IC DK124 PDFDocument7 pagesSpecification IC DK124 PDFordamNo ratings yet

- VIPER22ADocument15 pagesVIPER22ACleber MouraNo ratings yet

- Philips G90-AEDocument9 pagesPhilips G90-AEaulin64_845645735No ratings yet

- Umwd 06516a XDHDocument3 pagesUmwd 06516a XDHИван ФиличевNo ratings yet

- Wireless Remote Control for Underwater VehiclesDocument32 pagesWireless Remote Control for Underwater Vehiclesajacks504No ratings yet

- Modbus Hexadecimal Address (Master) - RTU / ASCII Mode Delta A. HMI Factory SettingsDocument2 pagesModbus Hexadecimal Address (Master) - RTU / ASCII Mode Delta A. HMI Factory SettingsryoNo ratings yet

- Multimedia - LECTURE 3Document37 pagesMultimedia - LECTURE 3Hemed hafidhNo ratings yet

- Faw1 PDFDocument2 pagesFaw1 PDFSavita BhabhiNo ratings yet

- Internship Report ModelDocument3 pagesInternship Report Modelo7bu046No ratings yet

- Wimax Is Defined As Worldwide Interoperability For Microwave Access by TheDocument27 pagesWimax Is Defined As Worldwide Interoperability For Microwave Access by Thensharanab4No ratings yet

- Phone Genesys ConfigurationDocument22 pagesPhone Genesys ConfigurationRodolfo TobiasNo ratings yet

- 11.2.1 Packet Tracer - Configure and Verify eBGP - ILM TraducidoDocument4 pages11.2.1 Packet Tracer - Configure and Verify eBGP - ILM TraducidoCrisgamerGDNo ratings yet

- IoT barriers agricultureDocument6 pagesIoT barriers agricultureSatyam BhardwajNo ratings yet

- Annex F - VHF Antenna - MD70-SRT-NTYPE DataDocument2 pagesAnnex F - VHF Antenna - MD70-SRT-NTYPE DataAhmed EidNo ratings yet

- SCADAPack 470 User ManualDocument134 pagesSCADAPack 470 User ManualLászló LósNo ratings yet

- Technical Manual - C&C08 Digital Switching System Chapter 2 OverviewDocument19 pagesTechnical Manual - C&C08 Digital Switching System Chapter 2 OverviewSamuel100% (2)

- (Nokia) MoP NB Over TDMDocument20 pages(Nokia) MoP NB Over TDMKiar JuniorNo ratings yet

- Service LIS2-ADocument11 pagesService LIS2-ASmart BiomedicalNo ratings yet

- PDVD700 Portable DVD Player Quickstart GuideDocument19 pagesPDVD700 Portable DVD Player Quickstart GuideGavinNo ratings yet

- Indian Institute of Information Technology Tiruchirappalli Department of Electronics and Communication EngineeringDocument3 pagesIndian Institute of Information Technology Tiruchirappalli Department of Electronics and Communication EngineeringANITHA MNo ratings yet

- WLAN Physical Layer (Including Wireless Ethernet Frame Structure)Document23 pagesWLAN Physical Layer (Including Wireless Ethernet Frame Structure)Sandy ZakariaNo ratings yet

- Master'S Thesis: Performance Measurements of Bluetooth 5 Technique Under InterferenceDocument59 pagesMaster'S Thesis: Performance Measurements of Bluetooth 5 Technique Under InterferenceГеорги НасковNo ratings yet

- Fisa Tehnica Camera Supraveghere IP Wireless Dahua IPC-HFW1435S-W 4 MP IR 30 M 2.8 MM 16x 1Document2 pagesFisa Tehnica Camera Supraveghere IP Wireless Dahua IPC-HFW1435S-W 4 MP IR 30 M 2.8 MM 16x 1DanielTeglasNo ratings yet

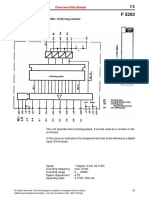

- Overview Data Sheets: F 5203: 14 Bit Ring CounterDocument2 pagesOverview Data Sheets: F 5203: 14 Bit Ring CountermohamadziNo ratings yet

- EMC Troubleshooting KitDocument6 pagesEMC Troubleshooting KitDirkNo ratings yet

- Cta12 14 BomDocument6 pagesCta12 14 BomIstván GerencsérNo ratings yet

- Nokia VoLTE Lessons From The Field White PaperDocument7 pagesNokia VoLTE Lessons From The Field White PaperBeliever0% (2)

- Huawei BTS 3900 Technical DescriptionDocument212 pagesHuawei BTS 3900 Technical DescriptionKrishanth Ppt87% (15)

- 114A4993 My Home Bridge ChamberlainDocument12 pages114A4993 My Home Bridge ChamberlainmichelleNo ratings yet

- Home Modem - Internet - Installation - Guide - CGN-RESDocument8 pagesHome Modem - Internet - Installation - Guide - CGN-RESAnthony HansonNo ratings yet

- FRENZEL3E - INSTRUCTORS MANUAL PartC - 01Document48 pagesFRENZEL3E - INSTRUCTORS MANUAL PartC - 01americo079No ratings yet

- ECE216Document2 pagesECE216Aryan GourNo ratings yet

- Ale Edi IdocDocument4 pagesAle Edi IdocPILLINAGARAJUNo ratings yet