Professional Documents

Culture Documents

Mse2 Vlsid 18

Mse2 Vlsid 18

Uploaded by

WARRIOR GamingOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Mse2 Vlsid 18

Mse2 Vlsid 18

Uploaded by

WARRIOR GamingCopyright:

Available Formats

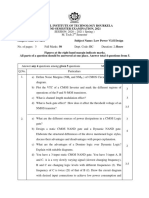

URR-14 “Write your Roll number”

KAKATIYA INSTITUTE OF TECHNOLOGY & SCIENCE, WARANGAL-506015

(An Autonomous Institute under Kakatiya University, Warangal)

B.Tech. (E&I Engg) VI Semester

Mid Semester Examination-II

U14EI604: VLSI DESIGN

Date: 18.04.2019 Note: 1. Answer all the questions.

Time: 2 Hrs] [Max. Marks: 25

Marks CDLL CO

1 Answer the following in brief.

a What is scaling. What factors can be improved with scaling? 1 R CO3

2 U CO3

b What are the advantages of switch logic. Differentiate between transmission

gates and pass transistors.

2 U CO3

c Implement a 4:1 MUX using Pass transistors. Draw the stick diagram.

d Differentiate between Verilog HDL and VHDL. 1 U CO4

1 R CO4

e List out the levels of abstraction used in Verilog.

2 a Explain (i) Sheet resistance (ii)Standard unit of capacitance and (iii) Delay Unit 3 U CO2

3 Ap CO2

b Discuss about inverter delays and derive expressions for rise and fall times for

a CMOS inverter.

(OR)

c List out different types of scaling models. Explain the effect of scaling on 3 Ap CO3

various device parameters of a MOSFET.

d What are the limits of miniaturization? Discuss about limits of interconnect and 3 U CO3

contact resistance.

3 U CO3

3 a Discuss the architectural issues and guide lines for a Subsystem design.

b Develop the structured design for a Parity Generator and show the circuit and 3 Ap CO3

stick diagrams.

(OR)

c Explain pseudo nMOS and dynamic CMOS logics. 3 U CO3

d Develop the structured design of Bus Arbitration Logic for n-line bus with 3 Ap CO3

relevant block, circuit and stick diagrams for leaf cell.

3 C CO4

4 a Write the Verilog description for a 4 bit ripple carry full adder. Also write the

test bench.

3 C CO4

b Implement a 4:1 MUX using AND, OR and NOT gates. Write the Verilog code

for the same. Also write the stimulus model.

(OR)

c Write the Verilog code for a 4bit ripple counter in Verilog. 3 C CO4

3 C CO4

d What is switch level modeling? Write the switch level Verilog description for a

2 input CMOS NAND gate.

---Question Paper Ends---

Paper set by: Prof. K. Sivani

Page 1 of 1

You might also like

- CXC Paper January 2015 AnswersDocument11 pagesCXC Paper January 2015 AnswersKimoy EdwardsNo ratings yet

- Supw QuestionsDocument8 pagesSupw QuestionsArpita Goyal100% (1)

- Chandigarh: TH THDocument3 pagesChandigarh: TH THAneezNo ratings yet

- S.Y. B.Tech. (Computer Science & Engineering) : End Semester Examination, December-2021Document1 pageS.Y. B.Tech. (Computer Science & Engineering) : End Semester Examination, December-2021A.K. GamingNo ratings yet

- New Horizon College of Engineering, Bangalore: 19CSE33 USNDocument12 pagesNew Horizon College of Engineering, Bangalore: 19CSE33 USNAhmad RazaNo ratings yet

- VLSI Assignment 3Document2 pagesVLSI Assignment 3RIONA RACHEL JACOBNo ratings yet

- VLSI DesignDocument5 pagesVLSI DesignqwertyuiopNo ratings yet

- National Institute of Technology Rourkela End Semester Examination, 2021Document3 pagesNational Institute of Technology Rourkela End Semester Examination, 2021ajay vermaNo ratings yet

- Kamala Institute of Technology & Science, Singapur Iv B.Tech I Sem 1 Mid ExaminationDocument1 pageKamala Institute of Technology & Science, Singapur Iv B.Tech I Sem 1 Mid ExaminationKarthik NasaniNo ratings yet

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- Vlsi QP 21,22Document11 pagesVlsi QP 21,22Arunitha ArulnathanNo ratings yet

- Signal 2Document2 pagesSignal 2imvuuser1No ratings yet

- VLSIDesignDocument5 pagesVLSIDesignVenkatesh KolatiNo ratings yet

- 523 BA19 Ad 01Document5 pages523 BA19 Ad 01ramesh1926No ratings yet

- CS 801D PDFDocument4 pagesCS 801D PDFarnab paulNo ratings yet

- See Cmos Vlsi Jan 2020Document3 pagesSee Cmos Vlsi Jan 20201ms21ec132No ratings yet

- See Cmos VlsiDocument2 pagesSee Cmos Vlsi1ms21ec132No ratings yet

- Iat2 QB CNDocument3 pagesIat2 QB CNkpkarthi80No ratings yet

- Rns Institute of Technology: Electronics and Communication EngineeringDocument1 pageRns Institute of Technology: Electronics and Communication EngineeringVinaykumar ANo ratings yet

- 21EC45T Control SystemDocument7 pages21EC45T Control SystemM.N.MD. FaheemNo ratings yet

- Mca 3 Sem Computer Network Kca303 2022Document2 pagesMca 3 Sem Computer Network Kca303 2022happyrobinsinghNo ratings yet

- Instrumentation II (EX602)Document18 pagesInstrumentation II (EX602)Akashman ShakyaNo ratings yet

- CS3351 - ModelDocument2 pagesCS3351 - Modelrkkumar07No ratings yet

- E ( (Caqsd CCN: G Mox - Mor Ks - E 3 HoursDocument7 pagesE ( (Caqsd CCN: G Mox - Mor Ks - E 3 HourssarveshNo ratings yet

- Cmos - Vlsi - Jan 2023Document2 pagesCmos - Vlsi - Jan 20231ms21ec132No ratings yet

- Microprocessor Aktu Sem 3 CT 1 KecDocument1 pageMicroprocessor Aktu Sem 3 CT 1 KecLakshitNo ratings yet

- Computer Networks (Cse252) 2022-23Document2 pagesComputer Networks (Cse252) 2022-23Snorlax2LazyNo ratings yet

- 54102-mt - Analog & Digital Ic DesignDocument2 pages54102-mt - Analog & Digital Ic DesignSRINIVASA RAO GANTANo ratings yet

- Mohamed Sathak A J College of Engineering: Assessment - II Exam EC6701Document3 pagesMohamed Sathak A J College of Engineering: Assessment - II Exam EC6701formyphdNo ratings yet

- Guru Nanak Institutions Technical Campus (Autonomous) : Question Bank With Blooms Taxonomy Level (BTL)Document3 pagesGuru Nanak Institutions Technical Campus (Autonomous) : Question Bank With Blooms Taxonomy Level (BTL)sahithikocharlakotaNo ratings yet

- Delay: Introduction To CMOS VLSI DesignDocument54 pagesDelay: Introduction To CMOS VLSI DesignHuy TranNo ratings yet

- Embedded System DesignDocument23 pagesEmbedded System DesignlosssssssssNo ratings yet

- 2017 Comp 204Document2 pages2017 Comp 204didow36570No ratings yet

- NR-221103 - Digital Circuits Design and ApplictionDocument5 pagesNR-221103 - Digital Circuits Design and ApplictionSrinivasa Rao G100% (1)

- Electronics: TelecommunicationDocument2 pagesElectronics: TelecommunicationSandhya GaikwadNo ratings yet

- WC QPDocument3 pagesWC QPsanthoshNo ratings yet

- r05410207 Vlsi DesignDocument7 pagesr05410207 Vlsi Design9010469071No ratings yet

- BCS302 Set 2Document2 pagesBCS302 Set 2megumifushiguru999No ratings yet

- C G1056 Pages: 3: Answer All Questions, Each Carries 4 MarksDocument3 pagesC G1056 Pages: 3: Answer All Questions, Each Carries 4 MarksCigi ManojNo ratings yet

- 18EI56Document6 pages18EI56Rocky BhaiNo ratings yet

- COA Question Bank - CO MappingDocument3 pagesCOA Question Bank - CO MappingKomalNo ratings yet

- Low Complexity Design of Ripple Carry and Brent-Kung Adders in QCADocument15 pagesLow Complexity Design of Ripple Carry and Brent-Kung Adders in QCATào TháoNo ratings yet

- 16BT70408 - Low Power Cmos Vlsi DesignDocument1 page16BT70408 - Low Power Cmos Vlsi DesignS KkNo ratings yet

- EE3601 - P&S - IAT-II - III Year EEEDocument4 pagesEE3601 - P&S - IAT-II - III Year EEEAravinth SankarNo ratings yet

- Digital ElectronicsDocument7 pagesDigital ElectronicsAlakaaa PromodNo ratings yet

- WSN Question Bank For Mid 1Document6 pagesWSN Question Bank For Mid 1praneetha ChowdaryNo ratings yet

- Code No: R05320402Document4 pagesCode No: R05320402chvsrsettiNo ratings yet

- Ec 703 2019-20Document2 pagesEc 703 2019-202000520310061No ratings yet

- MSE IIQuestionPaper (ComputerNetworks) Nov2023AnswerkeyDocument2 pagesMSE IIQuestionPaper (ComputerNetworks) Nov2023Answerkeysurajadine001No ratings yet

- Vlsi Model 4-QPDocument2 pagesVlsi Model 4-QPsanthoshNo ratings yet

- Set 1 Linear Integrated Circuits & Applications (15A04503)Document5 pagesSet 1 Linear Integrated Circuits & Applications (15A04503)N.RAMAKUMARNo ratings yet

- VTU Model Question Papers VI Sem ECE - TCEDocument44 pagesVTU Model Question Papers VI Sem ECE - TCEMr Ashutosh SrivastavaNo ratings yet

- CN QP Pattern IIDocument2 pagesCN QP Pattern IISivakumar MuthuNo ratings yet

- First Series ExamDocument1 pageFirst Series ExamxaviNo ratings yet

- Basic Eln-2021-IA-1-Set 1 - ModifiedDocument1 pageBasic Eln-2021-IA-1-Set 1 - ModifiedProf. Nikhil KulkarniNo ratings yet

- Advanced Digital VLSI Design (ECE 521) (Makeup) PDFDocument2 pagesAdvanced Digital VLSI Design (ECE 521) (Makeup) PDFRahul PinnamaneniNo ratings yet

- SEPTEMBERDocument3 pagesSEPTEMBERRocky BobeeNo ratings yet

- CN Assignment 2Document2 pagesCN Assignment 2ns7410501No ratings yet

- 21ECE27 ModelQP Set1 CAODocument2 pages21ECE27 ModelQP Set1 CAOramk1987No ratings yet

- Btech 3 Sem Sensor and Instrumentation Koe034 2020Document2 pagesBtech 3 Sem Sensor and Instrumentation Koe034 2020Atharv SinghNo ratings yet

- B19EI044 Seminar ReportDocument10 pagesB19EI044 Seminar ReportWARRIOR GamingNo ratings yet

- A Seminar Report ON: Sensor Based Automated CarDocument12 pagesA Seminar Report ON: Sensor Based Automated CarWARRIOR GamingNo ratings yet

- U18EI503 VLSI Syllabus EIEDocument2 pagesU18EI503 VLSI Syllabus EIEWARRIOR GamingNo ratings yet

- A Seminar Report ON: Sensor Based Automated CarDocument12 pagesA Seminar Report ON: Sensor Based Automated CarWARRIOR GamingNo ratings yet

- Kakatiya Institute of Technology & Science, Warangal-506015Document2 pagesKakatiya Institute of Technology & Science, Warangal-506015WARRIOR GamingNo ratings yet

- Vlsi - Mid2 15Document1 pageVlsi - Mid2 15WARRIOR GamingNo ratings yet

- "Write Your Roll Number": DateDocument2 pages"Write Your Roll Number": DateWARRIOR GamingNo ratings yet

- 10-How To Speed Up Your WordPress Website (And Why You Should) PDFDocument18 pages10-How To Speed Up Your WordPress Website (And Why You Should) PDFIcon GadgetsNo ratings yet

- Yamini NambiarDocument1 pageYamini NambiaryamininambiarNo ratings yet

- IoT Lab REPORT CSEDocument20 pagesIoT Lab REPORT CSECaptains PlayNo ratings yet

- Lab1 Week 1Document52 pagesLab1 Week 1Nguyên Trịnh Vũ ĐăngNo ratings yet

- The Art of ShitpostingDocument12 pagesThe Art of ShitpostingJoe ShmoeNo ratings yet

- 9.3.2017-Project-CSE 047 06266, CSE 047 06280-Tamjid RahmanDocument69 pages9.3.2017-Project-CSE 047 06266, CSE 047 06280-Tamjid Rahmanadrianrandolf baysicNo ratings yet

- CDS&HANA NotesDocument2 pagesCDS&HANA NotesDikshant SharmaNo ratings yet

- 1 s2.0 0734189X88901089 MainDocument36 pages1 s2.0 0734189X88901089 MainShadi AtriNo ratings yet

- HTTP - App - Utu.ac - in - Utuexmanagement - Exammsters - Syllabus - CE2010-Operating System1Document4 pagesHTTP - App - Utu.ac - in - Utuexmanagement - Exammsters - Syllabus - CE2010-Operating System1ꌩꍏꌗꃅꋪꍏꀭ T͡ᎻმƘ๏ԻNo ratings yet

- AssemblerDocument40 pagesAssemblerAASTHA JOSHINo ratings yet

- Aws VPC Connectivity OptionsDocument39 pagesAws VPC Connectivity OptionsArchan MajiNo ratings yet

- How To Find My Public IP Address From Linux CLIDocument8 pagesHow To Find My Public IP Address From Linux CLIvpalmar8871No ratings yet

- Efficient Sparse Voxel Octrees: Samuli Laine Tero Karras NVIDIA ResearchDocument9 pagesEfficient Sparse Voxel Octrees: Samuli Laine Tero Karras NVIDIA Researchgoheh52264No ratings yet

- JSY General Quotation (KADA4)Document2 pagesJSY General Quotation (KADA4)Zamri ZabidiNo ratings yet

- FRD - Top 100 Customer Report - 0.1Document8 pagesFRD - Top 100 Customer Report - 0.1Thakur Saurabh KumarNo ratings yet

- Extreme Networks: Spectralink VIEW Certified Configuration GuideDocument27 pagesExtreme Networks: Spectralink VIEW Certified Configuration GuideLuis Orlando MartinezNo ratings yet

- Hardware Installation GuidelinesDocument508 pagesHardware Installation GuidelinesRoberto PáezNo ratings yet

- DE2-115 Computer NiosIIDocument63 pagesDE2-115 Computer NiosIITran Quang Thai B1708908No ratings yet

- How To Prepare For Network Engineer Interview QuestionsDocument4 pagesHow To Prepare For Network Engineer Interview QuestionsSANKET PARSEKARNo ratings yet

- 1.2 MARS Data Cache Simulator ToolDocument2 pages1.2 MARS Data Cache Simulator Toolamarsdd7238No ratings yet

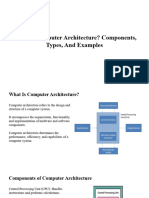

- What Is Computer Architecture - Components, Types, and ExamplesDocument10 pagesWhat Is Computer Architecture - Components, Types, and ExamplesAnvesh bandallaNo ratings yet

- Automation QuestionsDocument8 pagesAutomation QuestionsJowel RanaNo ratings yet

- Lesson PlanDocument5 pagesLesson PlanNandini prem AnandNo ratings yet

- Part1 Overview Release 13 enDocument38 pagesPart1 Overview Release 13 enkaanggonoNo ratings yet

- 1 Integrate EBS With IDCSDocument43 pages1 Integrate EBS With IDCSKishore AdikarNo ratings yet

- U CESP4 MicroGridsPy Tutorial PDFDocument24 pagesU CESP4 MicroGridsPy Tutorial PDFRenzo Diaz DelgadoNo ratings yet

- Chapter 5: Queues: (Data Structures and Algorithms)Document39 pagesChapter 5: Queues: (Data Structures and Algorithms)Duy Khanh PhanNo ratings yet

- SE Unit 1Document32 pagesSE Unit 1nmaheshkumar EEE-HICETNo ratings yet