Professional Documents

Culture Documents

Thyristors BT169 Series Logic Level: General Description Quick Reference Data

Uploaded by

wasantha bandaraOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Thyristors BT169 Series Logic Level: General Description Quick Reference Data

Uploaded by

wasantha bandaraCopyright:

Available Formats

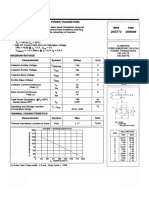

Philips Semiconductors Product specification

Thyristors BT169 series

logic level

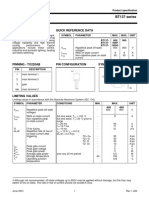

GENERAL DESCRIPTION QUICK REFERENCE DATA

Passivated, sensitive gate thyristors SYMBOL PARAMETER MAX MAX MAX MAX UNIT

in a plastic envelope, intended for use . . . .

in general purpose switching and BT169

phase control applications. These VDRM, Repetitive peak B D E G V

devices are intended to be interfaced VRRM off-state voltages 200 400 500 600

directly to microcontrollers, logic IT(AV) Average on-state A

integrated circuits and other low current 0.5 0.5 0.5 0.5

power gate trigger circuits. IT(RMS) RMS on-state current A

ITSM Non-repetitive peak 0.8 0.8 0.8 0.8 A

on-state current 8 8 8 8

PINNING - TO92 variant PIN CONFIGURATION SYMBOL

PIN DESCRIPTION

1 anode

a k

2 gate

3 cathode

3 2 1

g

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

B D E G

VDRM, VRRM Repetitive peak off-state - 2001 4001 5001 6001 V

voltages

IT(AV) Average on-state current half sine wave; - 0.5 A

Tlead ≤ 83 ˚C

IT(RMS) RMS on-state current all conduction angles - 0.8 A

ITSM Non-repetitive peak t = 10 ms - 8 A

on-state current t = 8.3 ms - 9 A

half sine wave;

Tj = 25 ˚C prior to surge

I2t I2t for fusing t = 10 ms - 0.32 A2s

dIT/dt Repetitive rate of rise of ITM = 2 A; IG = 10 mA; - 50 A/µs

on-state current after dIG/dt = 100 mA/µs

triggering

IGM Peak gate current - 1 A

VGM Peak gate voltage - 5 V

VRGM Peak reverse gate voltage - 5 V

PGM Peak gate power - 2 W

PG(AV) Average gate power over any 20 ms period - 0.1 W

Tstg Storage temperature -40 150 ˚C

Tj Operating junction - 125 ˚C

temperature

1 Although not recommended, off-state voltages up to 800V may be applied without damage, but the thyristor may

switch to the on-state. The rate of rise of current should not exceed 15 A/µs.

September 2001 1 Rev 1.500

Philips Semiconductors Product specification

Thyristors BT169 series

logic level

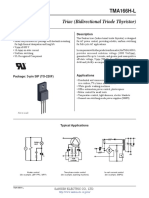

THERMAL RESISTANCES

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Rth j-lead Thermal resistance - - 60 K/W

junction to lead

Rth j-a Thermal resistance pcb mounted; lead length = 4mm - 150 - K/W

junction to ambient

STATIC CHARACTERISTICS

Tj = 25 ˚C unless otherwise stated

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

IGT Gate trigger current VD = 12 V; IT = 10 mA; gate open circuit - 50 200 µA

IL Latching current VD = 12 V; IGT = 0.5 mA; RGK = 1 kΩ - 2 6 mA

IH Holding current VD = 12 V; IGT = 0.5 mA; RGK = 1 kΩ - 2 5 mA

VT On-state voltage IT = 1 A - 1.2 1.35 V

VGT Gate trigger voltage VD = 12 V; IT = 10 mA; gate open circuit - 0.5 0.8 V

VD = VDRM(max); IT = 10 mA; Tj = 125 ˚C; 0.2 0.3 - V

gate open circuit

ID, IR Off-state leakage current VD = VDRM(max); VR = VRRM(max); Tj = 125 ˚C; - 0.05 0.1 mA

RGK = 1 kΩ

DYNAMIC CHARACTERISTICS

Tj = 25 ˚C unless otherwise stated

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

dVD/dt Critical rate of rise of VDM = 67% VDRM(max); Tj = 125 ˚C; 500 800 - V/µs

off-state voltage exponential waveform; RGK = 1 kΩ

tgt Gate controlled turn-on ITM = 2 A; VD = VDRM(max); IG = 10 mA; - 2 - µs

time dIG/dt = 0.1 A/µs

tq Circuit commutated VD = 67% VDRM(max); Tj = 125 ˚C; - 100 - µs

turn-off time ITM = 1.6 A; VR = 35 V; dITM/dt = 30 A/µs;

dVD/dt = 2 V/µs; RGK = 1 kΩ

September 2001 2 Rev 1.500

Philips Semiconductors Product specification

Thyristors BT169 series

logic level

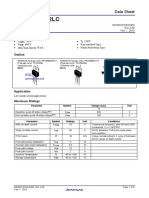

Ptot / W Tc(max) / C ITSM / A

0.8 77 10

conduction form

angle factor

a = 1.57 IT I TSM

0.7 degrees a 83

30 4 1.9 8

0.6 60 2.8 89 T time

90 2.2 2.2 Tj initial = 25 C max

120 1.9

0.5 180 1.57 95

2.8 6

0.4 4 101

0.3 107 4

0.2 113

2

0.1 119

0 125

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0

1 10 100 1000

IF(AV) / A Number of half cycles at 50Hz

Fig.1. Maximum on-state dissipation, Ptot, versus Fig.4. Maximum permissible non-repetitive peak

average on-state current, IT(AV), where on-state current ITSM, versus number of cycles, for

a = form factor = IT(RMS)/ IT(AV). sinusoidal currents, f = 50 Hz.

ITSM / A IT(RMS) / A

1000 2

1.5

100

10 IT I TSM

0.5

T time

Tj initial = 25 C max

1 0

10us 100us 1ms 10ms 0.01 0.1 1 10

T/s surge duration / s

Fig.2. Maximum permissible non-repetitive peak Fig.5. Maximum permissible repetitive rms on-state

on-state current ITSM, versus pulse width tp, for current IT(RMS), versus surge duration, for sinusoidal

sinusoidal currents, tp ≤ 10ms. currents, f = 50 Hz; Tlead ≤ 83˚C.

IT(RMS) / A VGT(Tj)

1 VGT(25 C)

1.6

83 C

0.8 1.4

1.2

0.6

1

0.4

0.8

0.2

0.6

0 0.4

-50 0 50 100 150 -50 0 50 100 150

Tlead / C Tj / C

Fig.3. Maximum permissible rms current IT(RMS) , Fig.6. Normalised gate trigger voltage

versus lead temperature, Tlead. VGT(Tj)/ VGT(25˚C), versus junction temperature Tj.

September 2001 3 Rev 1.500

Philips Semiconductors Product specification

Thyristors BT169 series

logic level

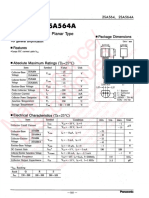

IGT(Tj) IT / A

5

IGT(25 C) Tj = 125 C

3

Tj = 25 C

4

2.5 Vo = 1.067 V

Rs = 0.187 ohms typ max

2 3

1.5

2

1

1

0.5

0 0

-50 0 50 100 150 0 0.5 1 1.5 2 2.5

Tj / C VT / V

Fig.7. Normalised gate trigger current Fig.10. Typical and maximum on-state characteristic.

IGT(Tj)/ IGT(25˚C), versus junction temperature Tj.

IL(Tj) Zth j-lead (K/W)

100

IL(25 C)

3

2.5 10

2

1

1.5

P tp

D

1

0.1

t

0.5

0.01

0 10us 0.1ms 1ms 10ms 0.1s 1s 10s

-50 0 50 100 150

Tj / C tp / s

Fig.8. Normalised latching current IL(Tj)/ IL(25˚C), Fig.11. Transient thermal impedance Zth j-lead, versus

versus junction temperature Tj, RGK = 1 kΩ. pulse width tp.

IH(Tj) dVD/dt (V/us)

IH(25 C) 10000

3

RGK = 1 kohms

2.5

1000

2

1.5

100

1

0.5

10

0 0 50 100 150

-50 0 50 100 150 Tj / C

Tj / C

Fig.9. Normalised holding current IH(Tj)/ IH(25˚C), Fig.12. Typical, critical rate of rise of off-state voltage,

versus junction temperature Tj, RGK = 1 kΩ. dVD/dt versus junction temperature Tj.

September 2001 4 Rev 1.500

Philips Semiconductors Product specification

Thyristors BT169 series

logic level

MECHANICAL DATA

Plastic single-ended leaded (through hole) package; 3 leads SOT54

d A L

1

e1

2

D e

b1

L1

0 2.5 5 mm

scale

DIMENSIONS (mm are the original dimensions)

UNIT A b b1 c D d E e e1 L L1(1)

5.2 0.48 0.66 0.45 4.8 1.7 4.2 14.5

mm 2.54 1.27 2.5

5.0 0.40 0.56 0.40 4.4 1.4 3.6 12.7

Note

1. Terminal dimensions within this zone are uncontrolled to allow for flow of plastic and terminal irregularities.

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC EIAJ PROJECTION

SOT54 TO-92 SC-43 97-02-28

Fig.13. TO92 ; plastic envelope; Net Mass: 0.2 g

Notes

1. Epoxy meets UL94 V0 at 1/8".

September 2001 5 Rev 1.500

Philips Semiconductors Product specification

Thyristors BT169 series

logic level

DEFINITIONS

DATA SHEET STATUS

DATA SHEET PRODUCT DEFINITIONS

STATUS2 STATUS3

Objective data Development This data sheet contains data from the objective specification for

product development. Philips Semiconductors reserves the right to

change the specification in any manner without notice

Preliminary data Qualification This data sheet contains data from the preliminary specification.

Supplementary data will be published at a later date. Philips

Semiconductors reserves the right to change the specification without

notice, in ordere to improve the design and supply the best possible

product

Product data Production This data sheet contains data from the product specification. Philips

Semiconductors reserves the right to make changes at any time in

order to improve the design, manufacturing and supply. Changes will

be communicated according to the Customer Product/Process

Change Notification (CPCN) procedure SNW-SQ-650A

Limiting values

Limiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one

or more of the limiting values may cause permanent damage to the device. These are stress ratings only and

operation of the device at these or at any other conditions above those given in the Characteristics sections of

this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

Philips Electronics N.V. 2001

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the

copyright owner.

The information presented in this document does not form part of any quotation or contract, it is believed to be

accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any

consequence of its use. Publication thereof does not convey nor imply any license under patent or other

industrial or intellectual property rights.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices or systems where malfunction of these

products can be reasonably expected to result in personal injury. Philips customers using or selling these products

for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting

from such improper use or sale.

2 Please consult the most recently issued datasheet before initiating or completing a design.

3 The product status of the device(s) described in this datasheet may have changed since this datasheet was

published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

September 2001 6 Rev 1.500

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Lua ProgrammingDocument38 pagesLua ProgrammingPaul EduardNo ratings yet

- TURBO-Buick V6 Turbo Intro 780413Document21 pagesTURBO-Buick V6 Turbo Intro 780413T Smi100% (1)

- Photo Studio: User's GuideDocument243 pagesPhoto Studio: User's GuideAfonso BuenoNo ratings yet

- 04 PPP TTE API 570 Piping InspnDocument35 pages04 PPP TTE API 570 Piping InspnRavindra S. Jivani100% (8)

- Calculation and Spesification of Fuel Oil System: Design Iv Machinery Department of Marine EngineeringDocument42 pagesCalculation and Spesification of Fuel Oil System: Design Iv Machinery Department of Marine EngineeringMuzami ThahirNo ratings yet

- 2 Technology EvolutionDocument20 pages2 Technology EvolutionRokan Uddin100% (1)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Drawworks and Rig Sizing PDFDocument8 pagesDrawworks and Rig Sizing PDFAmine Mimo100% (1)

- BT169 01Document7 pagesBT169 01Rizky SyahNo ratings yet

- Datasheet BT150 500RDocument6 pagesDatasheet BT150 500RJosemar M. FerreiraNo ratings yet

- Thyristors BT168W Series Logic Level For RCD/ GFI/ LCCB ApplicationsDocument7 pagesThyristors BT168W Series Logic Level For RCD/ GFI/ LCCB ApplicationshassamNo ratings yet

- BT151Document8 pagesBT151Javier ParedesNo ratings yet

- D Data Sheet: BT300S SeriesDocument8 pagesD Data Sheet: BT300S SeriesFabio LastraNo ratings yet

- BT 151Document6 pagesBT 151Oscar FernandezNo ratings yet

- BT151 Series 2Document7 pagesBT151 Series 2Louie Derek OrtizNo ratings yet

- D Data Sheet: BT131W SeriesDocument9 pagesD Data Sheet: BT131W Seriesuser_scribd54635No ratings yet

- datasheet4Document6 pagesdatasheet4echkomNo ratings yet

- Datasheet 2Document8 pagesDatasheet 2YELZAX C.ANo ratings yet

- BT169Document5 pagesBT169zaveriprernaNo ratings yet

- Thyristors BTA151 Series Sensitive Gate: General Description Quick Reference DataDocument6 pagesThyristors BTA151 Series Sensitive Gate: General Description Quick Reference DatarogeriocorreaNo ratings yet

- Bt136 SeriesDocument6 pagesBt136 SeriesRudy GunawanNo ratings yet

- BT137Document7 pagesBT137Gabriel RacovskyNo ratings yet

- Thyristors BT151F Series: General Description Quick Reference DataDocument6 pagesThyristors BT151F Series: General Description Quick Reference DataadyanNo ratings yet

- BT152 PhilipsSemiconductorsDocument8 pagesBT152 PhilipsSemiconductorsDiego RicardoNo ratings yet

- BT131 Series: General Description Quick Reference DataDocument5 pagesBT131 Series: General Description Quick Reference DataDabro FabioNo ratings yet

- BT137 PhiDocument6 pagesBT137 PhiJavierJBVNo ratings yet

- Triacs BT136 Series D Logic Level: General Description Quick Reference DataDocument6 pagesTriacs BT136 Series D Logic Level: General Description Quick Reference DatarepelindNo ratings yet

- Triacs BT139 Series: General Description Quick Reference DataDocument6 pagesTriacs BT139 Series: General Description Quick Reference DataJose Luis SabinoNo ratings yet

- TRIACS CatálogoDocument8 pagesTRIACS CatálogoJacy FigueNo ratings yet

- BT138 SeriesDocument8 pagesBT138 SeriesYogi RuliemNo ratings yet

- BT139 PhilipsDocument6 pagesBT139 PhilipsDelcu MarinicaNo ratings yet

- Triacs BT137 Series: General Description Quick Reference DataDocument3 pagesTriacs BT137 Series: General Description Quick Reference DataLidice BarreraNo ratings yet

- Triacs BT137-600D Logic Level: General Description Quick Reference DataDocument7 pagesTriacs BT137-600D Logic Level: General Description Quick Reference DataGabriel Alexander R. MNo ratings yet

- D Data Sheet: BT134 SeriesDocument9 pagesD Data Sheet: BT134 SeriesMohsenNo ratings yet

- D Data SheetDocument8 pagesD Data SheetAlexandru Gheorghe VisinoiuNo ratings yet

- Three Quadrant Triacs BTA204S Series B and C High CommutationDocument6 pagesThree Quadrant Triacs BTA204S Series B and C High CommutationAlex SandroNo ratings yet

- Three Quadrant Triacs BTA212 Series B High Commutation: General Description Quick Reference DataDocument6 pagesThree Quadrant Triacs BTA212 Series B High Commutation: General Description Quick Reference DataВасилий ЛитвинNo ratings yet

- Triacs BT137X Series D Logic Level: General Description Quick Reference DataDocument6 pagesTriacs BT137X Series D Logic Level: General Description Quick Reference DataSantiago SerranoNo ratings yet

- Data Sheet: BTA204S Series D, E and F BTA204M Series D, E and FDocument8 pagesData Sheet: BTA204S Series D, E and F BTA204M Series D, E and FMindSet MarcosNo ratings yet

- BT169D LDocument12 pagesBT169D Lأبو أنس المسلمNo ratings yet

- 2N5064Document5 pages2N5064JADERSONNo ratings yet

- Triacs BT136F Series: General Description Quick Reference DataDocument8 pagesTriacs BT136F Series: General Description Quick Reference DataChelaru CosminNo ratings yet

- BT136BDocument6 pagesBT136BsaumyakanthaNo ratings yet

- DatasheetDocument6 pagesDatasheetratnaNo ratings yet

- BCR8PM-12L RenesasTechnologyDocument8 pagesBCR8PM-12L RenesasTechnologyAriel GarciaNo ratings yet

- Unisonic Technologies Co., LTD: Description 1Document5 pagesUnisonic Technologies Co., LTD: Description 1alexjcc10No ratings yet

- BT169DDocument1 pageBT169DBuho FielNo ratings yet

- R07ds0959ej0400 bcr16fm14ljDocument9 pagesR07ds0959ej0400 bcr16fm14ljJacky NplNo ratings yet

- Haopin Microelectronics Co.,Ltd.: Sensitive Gate TriacsDocument5 pagesHaopin Microelectronics Co.,Ltd.: Sensitive Gate TriacsIsac Rodrigues DE MatosNo ratings yet

- MCR100W 10M 0-2902672Document12 pagesMCR100W 10M 0-2902672chawkigenieNo ratings yet

- ACS110-7SN/SB2: Ac Line Switch Asd™ AC Switch FamilyDocument10 pagesACS110-7SN/SB2: Ac Line Switch Asd™ AC Switch FamilySamerNo ratings yet

- D bcr8lm-14lj TDocument8 pagesD bcr8lm-14lj TJonn Sim-OneNo ratings yet

- C106D C106M C106D C106M: Haopin Microelectronics Co.,LtdDocument4 pagesC106D C106M C106D C106M: Haopin Microelectronics Co.,LtdmadiserviNo ratings yet

- Data SheetDocument5 pagesData SheetLucas QuarchioniNo ratings yet

- Quick Reference Data: General Description SOT82Document4 pagesQuick Reference Data: General Description SOT82Julio Desales SerranoNo ratings yet

- TMA166H-L Triac Provides Reliable AC Power ControlDocument10 pagesTMA166H-L Triac Provides Reliable AC Power ControlARANASOFTNo ratings yet

- BCR8KM-14LA RenesasTechnologyDocument8 pagesBCR8KM-14LA RenesasTechnologyosvaldoNo ratings yet

- 2P4M: Pb Free Plating Product 2.0 Ampere Passivated Process Thyristor---Sensitive Gate SCRDocument3 pages2P4M: Pb Free Plating Product 2.0 Ampere Passivated Process Thyristor---Sensitive Gate SCRbasheer almetwakelNo ratings yet

- 12 A 800 V Snubberless Triac in TO-220AB Package: FeaturesDocument11 pages12 A 800 V Snubberless Triac in TO-220AB Package: FeaturesDelos Santos JojoNo ratings yet

- REN R07ds1031ej0300 bcr16cm12lc DST 20190201Document9 pagesREN R07ds1031ej0300 bcr16cm12lc DST 20190201Purwanto B012No ratings yet

- Cr02am-8 (To-92)Document8 pagesCr02am-8 (To-92)Manuel De Jesus Andrade PalacioNo ratings yet

- Bta216 600e HaopinDocument5 pagesBta216 600e HaopinRAYLINo ratings yet

- Byw29ex 200Document8 pagesByw29ex 200taligentxspamNo ratings yet

- TMA126G-L Triac Technical SpecificationsDocument10 pagesTMA126G-L Triac Technical SpecificationsPedro RodriguezNo ratings yet

- MSP3400D & MSP3410DDocument83 pagesMSP3400D & MSP3410Dwasantha bandaraNo ratings yet

- 2SA564Document4 pages2SA564wasantha bandaraNo ratings yet

- Datasheet PDFDocument4 pagesDatasheet PDFmargarita_ceron_1No ratings yet

- BT138 SeriesDocument8 pagesBT138 SeriesYogi RuliemNo ratings yet

- High Breakdown Voltage Silicon NPN Power Transistor 2SC5885Document2 pagesHigh Breakdown Voltage Silicon NPN Power Transistor 2SC5885wasantha bandaraNo ratings yet

- Infineon IHW15N120R3 DS v02 - 05 ENDocument15 pagesInfineon IHW15N120R3 DS v02 - 05 ENgusiusNo ratings yet

- TM1628Document14 pagesTM1628chandra sekhar BeheraNo ratings yet

- Toshiba transistor specificationsDocument5 pagesToshiba transistor specificationsjose peresNo ratings yet

- Isc 2SC4007: Silicon NPN Power TransistorDocument2 pagesIsc 2SC4007: Silicon NPN Power Transistorwasantha bandaraNo ratings yet

- Volume, Bass and Treble Circuit in Audio Amplifier: InstructablesDocument8 pagesVolume, Bass and Treble Circuit in Audio Amplifier: Instructableswasantha bandaraNo ratings yet

- 2N3773 & 2N6609Document3 pages2N3773 & 2N6609wasantha bandaraNo ratings yet

- 2N3773 & 2N6609Document3 pages2N3773 & 2N6609wasantha bandaraNo ratings yet

- Delmar Unit 4 Magnetism Sept 2022Document51 pagesDelmar Unit 4 Magnetism Sept 2022Williams UgazNo ratings yet

- MS AccessDocument34 pagesMS AccessRovin Garcia0% (1)

- 3064 A CG Assignment-2Document57 pages3064 A CG Assignment-2nokexo6067No ratings yet

- MVC Architecture and Sales Order Entry (P42101)Document10 pagesMVC Architecture and Sales Order Entry (P42101)ashish007d100% (1)

- Kingfisher Rtu Mod BusDocument4 pagesKingfisher Rtu Mod BusClifford RyanNo ratings yet

- IBM System x3250 M3: IBM Redbooks Product GuideDocument29 pagesIBM System x3250 M3: IBM Redbooks Product Guidegopi_hcNo ratings yet

- Bsme 1 3 G1 E3Document12 pagesBsme 1 3 G1 E3Daniel ParungaoNo ratings yet

- Chapter 3 Kinematics in Two Dimensions VectorsDocument18 pagesChapter 3 Kinematics in Two Dimensions VectorsShaquille AbhistaNo ratings yet

- Mathematics of 3D PrintingDocument41 pagesMathematics of 3D PrintingHabtamu GeremewNo ratings yet

- Fanuc 0i, 16i, 18i, 21i Series and 16/18 Models A, B and C: Setting (Handy)Document2 pagesFanuc 0i, 16i, 18i, 21i Series and 16/18 Models A, B and C: Setting (Handy)Mariusz DubasNo ratings yet

- Aiats Practise Test-1Document46 pagesAiats Practise Test-1Arunanshu Pal75% (4)

- B Cell ActivationDocument62 pagesB Cell ActivationAYSHAMOHD88No ratings yet

- Mineral-Insulated Thermocouples According To DIN 43710 and DIN EN 60584Document11 pagesMineral-Insulated Thermocouples According To DIN 43710 and DIN EN 60584Veryco BudiantoNo ratings yet

- D5G6 DatasheetDocument3 pagesD5G6 DatasheetchichedemorenoNo ratings yet

- Afm E308-16 Afm E308h-16Document13 pagesAfm E308-16 Afm E308h-16Julio Cesar Lazcano PintoNo ratings yet

- Generation of High Voltages & CurrentsDocument79 pagesGeneration of High Voltages & CurrentshamzaNo ratings yet

- Impact of Massive MIMO Antennas on 5G Network CapacityDocument10 pagesImpact of Massive MIMO Antennas on 5G Network CapacitykamelNo ratings yet

- Long QuizDocument2 pagesLong QuizDavid Mikael Nava TaclinoNo ratings yet

- End of Year Project ExamplesDocument10 pagesEnd of Year Project ExamplesMalik Fahad YounasNo ratings yet

- SMC Imu Data Sheet Motion SensorDocument2 pagesSMC Imu Data Sheet Motion SensorErwin ArdiasNo ratings yet

- Accurate Doppler Current Sensor for Measuring Sea Current Speed and DirectionDocument4 pagesAccurate Doppler Current Sensor for Measuring Sea Current Speed and DirectionKiran VepanjeriNo ratings yet

- 5 - Lab5 - Permanganate and Dichromate TitrationDocument5 pages5 - Lab5 - Permanganate and Dichromate TitrationHoang Thao0% (1)

- Python Interactive Mode: Anaconda Navigator SpyderDocument5 pagesPython Interactive Mode: Anaconda Navigator SpyderDeeshpreet Kaur sonaNo ratings yet