Professional Documents

Culture Documents

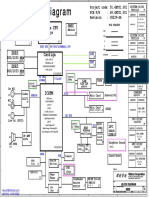

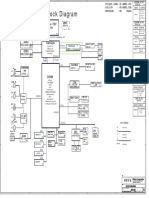

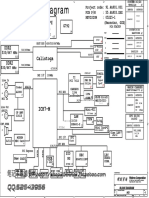

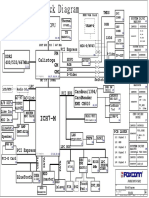

B460 Power Up Sequence

B460 Power Up Sequence

Uploaded by

sousalrCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

B460 Power Up Sequence

B460 Power Up Sequence

Uploaded by

sousalrCopyright:

Available Formats

1 2 3 4 5 6 7 8

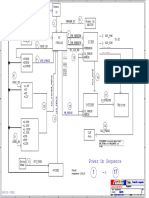

G3 G3 --> S5 S5 S0 S3 S0 S4/S5 S4(S5)-->G3 G3

DC_IN DC_IN+

DCBATOUT DCBATOUT

A A

+ECVCC +ECVCC

EC[I] ECRST#

ECRST#

EC[O]ALW_ON T01 (Min. 5 ms)

ALW_ON

+3VALW/+5VALW +3VALW/+5VALW

Power

EC[I]ALW_PWRGD Switch ALW_PWRGD

Press

EC[I]PWRSW#

PWRSW#

T02 T05

(700ms) (50ms)

EC[O]PWRBTN# (From EC to PCH) T04

(150ms) PWRBTN#

T03

(5ms) For battery mode(ACIN_EC inactive):

EC[O]PM_RSMRST# (From EC to PCH) PM_RSMRST# follow ACIN_EC

PCH will wait for 4-5 seconds before de-asserting SLP_S5# & PM_SLP_S5# &PM_SLP_S4#) PM_RSMRST#

Ta (max.110ms)

EC[I]PM_SLP_S5# (From PCH to EC) PM_SLP_S5#

T8 (Min 30us)

B EC[I]PM_SLP_S4# (From PCH to EC) PM_SLP_S4# B

T9 (Min 30us)

EC[I]PM_SLP_S3# (From PCH to EC) PM_SLP_S3#

T06(1ms) T17(1ms)

EC[O]SUS_ON SUS_ON

+3VSUS/+5VSUS +3V_SUS/+5V_SUS

+1_5VSUS/DDRDIMM_VREF (0V to1.5V ->Max.2ms for DDR3) +1_5VSUS/DDRDIMM_VREF(DDR2)

(~0.3ms)Td

EC[I]SUS_PWRGD SUS_PWRGD

T07(1ms)

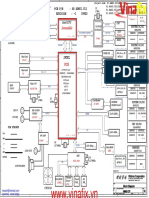

EC[O]RUN_ON T16 (5ms)

+3VRUN/+5VRUN

T08(5ms)

EC[O]RUN_ON1 T15(2ms)

PEX_VDD/NV_VDD/+1_05VRUN/+1_5VRUN/+1_1V_VTT/+1_8VRUN/+0_75VRUN

T09 (5ms)

(~1.8ms) Te

EC[I]RUN_PWRGD (From +1_1V_VTT VR PGOOD to EC)

C C

VTTPWRGOOD (TO CPU) Repeat Previous Repeat Previous

T16

(Delay Min 99ms)

S0 Sequence S3 Sequence

EC[O]IMVP_VR_ON (From EC to IMVP6) T13(1ms)

VHCORE

CLK_PWRGD T18(From 10 to 100us )

EC[I]IMVP_OK

CLK_CPU_BCLK (From Clock Gen TO CPU)

T24( Min 1ms )

EC[O]IMVP_PWRGD ( Form EC to PCH) T12(1ms)

T20( From 3ms to 20ms )

SYS_PWROK/PWROK/MEPWROK/LAN_RST# T21

( Min 5ms )

D D

BCLK, SRCCLK, PCICLK

Running

T23

T22( Min 100ns ) ( Min 1ms )

PM_DRAM_PWRGD (Form PCH to CPU)

T24 ( Min 1ms )

H_CPUPWRGD (From PCH to CPU) T25 ( From 1ms to 100ms )

( Min 1ms ) T26

PLT_RST# (From PCH to CPU) T32 (Min 1ms)

1 2 3 4 5 6 7 8

You might also like

- David Lowenthal The Past Is A Foreign Country PDFDocument677 pagesDavid Lowenthal The Past Is A Foreign Country PDFErika Cerqueira100% (6)

- Topstar C46 C48 - Power On SequenceDocument1 pageTopstar C46 C48 - Power On SequenceCamilo Rodriguez NiñoNo ratings yet

- Spaj 140 C Combined Overcurrent and Earth-Fault Relay: User S Manual and Technical DescriptionDocument16 pagesSpaj 140 C Combined Overcurrent and Earth-Fault Relay: User S Manual and Technical DescriptionOreonnyr SouzaNo ratings yet

- Spaj 140 C Overcurrent and Earth-Fault Relay: User S Manual and Technical DescriptionDocument68 pagesSpaj 140 C Overcurrent and Earth-Fault Relay: User S Manual and Technical Descriptionzaheer2931No ratings yet

- Spaj 140 C Overcurrent and Earth-Fault Relay: User S Manual and Technical DescriptionDocument68 pagesSpaj 140 C Overcurrent and Earth-Fault Relay: User S Manual and Technical Descriptionzaheer ahamedNo ratings yet

- Spam 150 C Motor Protection Relay: User S Manual and Technical DescriptionDocument13 pagesSpam 150 C Motor Protection Relay: User S Manual and Technical DescriptionrpshvjuNo ratings yet

- FM Spac310c en BaacDocument110 pagesFM Spac310c en BaacThong PhamNo ratings yet

- FM Spaj141c en BbaDocument68 pagesFM Spaj141c en Bbathanhnguyen81No ratings yet

- ASUS A8E A8S F8S Power On SequenceDocument1 pageASUS A8E A8S F8S Power On SequenceEduinMaracuchoFernandezChaparroNo ratings yet

- Description of Configuration C30: Generator Protection REG670 1MRK 502 074-BEN QDocument1 pageDescription of Configuration C30: Generator Protection REG670 1MRK 502 074-BEN QTuấn Lê QuangNo ratings yet

- Experiment - 8 Date: 04/10/2021 AIM: To Design and Implement Relaxation Oscillator Using Op-Amp. TheoryDocument4 pagesExperiment - 8 Date: 04/10/2021 AIM: To Design and Implement Relaxation Oscillator Using Op-Amp. TheoryTimir PatelNo ratings yet

- Quanta Jm3 Power Sequence Rev 02Document37 pagesQuanta Jm3 Power Sequence Rev 02u6k5lp l2y3z0No ratings yet

- KD-R370K - R470K - R471xxx - R472E - R473MM2 - R474E - R476M - R477Q - R670K - R671x (SCH) - 70898Document26 pagesKD-R370K - R470K - R471xxx - R472E - R473MM2 - R474E - R476M - R477Q - R670K - R671x (SCH) - 70898Genaro NavarroNo ratings yet

- SPAA 120 C and SPAA 121 C Feeder Protection Relay: User S Manual and Technical DescriptionDocument76 pagesSPAA 120 C and SPAA 121 C Feeder Protection Relay: User S Manual and Technical DescriptionchupzptNo ratings yet

- Training Msi MS-7 - IiDocument17 pagesTraining Msi MS-7 - IiadaofisicoNo ratings yet

- 238 Series Normally Close Big Sizes (1 14'' 2") Revision Letter ChangeDocument4 pages238 Series Normally Close Big Sizes (1 14'' 2") Revision Letter Changekev YNo ratings yet

- High Efficiency Rectifiers: High-Reliability Discrete Products and Engineering Services Since 1977Document4 pagesHigh Efficiency Rectifiers: High-Reliability Discrete Products and Engineering Services Since 1977jesus cautivoNo ratings yet

- STK 086Document1 pageSTK 086Omar ArceNo ratings yet

- Spaj 144 C Combined Overcurrent and Earth-Fault Relay: User S Manual and Technical DescriptionDocument24 pagesSpaj 144 C Combined Overcurrent and Earth-Fault Relay: User S Manual and Technical DescriptionDiseño y Gestión de ProyectosNo ratings yet

- Curva de Daño de EquiposDocument1 pageCurva de Daño de EquiposdiegoNo ratings yet

- Acer Aspire 4310 (Wistron Volvi)Document42 pagesAcer Aspire 4310 (Wistron Volvi)microchip.labotecNo ratings yet

- DC Motor Driver With Position Control: Description OscillatorDocument9 pagesDC Motor Driver With Position Control: Description Oscillatorshahryar BRVNo ratings yet

- Electr Cal Equipment List For Asab-1: Conlractor NoDocument15 pagesElectr Cal Equipment List For Asab-1: Conlractor Noganesh kumarNo ratings yet

- RoboMaster 开发板A型 原理图Document10 pagesRoboMaster 开发板A型 原理图wangbo2750No ratings yet

- Vinafix - VN Acer Aspire 4741zg Emachines d730 - Wistron Hm42-Cp Je40-Cp - Rev SCDocument68 pagesVinafix - VN Acer Aspire 4741zg Emachines d730 - Wistron Hm42-Cp Je40-Cp - Rev SCเอกชัย เพชรจันทร์No ratings yet

- Sualaptop365.edu - VN - Acer 4741G 4743G HM42-CP 0122 09920-3 JE40-CP MBDocument68 pagesSualaptop365.edu - VN - Acer 4741G 4743G HM42-CP 0122 09920-3 JE40-CP MBEcho RodeoNo ratings yet

- Acer Aspire 3935 (Wistron SM30) PDFDocument45 pagesAcer Aspire 3935 (Wistron SM30) PDFMustafa AkanNo ratings yet

- IBM Thinkpad Z61 (Quanta BW2)Document80 pagesIBM Thinkpad Z61 (Quanta BW2)Maks ProstNo ratings yet

- Quanta jm3Document37 pagesQuanta jm3CADASEDANo ratings yet

- Packard Bell ETNA GM-WistronDocument50 pagesPackard Bell ETNA GM-WistronEdson HenriqueNo ratings yet

- Acer Aspire 7535 - 7535ZG - 7735 - 7738 Wistron JM70-MV RevSB SchematicDocument55 pagesAcer Aspire 7535 - 7535ZG - 7735 - 7738 Wistron JM70-MV RevSB Schematicpremium.technNo ratings yet

- Data Sheet: Weltrend Semiconductor, IncDocument10 pagesData Sheet: Weltrend Semiconductor, IncaadNo ratings yet

- (Models: XTM - 443 / 773 / 993) : DIP Switch Setting:-1) Timer Mode SettingDocument3 pages(Models: XTM - 443 / 773 / 993) : DIP Switch Setting:-1) Timer Mode SettingashNo ratings yet

- Eletro-X - gpr51 La-J493p (Rev 2.0)Document48 pagesEletro-X - gpr51 La-J493p (Rev 2.0)All CastilloNo ratings yet

- Sri Lanka Institute of Information Technology: Faculty of Engineering Department of Electrical and Computer EngineeringDocument4 pagesSri Lanka Institute of Information Technology: Faculty of Engineering Department of Electrical and Computer EngineeringMadhushan DassanayakeNo ratings yet

- Regulador de Voltaje GAVR8AhDocument2 pagesRegulador de Voltaje GAVR8AhcrecosiroNo ratings yet

- lm555 DatasheetDocument11 pageslm555 DatasheetKhu GhingNo ratings yet

- TL2843B Q1 etcTIDocument18 pagesTL2843B Q1 etcTIrahma jayaNo ratings yet

- Datasheet 2n4354Document1 pageDatasheet 2n4354BuchoriNo ratings yet

- Modelling Parallel Operation of Power Rectifiers With PspiceDocument8 pagesModelling Parallel Operation of Power Rectifiers With PspiceAl-amin AlexNo ratings yet

- CADIZ-CP Block Diagram: Intel CPUDocument57 pagesCADIZ-CP Block Diagram: Intel CPUvnenovNo ratings yet

- Sony Mbx-229 - Wistron Cadiz-Cp - Rev - 1mDocument57 pagesSony Mbx-229 - Wistron Cadiz-Cp - Rev - 1mLeandro SilvaNo ratings yet

- Mu5dc CH7DC (Rev 2.0)Document86 pagesMu5dc CH7DC (Rev 2.0)aka.virtuozNo ratings yet

- SP481E / SP485E Enhanced Low Power Half-Duplex RS-485 TransceiversDocument12 pagesSP481E / SP485E Enhanced Low Power Half-Duplex RS-485 TransceiversAlejandro PerezNo ratings yet

- Dell Power On 2Document1 pageDell Power On 2Rajesh BarangeNo ratings yet

- K46CM Repair Guide: Jul/23/2012 John - Jin Csc-GrmaDocument5 pagesK46CM Repair Guide: Jul/23/2012 John - Jin Csc-Grmaanas symbianNo ratings yet

- Acer Aspire5560 (Wistron Ag1 UMA-1-0309 PDFDocument45 pagesAcer Aspire5560 (Wistron Ag1 UMA-1-0309 PDFsousalrNo ratings yet

- NLC0BE3# Nlrefresh0: Address BUS AddressDocument6 pagesNLC0BE3# Nlrefresh0: Address BUS AddressDjony Sedilque NunesNo ratings yet

- EST7502B PC Power Supply PWM With Supervisor: General DescriptionDocument7 pagesEST7502B PC Power Supply PWM With Supervisor: General DescriptionGabriel ZanottiNo ratings yet

- PLECS Basics: Síxifo FalconesDocument20 pagesPLECS Basics: Síxifo FalconesBryon MitchellNo ratings yet

- OT MES 3G Kabbara2Document33 pagesOT MES 3G Kabbara2Youssef ameurNo ratings yet

- Three-Phase Induction Motor DTC-SVPWM Scheme With Self-Tuning PI-Type Fuzzy ControllerDocument7 pagesThree-Phase Induction Motor DTC-SVPWM Scheme With Self-Tuning PI-Type Fuzzy ControllerManuel DelgadoNo ratings yet

- Lenovo IdeaPad Y330 Wistron Olympus LT32P 07242 RevSBDocument54 pagesLenovo IdeaPad Y330 Wistron Olympus LT32P 07242 RevSBRohithRenNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsRating: 5 out of 5 stars5/5 (1)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetNo ratings yet

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetRating: 2 out of 5 stars2/5 (1)

- Advanced Electric Drives: Analysis, Control, and Modeling Using MATLAB / SimulinkFrom EverandAdvanced Electric Drives: Analysis, Control, and Modeling Using MATLAB / SimulinkNo ratings yet

- Power Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlFrom EverandPower Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlRating: 5 out of 5 stars5/5 (1)

- Lenovo G400 (Compal LA-3781P) Free Laptop SchematicsDocument46 pagesLenovo G400 (Compal LA-3781P) Free Laptop SchematicsIon BogheanNo ratings yet

- Ibm R40Document60 pagesIbm R40حسن علي نوفلNo ratings yet

- Compal Confidential: Gx00/Gx00 DIS M/B Schematics DocumentDocument60 pagesCompal Confidential: Gx00/Gx00 DIS M/B Schematics Documentحسن علي نوفلNo ratings yet

- Laptop Lenovo Foxcon-661S03Document50 pagesLaptop Lenovo Foxcon-661S03حسن علي نوفلNo ratings yet

- Compal Confidential: DCL55 Schematics Document Banias ICP uFCBGA/uFCPGA Package With Montara-GM Core LogicDocument45 pagesCompal Confidential: DCL55 Schematics Document Banias ICP uFCBGA/uFCPGA Package With Montara-GM Core Logicحسن علي نوفلNo ratings yet

- Ibm Rome3 (1) .5Document83 pagesIbm Rome3 (1) .5حسن علي نوفلNo ratings yet

- Lenovo 3000 N220 N440 Wistron Anote2.0 AMD - Bak.bak - Bak.bak - BakDocument55 pagesLenovo 3000 N220 N440 Wistron Anote2.0 AMD - Bak.bak - Bak.bak - Bakحسن علي نوفلNo ratings yet

- DC/DC & Charger Taurus2 Block Diagram : YonahDocument40 pagesDC/DC & Charger Taurus2 Block Diagram : Yonahحسن علي نوفلNo ratings yet

- Laptop Lenovo Foxcon-S04Document40 pagesLaptop Lenovo Foxcon-S04حسن علي نوفلNo ratings yet

- Lenovo 3000 N220-N440-Wistron Anote2.0 AMDDocument55 pagesLenovo 3000 N220-N440-Wistron Anote2.0 AMDحسن علي نوفلNo ratings yet

- Lenovo B470 - Wistron - La47-10250-1 - 1104Document103 pagesLenovo B470 - Wistron - La47-10250-1 - 1104حسن علي نوفلNo ratings yet

- Laptop Lenovo Foxcon-W06NDocument44 pagesLaptop Lenovo Foxcon-W06Nحسن علي نوفلNo ratings yet

- Laptop Lenovo Foxcon-S09Document45 pagesLaptop Lenovo Foxcon-S09حسن علي نوفلNo ratings yet

- Laptop Lenovo Foxcon-TPC01Document39 pagesLaptop Lenovo Foxcon-TPC01حسن علي نوفلNo ratings yet

- Laptop Lenovo Foxcon-TPC02Document33 pagesLaptop Lenovo Foxcon-TPC02حسن علي نوفلNo ratings yet

- Lenovo g530 n500 - Compal La-4212p Jiwa3 Jiwa4 - Rev 1Document53 pagesLenovo g530 n500 - Compal La-4212p Jiwa3 Jiwa4 - Rev 1Erasto Villalón Sánchez0% (1)

- 04211-3 SIT 39T5202: Intel Alviso-GMDocument71 pages04211-3 SIT 39T5202: Intel Alviso-GMحسن علي نوفلNo ratings yet

- Compal Confidential: Mobile Dothan uFCPGA With Intel Alviso - GM+ICH6-M Core Logic Schematics DocumentDocument46 pagesCompal Confidential: Mobile Dothan uFCPGA With Intel Alviso - GM+ICH6-M Core Logic Schematics Documentحسن علي نوفلNo ratings yet

- Ibm x31Document83 pagesIbm x31حسن علي نوفلNo ratings yet

- Lenovo G430 LA-4211PDocument53 pagesLenovo G430 LA-4211Pحسن علي نوفلNo ratings yet

- Ibm Rome4 (1) .0Document88 pagesIbm Rome4 (1) .0حسن علي نوفلNo ratings yet

- Lenovo 3000 G410 (COMPAL LA-3691P) Laptop Schematics DiagramDocument47 pagesLenovo 3000 G410 (COMPAL LA-3691P) Laptop Schematics Diagramحسن علي نوفلNo ratings yet

- Nvidia N11M-GE Intel CPU Auburndale (Dual Core) : PCB LayerDocument58 pagesNvidia N11M-GE Intel CPU Auburndale (Dual Core) : PCB Layerحسن علي نوفلNo ratings yet

- Complete ProjectDocument74 pagesComplete Projectyung JayceNo ratings yet

- Introduction TitrationDocument30 pagesIntroduction TitrationlacaranjaredNo ratings yet

- Robin Kuckyr Selling Your Accounting Practice NewsletterDocument16 pagesRobin Kuckyr Selling Your Accounting Practice NewsletterWard WichtNo ratings yet

- Kec 553a Lab Manual DSP 20-21Document62 pagesKec 553a Lab Manual DSP 20-21sachinyadavv13No ratings yet

- Corporate Report 2017Document44 pagesCorporate Report 2017LOLA PATRICIA MORALES DE LA CUBANo ratings yet

- Helmke - Slipring MotorsDocument16 pagesHelmke - Slipring MotorssanmaworkNo ratings yet

- 11 - Past Simple Tense vs. Present PerfectDocument9 pages11 - Past Simple Tense vs. Present PerfectJosé SantosNo ratings yet

- JBL Tune 660NC SpecSheet EnglishDocument2 pagesJBL Tune 660NC SpecSheet EnglishCaroAntifazNo ratings yet

- R12 - Table/View Changes, Additions: Echnical OcumentDocument97 pagesR12 - Table/View Changes, Additions: Echnical OcumentSameer KulkarniNo ratings yet

- Cultivation of Algae - Photobioreactor - Oilgae - Oil From AlgaeDocument10 pagesCultivation of Algae - Photobioreactor - Oilgae - Oil From Algaeswetha chandrasekaranNo ratings yet

- Acr First Day Classes - EditedDocument5 pagesAcr First Day Classes - EditedBernard TerrayoNo ratings yet

- Histology of Umbilical Cord in MammalsDocument16 pagesHistology of Umbilical Cord in MammalsFia NisaNo ratings yet

- Ice ScrambbleDocument15 pagesIce ScrambbleJay ArNo ratings yet

- NISM-Investment Adviser - Level 1Document190 pagesNISM-Investment Adviser - Level 1Rohil SanilNo ratings yet

- Catalog LZB August-2023Document26 pagesCatalog LZB August-2023angga nugrahaNo ratings yet

- Antrenament - Caiet de Lucru Al AntrenoruluiDocument134 pagesAntrenament - Caiet de Lucru Al AntrenoruluialeksandraNo ratings yet

- RPMS Porfolio Template (Long)Document3 pagesRPMS Porfolio Template (Long)JohnCzyril Deladia DomensNo ratings yet

- Exit Ticket Report #7: SDG 7 Affordable & Clean Energy: Sample TemplateDocument2 pagesExit Ticket Report #7: SDG 7 Affordable & Clean Energy: Sample TemplateNino Joycelee TuboNo ratings yet

- Modern Solutions To Screen NG Problems: Mogensen SizerDocument8 pagesModern Solutions To Screen NG Problems: Mogensen SizerTsakalakis G. KonstantinosNo ratings yet

- Case Study CEMEX Students)Document6 pagesCase Study CEMEX Students)Alvin Amos100% (1)

- Bespoke Benchmarking PDFDocument2 pagesBespoke Benchmarking PDFDurga PrasadNo ratings yet

- A Study On Customer Relationship Management at Yamaha Srinivasa Motors PuducherryDocument6 pagesA Study On Customer Relationship Management at Yamaha Srinivasa Motors PuducherryEditor IJTSRDNo ratings yet

- Gr12 EnglishJIT P1 2020Document53 pagesGr12 EnglishJIT P1 2020NhlanhlakaziNo ratings yet

- Mongol Invasion in IndiaDocument4 pagesMongol Invasion in IndiaIsabella HannahNo ratings yet

- Aptitude Problems On Trains3 (WWW - Students3k.com)Document6 pagesAptitude Problems On Trains3 (WWW - Students3k.com)Srinivas RaghavanNo ratings yet

- CG ProgrammingDocument429 pagesCG ProgrammingAdi Nouashcinci100% (1)

- Chapter 12 BDocument3 pagesChapter 12 Bjuhi993No ratings yet

- 01 - Power System Protection-Basics and Breakers v2 (Revised) PDFDocument55 pages01 - Power System Protection-Basics and Breakers v2 (Revised) PDFJawwad Sadiq Ayon100% (1)

- Lab 4Document7 pagesLab 4HEMANILASHINII A P R THARMALINGAMNo ratings yet