Professional Documents

Culture Documents

Same2006 J Tissier

Uploaded by

Ganesan SOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Same2006 J Tissier

Uploaded by

Ganesan SCopyright:

Available Formats

MMIC/RFIC for receivers front-end

Jérôme Tissier

To cite this version:

Jérôme Tissier. MMIC/RFIC for receivers front-end. SAME 2006, Oct 2006, Sophia-Antipolis, France.

�hal-01130373�

HAL Id: hal-01130373

https://hal.archives-ouvertes.fr/hal-01130373

Submitted on 11 Mar 2015

HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est

archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents

entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non,

lished or not. The documents may come from émanant des établissements d’enseignement et de

teaching and research institutions in France or recherche français ou étrangers, des laboratoires

abroad, or from public or private research centers. publics ou privés.

SAME 2006 Forum

Session : Mixed Signal, RF, Communication.

MMIC/RFIC for receivers front-end

Jérôme TISSIER, ESEO

4, rue Merlet de la Boulaye - BP 30926 - 49009 Angers Cedex 01

France

Phone : +33(0)2 41 86 67 13 – Fax : +33(0)2 41 87 99 27- E-mail: jerome.tissier@eseo.fr

The Microwave Monolithic Integrated Circuits

(MMIC) design is a recent research axis developed

Abstract: at ESEO (for about three years). At the beginning,

two simple circuits, a mixer and a filtering

This paper deals with the work, realized in the amplifier, operating both at 5.8 GHz, have been

Electronics and Physics Department of ESEO realized, in a 0.2 µm GaAs process from OMMIC

(Graduate school of engineering in Electronics, (EDO2AH). For each circuit, a compromise has

Computer sciences, Telecommunication and been done between simplicity and performances in

Networks) in the area of MMIC and RFIC circuits order to obtain compactness (circuits have to be

for wireless applications. To be more precise, a implemented on the smallest chip size available

mixer, a filtering amplifier and Low Noise with this process, that is to say 1.5*1mm²), easily to

Amplifiers (LNA) will be presented in this article implement and easily to test structures with

in GaAs and SiGe technologies. sufficient characteristics for an integration in a

receiver front-end.

The use of the GaAs OMMIC process EDO2AH

Table of Contents of the paper was justified by the fact that it is a well known

process for microwave frequencies, with a

I. INTRODUCTION complete library (including spiral inductors) and

which is available for academic institutes by way of

II. DUAL-GATE MIXER the CMP (Multi-Projects Circuits) in Grenoble.

1. Circuit topology and layout But, for our frequency band (centred at 5.8 GHz), a

2. Simulation and measurement results simple SiGe BiCMOS process could be used. The

use of a SiGe process leads to compactness

III. FILTERING AMPLIFIIER structures, compatible with a CMOS process, with

1. Circuit topology and layout results as good as those obtained with a GaAs

2. Simulation and measurement results process (except for linearity). The drawback of this

kind of technology is that the library is not so

IV. WIDE BAND LOW NOISE AMPLIFIERS (LNA) complete than the GaAs one, specially concerning

1. Wide band SiGe LNA for 2.45 GHz and spiral inductors, which can cause some problems at

5.8 GHz ISM bands microwave frequencies.

2. Ultra Wide band GaAs LNA Nowadays, our field of interest is the Low Noise

Amplification. Two circuits are in development.

V. CONCLUSION The first one, use a 0.35 µm SiGe BiCMOS process

from AMS (available by way of the CMP) for the

reasons explained above. It is a wide band LNA

I. INTRODUCTION which have to operate in the two ISM bands,

centred at 2.45 GHz and 5.8 GHz

Nowadays, the frontier between analog processing The second one is an ultra wide band LNA

and digital processing is moving close to the designed to be used for UWB or Wimax

antenna. However, as the RF signal from the applications for example. The process used to

antenna cannot be directly digitally processed, Low design this Low Noise Amplifier is the GaAs

Noise Amplifiers (LNA), Power Amplifiers (PA) OMMIC process ED02AH.

and, to a lesser extent, mixers remain essential

components of receivers or transmitters front-end.

SAME 2006 Forum- October 4th & 5th 2006 1

II. DUAL-GATE MIXER

II-1. Circuit topology and layout

A double balanced mixer is frequently used in

communication systems [1] [2]. Balanced mixers

generally have better power-handling capabilities,

and higher isolation characteristic between ports

than unbalanced mixers. In addition, certain

spurious responses, LO noise, and spurious signals

can be rejected by balanced mixer scheme. Their

disadvantages are the need for greater LO power to Figure 2 : Dual-gate mixer layout

drive many nonlinear devices and the complicated

structure due to the external devices, such as balun

and many devices. Thus, it is often practical to use II-2 Simulated and measured results

a single device dual-gate FET mixer in applications

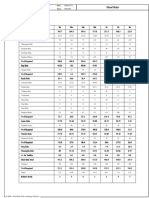

where a balanced mixer would otherwise be needed All the results are summarized in table 1.

[3] [4]. Although characteristics of this kind of

mixer are not so good as balanced mixer’s ones, the Simulated Measured

possibility of applying LO and RF to separated results results

gates without the use of baluns makes dual-gate Parameters Unit fRF = 5.8 GHz fRF = 5.8 GHz

fLO = 5.2 GHz fLO = 5.4 GHz

FET mixer easy to implement in MMIC technology PLO = 4 dBm PLO = 4 dBm

with sufficient performances for an integration in a PRF = -30dBm PRF = -30dBm

receiver front-end. That is why our mixer is based Conversion

dB 1.7 1.7

on a simple dual-gate P-HEMT mixer matched gain

simultaneously at its three ports, as shown in figure LO-IF Isolation dB 31 24

1. RF-IF Isolation dB 20 19

LO-RF

dB 12 -

Isolation

VGS2 P-HEMT Input P-1dB

6*50 µm -8.5

RP2 CP3 L3 IF Compression

LO L2 CP2 D dBm -

G

2 Output P-1dB -7.7

S LP Compression

C2

P-HEMT

Input IP3 dBm 3 -

VDS2 CP4 C3

6*50 µm

L1 CP1 16 -

RF D

NFSSB dB

1

RP1

G

S DC power mW <10 <10

C1

VGS1

Table 1. Simulated and measured results of the

dual-gate mixer

Figure 1 : Dual-gate mixer circuit topology This dual-gate mixer is a down-converter

This dual-gate mixer has been implemented mixer, operating at a 5.8 GHz RF frequency (ISM

on a chip of 1.5x1mm², using the 0.2 µm GaAs band). It has been designed to achieve gain

process (ED02AH) from OMMIC. The layout of conversion at an intermediate frequency of about

the circuit is shown in figure 2. 600 MHz, good LO-IF, RF-IF and LO-RF

isolations (≥ 20 dB), good linearity and low power

consumption (< 10 mW). An example of simulated

results obtained for an intermediate frequency of

600 MHz is presented on table 1. All the results are

closed to those expected, except for LO-RF

isolation which is not very high (risk of DC offset)

and for the noise figure which is not very good. All

these results have been confirmed in measure.

Because of the bad LO-RF isolation and a drift in

the EDO2AH process, the results obtained for a fIF

SAME 2006 Forum- October 4th & 5th 2006 2

of 600 MHz in simulation are obtained for a fIF of As for the first circuit, simulation results have

400 MHz in measurement. been confirmed by measurements thanks to our

To improve these characteristics we have microwave probe station. Good agreement between

decided to combine filtering and low noise simulated and measured results has been obtained,

amplification in a filtering amplifier. as shown on figure 5.

20

III. FILTERING AMPLIFIER Simulation

Measurement

10

dB(S(2,1))

III-1. Circuit topology and layout 0

-10

Unlike LNA, the filtering function does not

have its monolithic version yet. That is why we -20

have decided to implement on a same chip low 3 4 5

freq, GHz

6 7 8

noise amplification and filtering functions. This 0

filtering amplifier, based on a single P-HEMT -10

transistor cascaded with input/output matching and

dB(S(1,1))

-20 Simulation

filtering networks was designed to achieve 10 dB

gain at 5.8 GHz, good input/output matching, very -30

good linearity, a noise figure of 4 dB at 5.8 GHz -40

and a -3dB bandwith of about 1GHz (our filter is Measurement

-50

not selective enough but for sensitive problems we 3 4 5 6 7 8

have decided not to optimize this parameter). 0

freq, GHz

The topology used is presented in figure 3.

-10

P-HEMT

dB(S(2,2))

Simulation

6*40 µm CP2 C3 OUT -20

IN L1 L2 CP1 D

2 Measurement

G

S LP -30

L3

RP C4 L4

C1 C2 CP3

VDS -40

VGS

3 4 5 6 7 8

freq, GHz

-20

Simulation

Figure 3 : Filtering amplifier circuit topology -30

dB(S(1,2))

Measurement

-40

This filtering amplifier is implemented using

-50

the same monolithic technology as in the second

part. The chip size is always 1.5x1 mm². A -60

photograph of the circuit is shown in figure 4. 3 4 5 6 7 8

freq, GHz

Figure 5 : S parameters simulated and measured

Except the gain max which has a little bit

decreased (8 dB measured, certainly due to a drift

of the EDO2AH process), all the S parameters

measured are equivalent to those simulated.

Concerning input matching (S11), output matching

(S22) and isolation (S12), measurement is even better

than simulation.

The –1 dB compression point occurs for an

input power of about 5 dBm, which denote a good

linearity behaviour.

Figure 4 : Photograph of the filtering amplifier Concerning noise figure at central frequency

(5.8 GHz), it is equal to the minimum noise figure

of 4 dB which is quite low.

III-2. Simulated and measured

results

SAME 2006 Forum- October 4th & 5th 2006 3

IV. WIDE BAND LOW NOISE The simulated gain and the noise figure are

plotted on figure 8. The input and output matching

AMPLIFIERS (LNA) are plotted on figure 9.

IV-1. Wide band SiGe LNA for 2.45

GHz and 5.8 GHz ISM bands 50 6

5

40

IV-1-1. Circuit topology and layout 4

dB(S(2,1))

30

nf(2)

3

The transistor used is a bipolar transistor from 20

2

the AMS 0.35 µm SiGe process. To achieve high 10

1

gain, 30 unit transistors have been wired in parallel. 0 0

The advantage of this technique is to increase gain 0 2 4 6 8 10

freq, GHz

without increasing the noise figure (minimum noise

figure of n wired in parallel two-ports networks is

equal to the minimum noise figure of this two-ports

network) [5]. As explained in [5], a high load Figure 8 : SiGe LNA simulated gain and

impedance can improve input impedance Ze in simulated noise figure

order to obtain a good power matching. This high

load impedance can be realized by a simple

0 0

capacitor. We need then a second stage to achieve -2 -2

output matching. The topology obtained is -4 -4

dB(S(1,1))

dB(S(2,2))

presented in figure 6. -6 -6

-8 -8

C3 OUT -10 -10

C2

C1 1 2 30 -12 -12

IN 1 2 0 2 4 6 8 10

30

freq, GHz

L2

L1

Figure 9 : SiGe LNA input and output matching

Figure 6 : SiGe LNA circuit topology

We can achieve a gain of 28 dB and 16 dB at

respectively 2.45 GHz and 5.8 GHz. The noise

L1 and L2 are small inductors used to improve figure obtained at 2.45 GHz and 5.8 GHz is very

stability and matching. They will be replaced by low (1.2 dB and 2.4 dB) and the matching

transmission lines in the layout. parameters (S11 and S22) are ≤ -10 dB over all

In this figure, biasing elements do not appear. frequency band.

This biasing has been realized thanks to five PMOS

transistors. Four of them, act as current mirrors to

generate the base current and to bias the fifth, IV-2. Ultra wide band GaAs LNA

which have to supply the collector current wanted.

A layout of the circuit is presented in figure 7.

IV-2-1. Circuit topology and layout

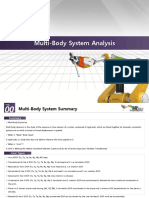

The topology, presented in figure 10, is a two

stages amplifier (to achieve about 20 dB

amplification on the 2-11 GHz band) with shunt

feedback on each stage to obtain broadband

matching and good noise figure [6].

CR2 RR2

CR1 RR1

P-HEMT

P-HEMT 6*50 µm CP4 OUT

6*50 µm CP2 D

IN CP1 Le D

G

2

G

1 S LP2

S LP1

RP

RP VDS CP3

CP3

Figure 7 : SiGe LNA layout VGS

VDS VGS

IV-1-2. Simulated results

Figure 10 : Ultra wide band LNA topology

SAME 2006 Forum- October 4th & 5th 2006 4

This dual-gate mixer has been implemented 0

on a chip of 1.5x1mm², using again the 0.2 µm -5

GaAs ED02AH process. The layout of the circuit is

dB(S(1,1))

shown in figure 11. -10

-15

-20

0 2 4 6 8 10 12

freq, GHz

-5

-10

dB(S(2,2))

-15

-20

-25

-30

Figure 11 : Ultra wide band LNA layout 0 2 4 6 8 10 12

freq, GHz

IV-2-2. Simulated results Figure 13: Ultra wide band LNA input and output

matching

The simulated gain is plotted on figure 12.

The input and output matching are plotted on figure

13. The noise figure is plotted on figure 14.

14

12

In the 2-11 GHz band we obtain a gain 10

contained between 23.4 dB (at 2GHz) and 19.1 dB 8

nf(2)

(at 11GHz). The noise figure is very low and below 6

2.3 dB over the all band (2.3 dB at 2 GHz and 1.8 4

2

dB at 11GHz), the input matching is good (S11 ≤ - 0

10 dB) and the output matching very good (S22 ≤ - 0 2 4 6 8 10 12

14 dB). This LNA will be again implemented on freq, GHz

the smallest chip size available with the ED02AH

process (1.5*1 mm²). This LNA will be sent to

Figure 14 : Ultra wide band LNA simulated noise

foundry soon.

figure

30

20 V. CONCLUSION

10

dB(S(2,1))

0

In this article, work realized at ESEO, in the

-10

MMIC/RFIC design area is presented. The first

-20

circuit developed is a dual-gate mixer with each

-30

0 2 4 6 8 10 12

port matched on the chip. Good characteristics have

freq, GHz been achieved according to the topology chosen,

except for the RF-LO isolation and the noise figure.

Figure 12 : Ultra wide band LNA simulated gain To improve this, a simple filtering amplifier based

upon a classical matching technique has been

designed, manufactured and tested, with excellent

agreement between simulation and measurement.

At present, our field of interest is the Low Noise

Amplification. Two circuits are in development,

using two different technologies. One uses the same

GaAs P-HEMT technology as for the dual-gate

mixer and filtering amplifier. This technology is

particularly interesting for having high gain and

very low noise in a very large microwave bandwith,

with good linearity. That is why the circuit

SAME 2006 Forum- October 4th & 5th 2006 5

developed with this technology is an ultra wide About the Authors

band (2-11 GHz) LNA for Wimax or UWB

applications. The second technology used is a

common 0.35 µm SiGe BiCMOS process from

AMS. It is used to design a wide band LNA, which

have to operate in the two ISM bands, centred at

2.45 GHz and 5.8 GHz. because the emitter width

is not small enough to allow sufficient gain at

higher frequencies. However, the design of an ultra

wide band LNA with an appropriate SiGe process

is possible and has still been published [7]. In fact,

nowadays, high frequencies SiGe processes are Jérôme TISSIER was born in Limoges, France,

joining two different domains, the microelectronic in October 1973. He received the PhD degree

domain and the microwave domain to design more from the University of Limoges in 2001. During

and more complicated and integrated chips. his PhD, at the Microwave and Optical

Communications Research Institute of Limoges

References (IRCOM) he has worked on active inductors,

negative resistances and active filters in MMIC

[1] J. Reina-Tosina, C. Crespo, J. I. Alonso, F. technology. Since 2002, he is an Associate

Pérez, "GaAs MMIC mixer based on the Professor at ESEO (Graduate school of

Gilbert cell with HEMTs biased on the engineering in Electronics, Computer sciences,

subthreshold region", Microwave and Optical Telecommunication and Networks), Angers, in

Technology Letters, vol. 28, n°4, Feb 2001, pp the Electronics and Physics Department. His

241-244. main field of interest is MMICs and more

[2] D. Dubuc, T. Parra, J. Graffeuil, "Original specially mixers and Low Noise Amplifiers for

topology of GaAs P-HEMT mixer", receivers front-end.

GaAs’2000, Paris, Oct 2000, pp 417-420.

[3] Eng Chuan Low and al., "A plastic package

GaAs MESFET 5.8 GHz receiver front-end

with on-chip matching for ETC", IEEE

Transactions on Microwave Theory and

Techniques, vol. 48, n°2, Feb 2000, pp 209-

213.

[4] Hyun II Kang and al., "An asymmetric GaAs

MMIC dual-gate mixer with improved

intermodulation characteristics", 1999 MTT-S

International Microwave Symposium Digest

vol.2 , pp 795-798.

[5] S. Bosse, S. Barth and al., "Conception d’un

LNA dans la bande [150 MHz – 2 GHz] en

technologie SiGe", 14èmes Journées

Nationales Microondes, May 2005.

[6] D. Eyllier, M.V. Cherkashin and al.,

"Utilisation d’une technique visuelle pour la

conception d’un LNA dans la bande 2-10 GHz

", 14èmes Journées Nationales Microondes,

May 2005.

[7] Y. Park, C.-H. Lee and al., "A very low power SiGe

LNA for UWB application", IEEE MTT-S Digest,

2005, vol. 2, pp. 1041-1044.

SAME 2006 Forum- October 4th & 5th 2006 6

You might also like

- 7.1.4.9 Lab - Identifying IPv4 AddressesDocument3 pages7.1.4.9 Lab - Identifying IPv4 AddressesEduardo Haro38% (16)

- Soyuer98 RAWCON Pp133-136 ACostEffectiveApproachtoShortRangeHighSpeedRadioDesign5GHzDocument4 pagesSoyuer98 RAWCON Pp133-136 ACostEffectiveApproachtoShortRangeHighSpeedRadioDesign5GHzTom BlattnerNo ratings yet

- A W-Band LNA/Phase Shifter With 5-dB NF and 24-mW Power Consumption in 32-nm CMOS SOIDocument10 pagesA W-Band LNA/Phase Shifter With 5-dB NF and 24-mW Power Consumption in 32-nm CMOS SOItoto byNo ratings yet

- Navigating LNA Microwave Integrated CircuitsDocument4 pagesNavigating LNA Microwave Integrated CircuitsArun KumarNo ratings yet

- Design of Low-Power Sub-2.4 DB Mean NF 5G Lnas Using Forward Body Bias in 22 NM FdsoiDocument10 pagesDesign of Low-Power Sub-2.4 DB Mean NF 5G Lnas Using Forward Body Bias in 22 NM FdsoiVarun DevNo ratings yet

- Integrated PAM2 Decision Feedback Equalizer For Gigabit Ethernet Over Standard SI-POF Using Red LEDDocument3 pagesIntegrated PAM2 Decision Feedback Equalizer For Gigabit Ethernet Over Standard SI-POF Using Red LEDzygmunt60No ratings yet

- RF Integrated Circuits in Standard CMOS TechnologiesDocument8 pagesRF Integrated Circuits in Standard CMOS TechnologiesSaitejaTallapellyNo ratings yet

- Multi-Standard Receiver DesignDocument54 pagesMulti-Standard Receiver DesignWalid_Sassi_TunNo ratings yet

- A 2 X 2 MIMO DVB-T2 System: Design, New Channel Estimation Scheme and Measurements With Polarization DiversityDocument9 pagesA 2 X 2 MIMO DVB-T2 System: Design, New Channel Estimation Scheme and Measurements With Polarization DiversityAdi SitorusNo ratings yet

- 10.1109-IDT.2008.4802471-System Level Design of Radio Frequency Receiver For IEEE 802.16 StandardDocument5 pages10.1109-IDT.2008.4802471-System Level Design of Radio Frequency Receiver For IEEE 802.16 StandardAsghar FarhadiNo ratings yet

- Asic Implementation of A Mimo-Ofdm Transceiver For 192 Mbps WlansDocument4 pagesAsic Implementation of A Mimo-Ofdm Transceiver For 192 Mbps WlanscommonsunguruNo ratings yet

- Low-Profile Wideband Four-Corner-Fed Square Patch Antenna For 5G MIMO Mobile Antenna ApplicationDocument5 pagesLow-Profile Wideband Four-Corner-Fed Square Patch Antenna For 5G MIMO Mobile Antenna Applicationrajesh yadavNo ratings yet

- Low-Power Low-Voltage CMOS RF MixersDocument12 pagesLow-Power Low-Voltage CMOS RF MixersanirudhdagameNo ratings yet

- A CMOS Receiver Front-End For 3.1-10.6 GHZ Ultra-Wideband RadioDocument4 pagesA CMOS Receiver Front-End For 3.1-10.6 GHZ Ultra-Wideband RadioĂbđÃłłÄH H㊪ãÑNo ratings yet

- HAMADA - A FULLY INTEGRATED 2x1 DUAL-BAND DIRECT-CONVERSION MOBILE WiMAX TRANSCEIVERDocument11 pagesHAMADA - A FULLY INTEGRATED 2x1 DUAL-BAND DIRECT-CONVERSION MOBILE WiMAX TRANSCEIVERmanasNo ratings yet

- A R Econfigurable L Ow I F - Z Ero I F R Eceiver Architecture F or Multi Standard Wireless Systems Using A Reconfigurable FilterDocument12 pagesA R Econfigurable L Ow I F - Z Ero I F R Eceiver Architecture F or Multi Standard Wireless Systems Using A Reconfigurable Filterjmicrojouranl1No ratings yet

- V-Band GaAs Metamorphic Low-Noise Amplifier Design Technique For Sharp Gain Roll-Off at Lower FrequenciesDocument4 pagesV-Band GaAs Metamorphic Low-Noise Amplifier Design Technique For Sharp Gain Roll-Off at Lower Frequencieskarthik srivatsa mbNo ratings yet

- Lorawan CRDocument5 pagesLorawan CRMaria Clara Santos QueirozNo ratings yet

- A Fully Integrated Radio-Fiber InterfaceDocument3 pagesA Fully Integrated Radio-Fiber InterfaceSana FatimaNo ratings yet

- A Dual-Band Multiport MIMO Slot Antenna For WLAN ApplicationsDocument4 pagesA Dual-Band Multiport MIMO Slot Antenna For WLAN ApplicationsDinindiraKesaktianningtyasNo ratings yet

- 08268871Document4 pages08268871ChandreshSinghNo ratings yet

- Brochure ALFO - BS.00030.E-001Document16 pagesBrochure ALFO - BS.00030.E-001Ailton PAPANo ratings yet

- Filterbank Based Multi Carrier Transmission (FBMC) - Evolving OFDMDocument8 pagesFilterbank Based Multi Carrier Transmission (FBMC) - Evolving OFDMdfhgNo ratings yet

- A Dual-Band Multiport MIMO Slot Antenna For WLAN ApplicationsDocument4 pagesA Dual-Band Multiport MIMO Slot Antenna For WLAN Applicationsgf.msaniNo ratings yet

- Assessment of Gigabit Ethernet Technology For The Lofar Multi-Terabit NetworkDocument4 pagesAssessment of Gigabit Ethernet Technology For The Lofar Multi-Terabit Networknaresh507No ratings yet

- Un Módulo Frontal Compacto BiFET para 802 y 802.16e RX Utilizando Un Filtro TriplexorDocument4 pagesUn Módulo Frontal Compacto BiFET para 802 y 802.16e RX Utilizando Un Filtro TriplexorDaniel Elmer Parado SosaNo ratings yet

- TMNL Open Doors Transport Network Training - Part1Document51 pagesTMNL Open Doors Transport Network Training - Part1Chelu Marius-FlorinNo ratings yet

- A 1.5V 1.5GHz CMOS LNADocument16 pagesA 1.5V 1.5GHz CMOS LNAptt3iNo ratings yet

- 2.4-Ghz Single-Ended Input Low-Power Low-Voltage Active Front-End For Zigbee Applications in 90 NM CmosDocument4 pages2.4-Ghz Single-Ended Input Low-Power Low-Voltage Active Front-End For Zigbee Applications in 90 NM CmosdilixyzNo ratings yet

- A Dual-Broadband MIMO Antenna System For GSM/UMTS/LTE and WLAN HandsetsDocument4 pagesA Dual-Broadband MIMO Antenna System For GSM/UMTS/LTE and WLAN Handsetsmsh-666No ratings yet

- 48 GHZ LNAdesignfora HASSTransponderusing in Ga Asp HEMTTechnologyDocument5 pages48 GHZ LNAdesignfora HASSTransponderusing in Ga Asp HEMTTechnologyten nheNo ratings yet

- A 1.5-V, 1.5-GHz CMOS Low Noise Amplifier - Solid-State Circuits, IEEE Journal of PDFDocument15 pagesA 1.5-V, 1.5-GHz CMOS Low Noise Amplifier - Solid-State Circuits, IEEE Journal of PDFAnirban HomroyNo ratings yet

- Ijisa V4 N9 9Document7 pagesIjisa V4 N9 9Đức QuangNo ratings yet

- Microcoll 1999 BEReff PDFDocument6 pagesMicrocoll 1999 BEReff PDFAttila HiltNo ratings yet

- Reduced Complexity Decision Feedback Equalizer For Supporting High Mobility in WimaxDocument5 pagesReduced Complexity Decision Feedback Equalizer For Supporting High Mobility in Wimaxjoy0302No ratings yet

- Toward Single Lane 200G Optical Interconnects With Silicon Photonic ModulatorDocument8 pagesToward Single Lane 200G Optical Interconnects With Silicon Photonic ModulatorRaad Sami FyathNo ratings yet

- A 1.5-V 1.5-GHz CMOS Low Noise Amplifier Shafer IEEE JSSC 97Document15 pagesA 1.5-V 1.5-GHz CMOS Low Noise Amplifier Shafer IEEE JSSC 97Abid MullaNo ratings yet

- Lna Project PDFDocument56 pagesLna Project PDFPranjal JalanNo ratings yet

- DesignDocument13 pagesDesignPankaj pandeyNo ratings yet

- Design and Analysis of High-Gain and Compact Single-Input Differential-Output Low Noise Amplifier For 5G ApplicationsDocument4 pagesDesign and Analysis of High-Gain and Compact Single-Input Differential-Output Low Noise Amplifier For 5G Applicationskarthik srivatsa mbNo ratings yet

- A 1 - 57-GHz RF Front-EndDocument8 pagesA 1 - 57-GHz RF Front-EndSreedevi MenonNo ratings yet

- TD CAB Intermodulation PDFDocument5 pagesTD CAB Intermodulation PDFEstrella AlemanNo ratings yet

- Isolation Enhancement of A Very Compact UWB-MIMO Slot Antenna With Two Defected Ground StructuresDocument4 pagesIsolation Enhancement of A Very Compact UWB-MIMO Slot Antenna With Two Defected Ground StructuresSrikar DNo ratings yet

- 5g Design Best Practices White PaperDocument13 pages5g Design Best Practices White PaperOrlando MedinaNo ratings yet

- Design of Mm-Wave Mic Frequency Multipliers and Mixers Using Simple Microstrip High-Pass FiltersDocument4 pagesDesign of Mm-Wave Mic Frequency Multipliers and Mixers Using Simple Microstrip High-Pass Filterskoke_8902No ratings yet

- A 24-GHz CMOS Transceiver For BluetoothDocument10 pagesA 24-GHz CMOS Transceiver For Bluetoothпавел панаринNo ratings yet

- A 28-Nm Fd-Soi 115-Fs Jitter Pll-Based Lo System For 24-30-Ghz Sliding-If 5G TransceiversDocument13 pagesA 28-Nm Fd-Soi 115-Fs Jitter Pll-Based Lo System For 24-30-Ghz Sliding-If 5G TransceiverstranNo ratings yet

- An Analogue Front-End Architecture For Software Defined RadioDocument4 pagesAn Analogue Front-End Architecture For Software Defined RadiorbsantiNo ratings yet

- A CSRR Loaded MIMO Antenna System For ISM Band OperationDocument10 pagesA CSRR Loaded MIMO Antenna System For ISM Band OperationAbdullah MadniNo ratings yet

- Assignment On Gp3 - LNA - Ver2Document8 pagesAssignment On Gp3 - LNA - Ver2SamreenNo ratings yet

- 2012.08.06 Osn - 1800 - R3 - CWDM & DWDMDocument45 pages2012.08.06 Osn - 1800 - R3 - CWDM & DWDMvictoriovegaNo ratings yet

- 1-Bandwidth Enhancement in Band Pass Filter BPF Using Microstrip Couple Lines For WLAN 2.4GHZ ApplicationsDocument4 pages1-Bandwidth Enhancement in Band Pass Filter BPF Using Microstrip Couple Lines For WLAN 2.4GHZ ApplicationsJohn JohnNo ratings yet

- Semiconductor Today - Transcending Frequency and Integration LimitsDocument4 pagesSemiconductor Today - Transcending Frequency and Integration Limitsnobody126No ratings yet

- Artículo1 PDFDocument6 pagesArtículo1 PDFDania Largo JaimesNo ratings yet

- WICAT SC-FDMA Workshop: A Review of OFDMA and SC-FDMA and Some Recent ResultsDocument24 pagesWICAT SC-FDMA Workshop: A Review of OFDMA and SC-FDMA and Some Recent ResultsectklaNo ratings yet

- A 128/512/1024/2048-Point Pipeline Fft/Ifft Architecture For Mobile WimaxDocument2 pagesA 128/512/1024/2048-Point Pipeline Fft/Ifft Architecture For Mobile Wimaxsaravanany5kNo ratings yet

- GaN-on-SiC LNA For UHF and L-BandDocument4 pagesGaN-on-SiC LNA For UHF and L-BandQazi KamalNo ratings yet

- CMN511 RW1Document22 pagesCMN511 RW1Sean Matthew L. OcampoNo ratings yet

- Noise Cancellation in OFDM Systems Using Adaptive Complex Narrowband IIR FilteringDocument5 pagesNoise Cancellation in OFDM Systems Using Adaptive Complex Narrowband IIR Filteringfilip bNo ratings yet

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDFrom EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDNo ratings yet

- KAS IntroDocument2 pagesKAS IntroGanesan SNo ratings yet

- PCB Trace Width Calculator - Trace Width vs. Current TableDocument5 pagesPCB Trace Width Calculator - Trace Width vs. Current TableGanesan SNo ratings yet

- Predicting Fusing Time of Overloaded PCB Traces Can We Predict It at All - With Douglas Brooks, PHD and Dr. Johannes Adam - ARTECH HOUSE INSIDERDocument12 pagesPredicting Fusing Time of Overloaded PCB Traces Can We Predict It at All - With Douglas Brooks, PHD and Dr. Johannes Adam - ARTECH HOUSE INSIDERGanesan SNo ratings yet

- Final - Radio Technology WuDocument15 pagesFinal - Radio Technology WuGanesan SNo ratings yet

- Gap Analysis of GNSS Receivers and Technology: GSA-227890 GRAMMAR D1.4 Version 1.17Document72 pagesGap Analysis of GNSS Receivers and Technology: GSA-227890 GRAMMAR D1.4 Version 1.17Ganesan SNo ratings yet

- Angelina Jolie Shad BalaDocument1 pageAngelina Jolie Shad BalaGanesan S100% (1)

- 25 Myths About PATENTS Demystified EbookDocument52 pages25 Myths About PATENTS Demystified EbookGanesan SNo ratings yet

- Installation Guide of AstrotransitDocument3 pagesInstallation Guide of AstrotransitGanesan SNo ratings yet

- Angelina Jolie VARSHAPHALADocument1 pageAngelina Jolie VARSHAPHALAGanesan SNo ratings yet

- Prepared and Compiled by Govindon Gopalan (Harish)Document1 pagePrepared and Compiled by Govindon Gopalan (Harish)Ganesan SNo ratings yet

- Using PATENTS To Reduce R&D Efforts: First Edition 2016Document31 pagesUsing PATENTS To Reduce R&D Efforts: First Edition 2016Ganesan SNo ratings yet

- New Thermasim™ Online Mosfet Thermal Simulation ToolDocument4 pagesNew Thermasim™ Online Mosfet Thermal Simulation ToolGanesan SNo ratings yet

- Intellectual Property Rights: Handbook OnDocument50 pagesIntellectual Property Rights: Handbook OnGanesan SNo ratings yet

- Unep Pops Nip Belgium 1.englishDocument115 pagesUnep Pops Nip Belgium 1.englishGanesan SNo ratings yet

- Rarnasu: Sub: - Contactless Book Scanner RegDocument1 pageRarnasu: Sub: - Contactless Book Scanner RegGanesan SNo ratings yet

- Thermal Management of Visible Leds: Application Bulletin 228Document4 pagesThermal Management of Visible Leds: Application Bulletin 228Ganesan SNo ratings yet

- A11 MBS (Analyst)Document15 pagesA11 MBS (Analyst)Ganesan SNo ratings yet

- VG 224 ConfigurationDocument6 pagesVG 224 Configurationelderly4meNo ratings yet

- Sophos CompetitiveDocument15 pagesSophos CompetitiveLaksmana WiranggaNo ratings yet

- Distributed Beamforming Techniques For Cell-Free Wireless Networks Using Deep Reinforcement LearningDocument16 pagesDistributed Beamforming Techniques For Cell-Free Wireless Networks Using Deep Reinforcement Learningwho3No ratings yet

- 3 LTE eRAN17.1 ANR ManagementDocument151 pages3 LTE eRAN17.1 ANR ManagementAhmed Yunes100% (1)

- Sony KDL-26 32 37 FA400 Chassis MA2Document25 pagesSony KDL-26 32 37 FA400 Chassis MA2Kike BelloNo ratings yet

- IC 756pro3Document118 pagesIC 756pro3larsNo ratings yet

- Different Channel Coding Techniques in MIMO-OFDMDocument5 pagesDifferent Channel Coding Techniques in MIMO-OFDMHameed Ullah MarwatNo ratings yet

- Bus Tracking With Emergency System: TH TH TH TH TH TH THDocument2 pagesBus Tracking With Emergency System: TH TH TH TH TH TH THScientist SakthivelNo ratings yet

- MOS Controlled Thyristor Group 7Document9 pagesMOS Controlled Thyristor Group 7cj gamatNo ratings yet

- Bit Error Ratio BER in DVB As A Function of S/N: Application NoteDocument16 pagesBit Error Ratio BER in DVB As A Function of S/N: Application NoteIndra Al-KahfiNo ratings yet

- Bluetooth HM-13 enDocument22 pagesBluetooth HM-13 enNicolas Prudencio RojasNo ratings yet

- Hypersat PDFDocument49 pagesHypersat PDFjobelleNo ratings yet

- Wide 6 V To 75 V Input Voltage Synchronous Buck Controller: FeaturesDocument42 pagesWide 6 V To 75 V Input Voltage Synchronous Buck Controller: FeaturesDhananjayNo ratings yet

- GATE 2012 Solution / GATE 2012 Answer KeyDocument1 pageGATE 2012 Solution / GATE 2012 Answer KeyEii RK RajeshNo ratings yet

- G7104A MultiMaster - REV 1.5.5-1 PDFDocument196 pagesG7104A MultiMaster - REV 1.5.5-1 PDFxufoNo ratings yet

- Error Detecting and Correcting Codes PDFDocument2 pagesError Detecting and Correcting Codes PDFNicoleNo ratings yet

- UPC-V315-QM77 UMN v1.00Document148 pagesUPC-V315-QM77 UMN v1.00علي ابوبكر عليNo ratings yet

- VAP User ManualDocument7 pagesVAP User ManualClara SuysNo ratings yet

- Sonus Routing Made Easy: A Background Info and ScenarioDocument6 pagesSonus Routing Made Easy: A Background Info and ScenarioMichel DinhNo ratings yet

- 02.signaling in Telcom NW and SSTPDocument15 pages02.signaling in Telcom NW and SSTPVINAY TANWARNo ratings yet

- Contents:: Part 1: Trends in Hipath 4000 Development Part 2: Ip Distributed ArchitectureDocument22 pagesContents:: Part 1: Trends in Hipath 4000 Development Part 2: Ip Distributed Architecturesumansonu23No ratings yet

- Chapter 4 Exam Style QuestionsDocument10 pagesChapter 4 Exam Style QuestionsHưng DzNo ratings yet

- DX-D 100 Wireless V5 - List of Service DocumentsDocument6 pagesDX-D 100 Wireless V5 - List of Service DocumentsEng-Eslam HassaanNo ratings yet

- Cyber Security Chapter 4Document13 pagesCyber Security Chapter 4Omar YasserNo ratings yet

- Disjointed Layer 2 Networks in X-UCS Intersight MMDocument48 pagesDisjointed Layer 2 Networks in X-UCS Intersight MMsalist3kNo ratings yet

- Lecture 4 - Implementing Logic in CMOSDocument32 pagesLecture 4 - Implementing Logic in CMOSsadia santaNo ratings yet

- Advanced Image Processing For Defense and Security ApplicationsDocument615 pagesAdvanced Image Processing For Defense and Security Applicationsonline servicesNo ratings yet

- Ruggedserver™ - Rs400: "Industrially Hardened"Document2 pagesRuggedserver™ - Rs400: "Industrially Hardened"Guillermo LizzanoNo ratings yet

- Manual EZCAP 295Document26 pagesManual EZCAP 295Luiz MalafaiaNo ratings yet