Professional Documents

Culture Documents

2021-1 EE2111 TTS CK De1 FIN

2021-1 EE2111 TTS CK De1 FIN

Uploaded by

Thắng Lê KimOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

2021-1 EE2111 TTS CK De1 FIN

2021-1 EE2111 TTS CK De1 FIN

Uploaded by

Thắng Lê KimCopyright:

Available Formats

TRƯỜNG ĐẠI HỌC BÁCH KHOA HÀ NỘI ĐỀ THI CUỐI KỲ 2021.

1

TRƯỜNG ĐIỆN – ĐIỆN TỬ Học phần: EE2111 – ĐIỆN TỬ TƯƠNG TỰ VÀ

SỐ

Đề số: 01 Tổng số trang: 2 Ngày thi: 07/02/2022

Thời gian làm bài: 90 phút

(Được sử dụng tài liệu)

Ký Trưởng nhóm/Giảng viên phụ trách HP: Khoa phụ trách HP:

duyệt

Nguyễn Quốc Cường

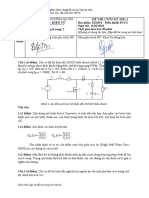

Câu 1 (2.5 điểm) Cho mạch điện với các thông số như hình dưới.

a. Biết V1=18Vdc, các diode là lý tưởng. Hãy tính dòng điện chảy qua R1, R2, R3

(1 điểm)

b. Biết V1 có dạng xung tam giác với chu kỳ 10ms, giá trị đỉnh là ±24Vdc, các

diode có VON= 0.7Vdc . Hãy phân tích và vẽ dạng điện áp trên R3 (1.5 điểm)

Câu 2 (1 điểm) Cho mạch ở Hình 2

a. Tính điện áp Ura1.

b. Vẽ đồ thị Ura1(t)

-------------------- Hết ------------------------

Câu 3 (1.5 điểm) Cho mạch ở Hình 3.

Cho biết Uvao(t) = 2V sin300t, Uref = -1V, +Vs=11V, -Vs = -11V

a. Hãy xác định các điểm chyển trạng thái và vẽ đặc tuyến Ura2 = f(Uvao)

b. Vẽ hình dạng của điện áp Ura2( t) theo các điểm chuyển trạng thái trên Uvao(t)

Câu 4 (3 điểm) Cho hàm Q(A,B,C,D) = ∏(0,2,3,7,8,9,13,14)

a. Hãy thành lập mạch logic của hàm Q sử dụng các cổng logic cơ bản (1 điểm)

b. Hãy thành lập mạch logic của hàm Q sử dụng các NAND 2 đầu vào (1 điểm)

c. Hãy thành lập mạch logic của hàm Q sử dụng 1 phần tử MUX 4 kênh dữ liệu và

các cổng logic cơ bản (1 điểm)

Câu 5 (1 điểm) Cho mạch logic như hình dưới.

Biết thời gian trễ truyền đạt của các cổng logic AND, OR, NOT, XOR lần lượt là 20ns,

30ns, 15ns, 40ns. Hãy tính thời gian trễ truyền đạt của mạch

Câu 6 (1 điểm) Cho mạch logic dãy như hình dưới.

Biết trạng thái logic ban đầu của các đầu ra Q là 0. Hãy lập bảng để xác định trạng trái

logic của các đầu ra Q tương ứng với 5 chu kỳ clock tiếp theo

-------------------- Hết ------------------------

You might also like

- Đề 1 cuối kỳ EE2110 2023.1Document4 pagesĐề 1 cuối kỳ EE2110 2023.1levanbe820No ratings yet

- Dethi 05 LTM2 Ky20211Document1 pageDethi 05 LTM2 Ky20211Trung Phạm ĐứcNo ratings yet

- Đề thi Mạch GKDocument2 pagesĐề thi Mạch GKvuanhquan12112k3No ratings yet

- 20211-KTDT - ET2012 - GK20211 - de 2Document1 page20211-KTDT - ET2012 - GK20211 - de 2Long ĐặngNo ratings yet

- Dethi 01 LTM2 Ky20211Document1 pageDethi 01 LTM2 Ky20211Thành Nguyễn TrungNo ratings yet

- LTM2-20221 - Cuoi Ky 4 deDocument4 pagesLTM2-20221 - Cuoi Ky 4 deNgô Văn SangNo ratings yet

- KTDT ET2012 GK20211 De1 ThaoDocument1 pageKTDT ET2012 GK20211 De1 ThaoĐức Trung Hiếu PhạmNo ratings yet

- Đề 1 giữa kỳ ĐTTT 128980Document1 pageĐề 1 giữa kỳ ĐTTT 128980Trung ĐôNo ratings yet

- 2023.1-LTM2-Cuoi Ky-4 deDocument4 pages2023.1-LTM2-Cuoi Ky-4 devanthanhbn133No ratings yet

- De So 01Document1 pageDe So 01lddl041221No ratings yet

- đề 4Document1 pageđề 4Thắng NguyễnNo ratings yet

- Đề 2 giữa kỳ ĐTTT 128980Document1 pageĐề 2 giữa kỳ ĐTTT 128980Trung ĐôNo ratings yet

- đề 3Document1 pageđề 3Thắng NguyễnNo ratings yet

- Đề-thi 20211Document1 pageĐề-thi 20211benhzxc92No ratings yet

- 20222-LTM1-Giua Ky-100 De-Ver 2Document2 pages20222-LTM1-Giua Ky-100 De-Ver 2Huy Phương VănNo ratings yet

- EE2111 20202 CK Đề 1Document1 pageEE2111 20202 CK Đề 1quan le anhNo ratings yet

- 2022.2-Giua Ky-Son 01Document3 pages2022.2-Giua Ky-Son 01vanthanhbn133No ratings yet

- Da Ii 16-17 Clc-Bael340662-DtcbDocument5 pagesDa Ii 16-17 Clc-Bael340662-DtcbPhúc Thiên PhạmNo ratings yet

- Đề thi - Điện tử tương tụ ĐHBKHNDocument1 pageĐề thi - Điện tử tương tụ ĐHBKHNtranquochuwngNo ratings yet

- Báo Cáo M CH 1Document15 pagesBáo Cáo M CH 1bao1472001No ratings yet

- TKDT Đề 2Document2 pagesTKDT Đề 2Tú HoàngNo ratings yet

- ĐTCS CK - HK3.14.15Document3 pagesĐTCS CK - HK3.14.15Trí ToànNo ratings yet

- Đề 3 Thi Ket Thuc Học Phần KT Cảm Biến (Da Ki)Document1 pageĐề 3 Thi Ket Thuc Học Phần KT Cảm Biến (Da Ki)Linh Nguyen Tien100% (1)

- Một số đề thi LTM1Document12 pagesMột số đề thi LTM1Đại KhắcNo ratings yet

- Một số đề LTM1Document29 pagesMột số đề LTM1Nguyễn HiệpNo ratings yet

- EE2110 20202 CK Đề 1-FINDocument1 pageEE2110 20202 CK Đề 1-FINDuc DaoNo ratings yet

- De 01 - 2021 - 2Document2 pagesDe 01 - 2021 - 2khailol4321No ratings yet

- 20202Document2 pages20202Nguyễn ĐiệpNo ratings yet

- Đề số 1Document1 pageĐề số 1Văn Nhật ĐoànNo ratings yet

- De So 2 TNDocument1 pageDe So 2 TNThành Nguyễn TrungNo ratings yet

- Câu 1 (3 điểm) : Họ và tên SV: MssvDocument1 pageCâu 1 (3 điểm) : Họ và tên SV: MssvAn TranNo ratings yet

- Đề thi cuối kì mạch điện, ĐH SPKT TP HCM PDFDocument2 pagesĐề thi cuối kì mạch điện, ĐH SPKT TP HCM PDFMân Trần Lê100% (1)

- 2022 12 08 Đề thi VLĐC 2 - HK1Document6 pages2022 12 08 Đề thi VLĐC 2 - HK1Long Nguyễn HoàngNo ratings yet

- De Thi KTSCT Aug10-2021Document2 pagesDe Thi KTSCT Aug10-2021Loan NguyễnNo ratings yet

- Đề thi KTĐDocument3 pagesĐề thi KTĐhieundNo ratings yet

- Tong Hop de Thi DTTT - Dts - Tkhts 2Document14 pagesTong Hop de Thi DTTT - Dts - Tkhts 2Thắng Lê KimNo ratings yet

- EE2110 20202 CK Đề 3-FINDocument1 pageEE2110 20202 CK Đề 3-FINAAnh Nguyễn ThếNo ratings yet

- 2021-LTT-Final - de 3Document1 page2021-LTT-Final - de 3Nguyễn ĐiệnNo ratings yet

- Long Dethi LTM2 2021-1-01-GKDocument1 pageLong Dethi LTM2 2021-1-01-GKsang nguyễn thịNo ratings yet

- DeKiemTra CSKTD HK192 CodapanDocument6 pagesDeKiemTra CSKTD HK192 CodapanMinh TrầnNo ratings yet

- De So 1 TNDocument1 pageDe So 1 TNThành Nguyễn TrungNo ratings yet

- Đề Thi-CA 2-Công Nghệ Mạng TTQ Online C.ngaDocument1 pageĐề Thi-CA 2-Công Nghệ Mạng TTQ Online C.ngaTrần Đăng Khoa- B18DCVT237No ratings yet

- Câu 1 (3 điểm) : Họ và tên SV: MssvDocument1 pageCâu 1 (3 điểm) : Họ và tên SV: MssvAn TranNo ratings yet

- Cuoi Ky Thao 01Document1 pageCuoi Ky Thao 01vanthanhbn133No ratings yet

- Đáp-Án HK211 GT HTĐ CQDocument5 pagesĐáp-Án HK211 GT HTĐ CQCảnh NguyễnNo ratings yet

- ĐK ĐTCS ĐỀ 4Document2 pagesĐK ĐTCS ĐỀ 4Hoàng Chu ĐứcNo ratings yet

- 2022-LC1-Final - 80 deDocument2 pages2022-LC1-Final - 80 dechâu nguyễn ngọcNo ratings yet

- ĐK ĐTCS ĐỀ 1Document2 pagesĐK ĐTCS ĐỀ 1Hoàng Chu ĐứcNo ratings yet

- Câu 1 (3 điểm) : (Được sử dụng tài liệu; nộp lại đề thi cùng bài làm)Document1 pageCâu 1 (3 điểm) : (Được sử dụng tài liệu; nộp lại đề thi cùng bài làm)Dương LêNo ratings yet

- ĐK ĐTCS ĐỀ 2Document2 pagesĐK ĐTCS ĐỀ 2Hoàng Chu ĐứcNo ratings yet

- HW01 CHHKDDocument21 pagesHW01 CHHKD05. Hà Xuân CátNo ratings yet

- De Thi Dien Tu Cong Suat - Thi Lai CD DIEN 09A, BDocument4 pagesDe Thi Dien Tu Cong Suat - Thi Lai CD DIEN 09A, BVü PhämNo ratings yet

- Trường Đại Học Giao Thông Vận Tải Thành Phố Hồ Chí Minh Đề Kiểm Tra Giữa Kỳ Tên học phần: …Giải Tích Mạch…………….Document4 pagesTrường Đại Học Giao Thông Vận Tải Thành Phố Hồ Chí Minh Đề Kiểm Tra Giữa Kỳ Tên học phần: …Giải Tích Mạch…………….namvv4584No ratings yet

- Kiem Tra 5Document6 pagesKiem Tra 5plongdz9No ratings yet

- PHIẾU GIAO BÀI THỰC HÀNH - TX3Document2 pagesPHIẾU GIAO BÀI THỰC HÀNH - TX3VĂN NGUYỄN NBNo ratings yet

- De MauDocument7 pagesDe MauHAVADA MusicNo ratings yet

- BT điện tửDocument39 pagesBT điện tửLogitnet 2No ratings yet

- Nhóm 2 123tmndt02 St2Document24 pagesNhóm 2 123tmndt02 St2Lợi NguyễnNo ratings yet

- Đa2 đt2Document7 pagesĐa2 đt2PhongNo ratings yet