Professional Documents

Culture Documents

10 Bit Current Steering DAC in CMOS 130n

Uploaded by

SRIGHAKOLLAPU AJITHOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

10 Bit Current Steering DAC in CMOS 130n

Uploaded by

SRIGHAKOLLAPU AJITHCopyright:

Available Formats

IJSART - Volume 2 Issue 10 –OCTOBER 2016 ISSN [ONLINE]: 2395-1052

10-Bit Current Steering DAC in CMOS 130nm

Technology

KolupuriKiran Kumar1, Ashok Kumar Adepu2

1, 2 Department of ECE

1MVGR College of Engineering

2 Assistant Professor, MVGR College of Engineering

Abstract- This paper proposed a 10-bit current steering The current source used here has no capacitance so the

(segmented architecture)digital-to-analog converter, with circuits need not to be charge or discharge in ON state. For high

different sizes of current sources. The proposed 10-bit digital- speed and high resolution designs current steering Digital to

to-analog converter was implemented using TSMC CMOS 130 Analog Converters are more suitable. As frequencies and

nm 1P2M technology. The power consumption was conversion rates increases, frequency domain parameters like

approximately 23.015 mW at the sample rate of 200 MHz, and SNR, SFDR parameters become more useful than static

the supply voltage was 3.3 V. It achieved a DNL (differential parameters like INL and DNL.

nonlinearity) and an INL (integral nonlinearity) of 0.06 LSB

and 0.04 LSB, respectively. In segmented (4LSB-6MSB) The static performance of DACs such as DNL and INL

architecture the measured SFDR (spurious free dynamic range) must be considered, as well as the dynamic performance of

was 88.156 dB. This work presented a good performance DACs such as SFDR. A DNL should be smaller than 1 LSB,

compared with other researches in DNL, INL and area. and the DAC converter should be kept monotonic. Every

increase of the digital input code increases the analog output

Keywords- Current steering DAC, Current source, INL, DNL, value. The DNL is always smaller than 1 LSB if the INL is

SFDR, Area. smaller than 0.5 LSB. An INL should be less than 0.5 LSB,

which ensures that the maximum linearity error is smaller than

I. INTRODUCTION the maximum quantization error.

Real world signals are in analog form but digital II. CIRCUIT ANDLAYOUT

signals are processed easily with simple circuits so analog

signals are converted into digital form. The digital signals are 2.1 BA DECODER

converted back to analog form to do some practical functions.

The circuit that perform this conversions are digital-to-analog Fig.1. shows the 2-bit Binary to Abacus decoder. It

converters, and at the output of this DACs load is connected. In consisted of AND gate and OR gate.S0-S2are the control

this paper CMOS current steering DAC is designed with BA signals for current source. The Binary to Abacus (BA) module

decoders, current sources and resistor at the output stage. uses to transform binary code (I1I0)2 to 3 thermometric codes

(S2S1S0).The output current of the current source is I0i.e 1mA.

Basically there are three types of current steering This DAC uses a BA decoder instead of conversional decoding

architectures unary array, binary array, and segmented array construction, which provides some advantages. The BA

architecture. Unary current DACs use a single-current element decoder contains one AND gate and one OR gate. The

for each quantization step. Unary current DACs are analogous advantages of the BA decoder are a reduction of DAC circuit

to resistor divider DACs with a resistor element for each LSB. complexity, delay and power consumption respectively. All

The drawback of unary arrays is that the complexity of the these gates are implemented using CMOS logic. This requires

digital decoder is exponentially related to the resolution. Binary six transistors for each logic gate. Fig.2. shows 4-bit BA

current DACs group current elements into binary multiples that decoder. This decoder is a combination of two 2-bit BA

are turned on or off directly with the input bits. This eliminates decoders.Fig.3. shows the layout of 2-bit Binary to Abacus

the decoder required in unary current DACs. decoder.

Segmented arrays consist of different sub-arrays, or

segments, each with a potentially different array coding. The

MSB-segment is a unary array with 2M-1 element and

represents the upper M bits. The LSB-segment realizes the

lower L bits in a binary array.

Figure1: 2-Bit BA Decoder

Page | 402 www.ijsart.com

IJSART - Volume 2 Issue 10 –OCTOBER 2016 ISSN [ONLINE]: 2395-1052

In the Figure 4: P1 controls the value of current by

varying width of P1. The goal of MOSFETs Sand S¯ they act

like switches. The gate terminal of Sis connected to binary

input. MOS Sturns on the switch and S¯ turns off the switch for

a given input. The current sources that are turned on generate

current flows through the output resistor Rout to generate an

analog output from the DAC. MOSFET P3 is used to increase

the output impedance. The high output impedance can improve

the performance of INL and SFDR. The schematic of current

sourceis shown in Figure 5.

Figure2: 4-Bit BA Decoder

Figure 5:Schematic of Current Source

Figure3: Layout of 2-Bit BA Decoder

2.2 CURRENT SOURCE

The current source used here is driven by the binary

input. To act as a current source the gate voltage must be

constant. The current source performance is improved by

improving two parameters i) small signal output resistance by

increasing resistance a more constant current over a large range

of Vout values. ii) Reduce the Vmin voltage by allowing a large

range of Vout over which current source work properly. To

reduce Vmin by increasing value of W/L and adjusting the gate

to source voltage to get the same output current.

Figure 6: Layout of Current Source

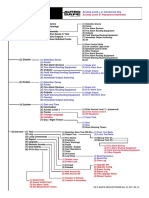

III. PROPOSED 10-BIT DAC

This circuit includes both BA (binary to Abacus)

modules called BA decoder and current source modules (which

Figure4: Schematic diagram of current source includes both current mirror and switch circuit).The general 10-

bit DAC module contains three BA decoders, as shown in

Page | 403 www.ijsart.com

IJSART - Volume 2 Issue 10 –OCTOBER 2016 ISSN [ONLINE]: 2395-1052

Fig.7.The first BA decoder transfers A0–A3 to thermometric

code, which controls the on/off of I0 and 4I0 current source.

The second BA decoders transfer A4–A7 to thermometric

codes, which controls the on/off of 16I0 and 64I0 current

source. And the third BA decoders transfer A8–A9 to

thermometric codes, which controls the on/off of 256I0 current

sources, respectively.

Figure9: Layout of 10-bit Binary Weighted DAC

3.2 SEGMENTED 10-BIT DAC

Figure7: 10-bit current-steering DAC Architecture Figure10: Shows the Segmented DAC. In this DAC

three BA decoders and seven current sources are used as it is a

Each bit of thermometric code controls a current 4-LSB 6-MSB segmented DAC. Figure11: Shows the layout of

source in the current source module. All the current source cells segmented DAC.

are divided into five different unit groups, i.e. I0, 4I0, 16I0,

64I0and 256I0. Each group contains three cells. Therefore, the

above two modules constitute an10-bit DAC. The analog signal

is converted by current flowing directly through the output

resistor. It can generate a voltage varying from 0 to 1023 units,

which of equally spaced level output voltage. Fig. 7 shows the

general construction of a 10-bit current-steering DAC.

3.1 BINARY 10-BIT DAC

Figure8: Shows the Binary Weighted Current Steering

DAC. This DAC uses 10 current sources each current source

has its own weights according to the position where it is used.

Figure9: Shows the Layout of Binary Weighted DAC.

Figure10: 10-bit current-steering DAC Architecture

Figure8: 10-bit Binary Weighted DAC Architecture Figure11: Layout of 10-bit current-steering DAC

Page | 404 www.ijsart.com

IJSART - Volume 2 Issue 10 –OCTOBER 2016 ISSN [ONLINE]: 2395-1052

IV. SIMULATION RESULTS currents and all these currents are added finally to get the output

current. Differential nonlinearity is the difference of the output

Figure12: Shows the simulation result of 10-Bit level between two adjacent codes. Integral nonlinearity is the

Segmented DAC. measure of the actual output voltage level minus the ideal level.

The values of DNL and INL after simulation are ± 0.04 and ±

0.05. The SFDR calculated is 88.156 dB.The loading effect may

degrade the performance of the DAC as it adds parasitic

capacitance in the circuit.

Table 1: Comparison of Experimental Results

Parameters Ref [1] Ref [2] Ref [3] This

Work

Resolution 10 10 10 10

Sample Rate 200 210 80 200

(MHz)

DNL 0.16 0.7 0.55 0.06

INL 0.13 1.1 0.4 0.040

Supply Voltage 3.3 3.3 2.5 3.3

(V)

Power 7.9 83 27.65 23.015

Dissipation(mw)

SFDR (dB) 77.9 59.36 68.15 88.156

Area (mm2) 0.0378 5 0.185 0.0190

Technology 350 350 250 130

(nm)

Figure12: Shows the simulation result of 10-Bit Segmented DAC

VI. CONCLUSION

In this paper, a 10-bit current-steering segmented

(4LSB-6MSB) DAC was proposed. The technology is TSMC

130 nm CMOS process. The power consumption was about

23.015 mW at the sample rate of 200 MHz. The supply voltage

was 3.3 V. It achieved a DNL and INL of 0.06 LSB and 0.04

LSB, respectively. The SFDR of simulation was about 88.15

dB. This work presented a good performance when compared

with researches in DNL, INL, SFDR and area. This design is

suitable for low-power electrical productions.

ACKNOWLEDGMENT

We the authors would like to take this opportunity to

extend our thanks to Department of ECE, MVGR College of

Engineering, Vizianagaram for providing required tools to do

Figure13: Shows the Result of Some Input Bits research in VLSI Domain.

Figure12: Shows the simulation result of 10-Bit REFERENCES

Segmented DAC, in which the result of a given input

0010000000is 127.021 mV. The segmented DAC consists of [1] Yi S-C. A 10-bit CMOS current-steering digital to analog

current source modules of different weights. The digital input converter. AEU – Int J Electron Commun 2012;66:433–7.

bits In1, In2, In3, In4 drives the first four current sources of [2] Cho H-H, Park C-Y, Yune G-S, Yoon K-S. A 10-bit 210

having weights 1, 2, 4 and 8 gives a current of I1, I2, I3, I4 MHz CMOS D/A converter for WLAN. In: IEEE Asia-

andI7respectively.All these current sources produce different

Page | 405 www.ijsart.com

IJSART - Volume 2 Issue 10 –OCTOBER 2016 ISSN [ONLINE]: 2395-1052

Pacific conference on advanced system integrated circuits.

August 2004. p. 106–9.

[3] Halder S, Banerjee S, Ghosh A, Prasad R, Chatterjee A,

Dey SK. A 10-bit 80-MSPS 2.5-V 27.65-mW 0.185-mm2

segmented current steering CMOS DAC’. In: 18th

international conference on VLSI design. January 2005. p.

319–22.

[4] Ashok Kumar Adepu and Kiran Kumar Kolupuri. “A 130-

nm CMOS 400 MHz 8-bit Low Power Binary Weighted

Current Steering DAC”. International Journal on

Cybernetics & Informatics (IJCI) Vol. 5, No. 4, August

2016.

[5] Yi S-C. An 8-bit current-steering digital to analog

converter. AEU – Int J Electron Commun 2012;66:433–7.

[6] B. Razavi, Principles of Data Conversion System Design.

New York IEEE Press, 1995.

[7] Huei-Chi Wang, Hong-Sing Kao, and Tai-Cheng Lee. An

%bit 2-V 2-mW 0.25-mm2 CMOS DAC in 2004 IEEE

Asia-Pacific Conference on Advanced System Integrated

Circuits(AP-ASIC2004).

[8] Hong GM, Hsu S-H, Peng Y-H, Chen AH-H, Wang Y-T,

Lu H-H.” A 10-bit 300 MHz 0.1 mm2 triple-channel

current-steering DAC 75.98 dB SFDR in 65 nm”. In: VLSI

DAT 2008, IEEE international symposium on VLSI

design, automation and test. April 2008

Page | 406 www.ijsart.com

You might also like

- Current Steering DacDocument6 pagesCurrent Steering Dacfahmi rasiqNo ratings yet

- A 12bit 250MSPS Pipeline ADC With 4 Gbps Serial Output InterfaceDocument11 pagesA 12bit 250MSPS Pipeline ADC With 4 Gbps Serial Output InterfaceKasi BandlaNo ratings yet

- ADC08060 8-Bit, 20 MSPS To 60 MSPS, 1.3 MW/MSPS A/D ConverterDocument19 pagesADC08060 8-Bit, 20 MSPS To 60 MSPS, 1.3 MW/MSPS A/D ConverterJuan CarlosNo ratings yet

- Analog To Digital (ADC) and Digital To Analog (DAC) ConvertersDocument12 pagesAnalog To Digital (ADC) and Digital To Analog (DAC) ConvertersIoana IoanaNo ratings yet

- Dac PDFDocument7 pagesDac PDFsanthoshNo ratings yet

- A 8-Bit Hybrid Architecture Current-Steering DAC: International Research Journal of Engineering and Technology (IRJET)Document5 pagesA 8-Bit Hybrid Architecture Current-Steering DAC: International Research Journal of Engineering and Technology (IRJET)upendra450No ratings yet

- Design of Low Power 6-Bit Digitally-Controlled Oscillator (DCO)Document9 pagesDesign of Low Power 6-Bit Digitally-Controlled Oscillator (DCO)AtulNo ratings yet

- Week 3Document25 pagesWeek 3İBRAHİM YÜMLÜNo ratings yet

- Analog Devices - MT-016Document6 pagesAnalog Devices - MT-016ModyKing99No ratings yet

- DLC Lab - 10Document7 pagesDLC Lab - 10Didarul Alam AlifNo ratings yet

- Design and Simulation of DAC On The Basis of Capacitor ArrayDocument4 pagesDesign and Simulation of DAC On The Basis of Capacitor ArrayAmitNo ratings yet

- Lab Manual DAC-SignedDocument10 pagesLab Manual DAC-Signedabidrk_21789100% (2)

- PmodCMPS Manual HMC5883Document2 pagesPmodCMPS Manual HMC5883soros4No ratings yet

- Camera Ready Reconfigurable ADCDocument20 pagesCamera Ready Reconfigurable ADCjayamala adsulNo ratings yet

- A Good Dac DesignDocument11 pagesA Good Dac DesignBhavin DesaiNo ratings yet

- DACDocument28 pagesDACRohith Mohan100% (1)

- Digital-to-Analog Conversion: Microchip MCP4921 Features General Overview Serial SPI InterfaceDocument8 pagesDigital-to-Analog Conversion: Microchip MCP4921 Features General Overview Serial SPI InterfaceRi Cha RdNo ratings yet

- Ad 768Document20 pagesAd 768Tim Lai Ky UcNo ratings yet

- Experinment 10Document5 pagesExperinment 10mano17doremonNo ratings yet

- Design of 16 Bit 180nm CMOS Fully Segmented DACDocument3 pagesDesign of 16 Bit 180nm CMOS Fully Segmented DACInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Folding ADCs ADIDocument12 pagesFolding ADCs ADINishit Shah100% (1)

- integratedelectronicsUNIT 3convertersDocument11 pagesintegratedelectronicsUNIT 3convertersYogeshwaranNo ratings yet

- Ultrasmall Digital Image Sensor For Endoscopic ApplicationsDocument4 pagesUltrasmall Digital Image Sensor For Endoscopic ApplicationsTaha OpedNo ratings yet

- Adc and Dac Converters: BY:-PULKIT PARASHAR (17BEE080), Pritam Yaduvanshi (17bee079) Guide:-Prof. Akhilesh NimjeDocument9 pagesAdc and Dac Converters: BY:-PULKIT PARASHAR (17BEE080), Pritam Yaduvanshi (17bee079) Guide:-Prof. Akhilesh NimjePritam YaduvanshiNo ratings yet

- Hui PanDocument12 pagesHui PanSanjayan VinayagamoorthyNo ratings yet

- Reynolds03 JSSC Vol38no9 Pp1555-1560 ADirectConvReceiverICforWCDMAMobileSystemsDocument6 pagesReynolds03 JSSC Vol38no9 Pp1555-1560 ADirectConvReceiverICforWCDMAMobileSystemsTom BlattnerNo ratings yet

- Design of A Low-Power 10-Bit DAC in 130 NM CMOS Technology: Mamun Bin Ibne Reaz Md. Torikul Islam BadalDocument5 pagesDesign of A Low-Power 10-Bit DAC in 130 NM CMOS Technology: Mamun Bin Ibne Reaz Md. Torikul Islam BadalSunil KumarNo ratings yet

- Bginzz Vlsi2006 PaperDocument2 pagesBginzz Vlsi2006 PaperPavan Kumar K.v.No ratings yet

- A 1 V 6-Bit 2.4 GS/s Nyquist CMOS DAC For UWB Systems: OtiidDocument4 pagesA 1 V 6-Bit 2.4 GS/s Nyquist CMOS DAC For UWB Systems: Otiidissam_techNo ratings yet

- ,dynamic Element Matching For High-Accuracy Monolithic WA ConvertersDocument6 pages,dynamic Element Matching For High-Accuracy Monolithic WA ConvertersMEHDI ABDOUNo ratings yet

- 2.704Gsps: A 6-Bit DAC For Ds-Cdma UwbDocument4 pages2.704Gsps: A 6-Bit DAC For Ds-Cdma Uwbissam_techNo ratings yet

- 40104diDocument6 pages40104dimariastalinNo ratings yet

- Experiment No. 4 ADC PDFDocument16 pagesExperiment No. 4 ADC PDFRia Cordova0% (1)

- Mpc1 Multi Purpose Can Controller - Reference Manual: Baldur Gíslason December 17, 2018Document6 pagesMpc1 Multi Purpose Can Controller - Reference Manual: Baldur Gíslason December 17, 2018Andrzej GomulaNo ratings yet

- Digital To Analog ConverterDocument7 pagesDigital To Analog ConverterDeepakNathNo ratings yet

- Adc-DacDocument21 pagesAdc-DacSon SonNo ratings yet

- Unit 4 NotesDocument26 pagesUnit 4 NotesJohnsi JNo ratings yet

- Digital System Design I DACDocument9 pagesDigital System Design I DACعبد الحكم زهيرNo ratings yet

- Folding ADC TutorialDocument5 pagesFolding ADC TutorialAlexandre KennedyNo ratings yet

- DEC LAB 06 (Design of A Digital To Analog Converter)Document9 pagesDEC LAB 06 (Design of A Digital To Analog Converter)anon_776365175No ratings yet

- Opamp Vlsi Project Adc 10 BitDocument4 pagesOpamp Vlsi Project Adc 10 BitPrajwal PrabhuNo ratings yet

- Best Practices For Analog PCB Layout Using RA2A1 MCU: Application Note Renesas RA FamilyDocument12 pagesBest Practices For Analog PCB Layout Using RA2A1 MCU: Application Note Renesas RA FamilymNo ratings yet

- Dac Interface To 8051 PDFDocument4 pagesDac Interface To 8051 PDFRAVI100% (1)

- REPORTFINALDocument21 pagesREPORTFINALReal HumanityNo ratings yet

- Design of DAC Using Pass Transistors - REPORTDocument14 pagesDesign of DAC Using Pass Transistors - REPORTRaj MistryNo ratings yet

- A Novel and Systematic Implementation of Thermometer-Coded Current-Mode DACDocument4 pagesA Novel and Systematic Implementation of Thermometer-Coded Current-Mode DACRodrigo SantosNo ratings yet

- Differential Analog Data Path DC Offset Calibration MethodsDocument7 pagesDifferential Analog Data Path DC Offset Calibration MethodsLincoln RibeiroNo ratings yet

- Kelvin DividerDocument2 pagesKelvin DividerlonemubashirNo ratings yet

- DLC LAB - 10 - Student - ManualDocument8 pagesDLC LAB - 10 - Student - ManualImtiaj SajinNo ratings yet

- EDN Design Ideas 2006Document142 pagesEDN Design Ideas 2006chag1956100% (1)

- Monolithic 16-Bit Dacport AD669: 61 LSB Integral Linearity ErrorDocument13 pagesMonolithic 16-Bit Dacport AD669: 61 LSB Integral Linearity ErrormhasansharifiNo ratings yet

- Precision Digital-to-Analog Converters: SEA DFAE Training Dec 2004Document38 pagesPrecision Digital-to-Analog Converters: SEA DFAE Training Dec 2004wildmonkey88No ratings yet

- Digital To Analog ConvertorsDocument10 pagesDigital To Analog ConvertorsAşšAśsins BRošNo ratings yet

- Using DE0-Nano ADC-1Document17 pagesUsing DE0-Nano ADC-1Sylwester MNo ratings yet

- Applying The New CMOS Micro-Dac: National Semiconductor Application Note 271 Tim Regan September 1981Document12 pagesApplying The New CMOS Micro-Dac: National Semiconductor Application Note 271 Tim Regan September 1981Beroxi MihaiNo ratings yet

- AV02-2211EN AN - 5442 MGA-17516 07apr2011,0 PDFDocument24 pagesAV02-2211EN AN - 5442 MGA-17516 07apr2011,0 PDFAnh Bien NguyenNo ratings yet

- Implementation of 4-Bit R-2R DAC On CADENCE ToolsDocument5 pagesImplementation of 4-Bit R-2R DAC On CADENCE Toolsabhishek0% (1)

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsFrom EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNo ratings yet

- Cloud Engineer Data Interview Prep GuideDocument7 pagesCloud Engineer Data Interview Prep GuideRakshithNo ratings yet

- DataSheet Book - September 07Document276 pagesDataSheet Book - September 07Ian JaredNo ratings yet

- Dell Openmanage Enterprise v32 - White Papers2 - en UsDocument24 pagesDell Openmanage Enterprise v32 - White Papers2 - en UsTechnicianccnaNo ratings yet

- Grid ArchitectureDocument19 pagesGrid ArchitectureBittu VermaNo ratings yet

- Laravel Tips and Tricks LightDocument423 pagesLaravel Tips and Tricks LightGyi Gyi100% (1)

- Polycom Realpresence Web Suite GuideDocument48 pagesPolycom Realpresence Web Suite GuideAnonymous k2SY4zdI3No ratings yet

- ICT-LAB Activity Sheet TemplateDocument4 pagesICT-LAB Activity Sheet Templatedebz marianoNo ratings yet

- New Microsoft Word DocumentDocument3 pagesNew Microsoft Word Documentengineer mrewaNo ratings yet

- Software Testing StrategiesDocument25 pagesSoftware Testing Strategieshabado badoNo ratings yet

- Empowerment Technology - Lesson 1Document7 pagesEmpowerment Technology - Lesson 1Julie Ann CotaraNo ratings yet

- FortiGate Interview Questions OnlyDocument4 pagesFortiGate Interview Questions OnlyWady L. BautistaNo ratings yet

- ARDUINODocument13 pagesARDUINOGagleen RissamNo ratings yet

- 2SGBD Practice 1Document2 pages2SGBD Practice 1Matisse prtNo ratings yet

- DVDFab 11 User ManualDocument70 pagesDVDFab 11 User ManualLuiz Antonio Bevilaqua CavalcanteNo ratings yet

- Auronica Fire Detection Operation ManualDocument1 pageAuronica Fire Detection Operation ManualSaint JossNo ratings yet

- Application Development and Emerging Technology All inDocument21 pagesApplication Development and Emerging Technology All inInah ValdezNo ratings yet

- IEEE PaperDocument6 pagesIEEE Paper198W1A05D7-SEC-C CHANDRAPATLA DEDEEPYANo ratings yet

- Tracing/Logging: IBM Content Collector For SAP Applications V2.2Document6 pagesTracing/Logging: IBM Content Collector For SAP Applications V2.2engko17No ratings yet

- Op-Amp MCQDocument13 pagesOp-Amp MCQAbhisek Gautam BTNo ratings yet

- Analog ElectronicsDocument180 pagesAnalog ElectronicsTharun kumar DoggaNo ratings yet

- Short Essay On PythonDocument1 pageShort Essay On PythonSamuel ChNo ratings yet

- LogfileDocument7 pagesLogfileJacob TibonNo ratings yet

- Implementas API Bot Telegram Untuk Sistem Notifikasi Pada The Dude Network Monitoring SystemDocument7 pagesImplementas API Bot Telegram Untuk Sistem Notifikasi Pada The Dude Network Monitoring SystemDellya Sari AndiniNo ratings yet

- Logcat 1672033245882Document6 pagesLogcat 1672033245882PyaeSone WinNo ratings yet

- IEC62304 ChecklistDocument6 pagesIEC62304 ChecklistuclealsepNo ratings yet

- ARM Architecture Reference ManualDocument1,138 pagesARM Architecture Reference ManualDaniel KingNo ratings yet

- Uchebnik Chast Vtoraya SBDocument203 pagesUchebnik Chast Vtoraya SBDaniela TigerNo ratings yet

- Sanjay Mali: Citizenship: Indian Date of Birth: 30 May 1991Document4 pagesSanjay Mali: Citizenship: Indian Date of Birth: 30 May 1991Sandesh AhirNo ratings yet

- Swinburne VPN Installation Guide Personal DevicesDocument7 pagesSwinburne VPN Installation Guide Personal DevicesJustin NguyenNo ratings yet

- Lecture Week 4: Algorithm ComplexityDocument34 pagesLecture Week 4: Algorithm ComplexityMaham uroojNo ratings yet