Professional Documents

Culture Documents

Lec 10 CMOS Static Logic Delays

Uploaded by

Mainak TarafdarOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lec 10 CMOS Static Logic Delays

Uploaded by

Mainak TarafdarCopyright:

Available Formats

VLSI Design : 2021-22

Lecture 10

Delays in

Complex CMOS Static Logic Circuits

By Dr. Sanjay Vidhyadharan

ELECTRICAL ELECTRONICS COMMUNICATION INSTRUMENTATION

Logical Effort

2/19/2022 2

ELECTRICAL ELECTRONICS COMMUNICATION INSTRUMENTATION

Delay in a Logic Gates

C int

C interconnect

2/19/2022 3

ELECTRICAL ELECTRONICS COMMUNICATION INSTRUMENTATION

Delay in a Logic Gates

For an Inverter

f : effective fanout

tp : Intrinsic Delay (Sizing Independent, Process Dependant)

For a Complex gate

f : Electrical effort = Cout / Cin

tp0 : Remains Intrinsic Delay of inverter

2/19/2022 4

ELECTRICAL ELECTRONICS COMMUNICATION INSTRUMENTATION

Parasitic Delay

p represents the ratio of the intrinsic (or unloaded) delays of the

complex gate and the simple inverter.

In multiples of pinv (1)

Estimates of intrinsic delay factors of various logic types assuming simple

layout styles, and a fixed PMOS/NMOS ratio.

2/19/2022 5

ELECTRICAL ELECTRONICS COMMUNICATION INSTRUMENTATION

Delay in a Logic Gates

2/19/2022 6

ELECTRICAL ELECTRONICS COMMUNICATION INSTRUMENTATION

Delay in a Logic Gates

For a Complex gate

h = fg the gate effort

Path effective fanout

Path Logical Effort

Path Effort H = FG

2/19/2022 7

ELECTRICAL ELECTRONICS COMMUNICATION INSTRUMENTATION

Delay in a Logic Gates

Digital Integrated Circuits By Jan M Rabaey

2/19/2022 8

ELECTRICAL ELECTRONICS COMMUNICATION INSTRUMENTATION

Logical Effort

Paths that Branch

G =1 15

90

F = 90 / 5 = 18 5

GF = 18 15

90

f1 = (15 +15) / 5 = 6

f2 = 90 / 15 = 6

F <-> H

H = g1g2f1f2 = 36 = 2GF (B=2)

H = GBF

2/19/2022

ELECTRICAL ELECTRONICS COMMUNICATION INSTRUMENTATION

Logical Effort : Example

• Select gate sizes x and y for least delay from A to B

x

y

x

Critical path

45

A 8

x

y B

45

2/19/2022

ELECTRICAL ELECTRONICS COMMUNICATION INSTRUMENTATION

Logical Effort : Example

x

y

x

45

A 8

x

y B

45

Logical Effort G = (4/3)*(5/3)*(5/3) = 100/27

Electrical Effort F = 45/8

Branching Effort B=3*2=6

Path Effort H = GBF = 125

3

Best Stage Effort ℎ= 𝐻=5

Parasitic Delay P = 2 + 3 + 2 = 7

Delay D = 3*5 + 7 = 22 = 4.4 FO4

In multiples of pinv (1)

2/19/2022

ELECTRICAL ELECTRONICS COMMUNICATION INSTRUMENTATION

Logical Effort : Example

• Delay of a fanout-of-4 (FO4) inverter

d

Logical Effort: G=1

Electrical Effort: F=4

H = FG = 4

h=4

Parasitic Delay: p=1

Stage Delay: d=5

ELECTRICAL ELECTRONICS COMMUNICATION INSTRUMENTATION

Logical Effort : Example

• Work backward for sizes

y = 45 * (5/3) / 5 = 15 h = 5 = fg the gate effort

f = 5/g the gate effort

x = (15*2) * (5/3) / 5 = 10

45

A P: 4

P: 4

N: 4 P: 12 B

N: 6 45

N: 3

ELECTRICAL ELECTRONICS COMMUNICATION INSTRUMENTATION

Thank you

2/19/2022 14

ELECTRICAL ELECTRONICS COMMUNICATION INSTRUMENTATION

You might also like

- Electronic Engineering Applications of Two–Port Networks: Applied Electricity and Electronics DivisionFrom EverandElectronic Engineering Applications of Two–Port Networks: Applied Electricity and Electronics DivisionNo ratings yet

- Lec 11 Layout of Static CMOS CircuitsDocument29 pagesLec 11 Layout of Static CMOS CircuitsMainak TarafdarNo ratings yet

- Lec 9 CMOS Static LogicDocument19 pagesLec 9 CMOS Static LogicMainak TarafdarNo ratings yet

- Tutorial - 13Document15 pagesTutorial - 13YusuppNo ratings yet

- Zebrev Interface Trap Extraction MIEL May 2012Document11 pagesZebrev Interface Trap Extraction MIEL May 2012Alexander TselykovskiyNo ratings yet

- Lec-11 - Arithmetic - Circuits Part-1Document32 pagesLec-11 - Arithmetic - Circuits Part-1vin adNo ratings yet

- Field Effect TransistorsDocument73 pagesField Effect TransistorsDan ChapsNo ratings yet

- Analog Electronics: Tutorial-8Document7 pagesAnalog Electronics: Tutorial-8Tushit ThakkarNo ratings yet

- Experiment3 HAMZADocument14 pagesExperiment3 HAMZAhamzasamara80No ratings yet

- Analog Systems: Microelectronic Circuit DesignDocument39 pagesAnalog Systems: Microelectronic Circuit DesignMạnh Cường TrầnNo ratings yet

- Logical Effort of Paths: A and C Begin To Rise (Figure 4.28 (C) ) - at First, Both Nodes See ApproximatelyDocument1 pageLogical Effort of Paths: A and C Begin To Rise (Figure 4.28 (C) ) - at First, Both Nodes See ApproximatelyCarlos SaavedraNo ratings yet

- Ee2205 2Document2 pagesEe2205 2Naveen BigShotNo ratings yet

- Preliminary Examination: Electronics & Telecom EnggDocument54 pagesPreliminary Examination: Electronics & Telecom EnggMaha Lakshmi ShankarNo ratings yet

- ECEG-4221-VLSI Lec 09 Testing Digital CircuitsDocument22 pagesECEG-4221-VLSI Lec 09 Testing Digital CircuitsNuhamin BirhanuNo ratings yet

- Introduction To Reversible Logic Gates & Its Application: Prashant .R.Yelekar Prof. Sujata S. ChiwandeDocument5 pagesIntroduction To Reversible Logic Gates & Its Application: Prashant .R.Yelekar Prof. Sujata S. ChiwandeVani YamaniNo ratings yet

- Ijater 04 29Document7 pagesIjater 04 29anandvmahadikNo ratings yet

- Designing of Combinational Logic Gates in Cmos: G.Susmitha Roll No:06Document49 pagesDesigning of Combinational Logic Gates in Cmos: G.Susmitha Roll No:06kumarbsnspNo ratings yet

- 16 Logical Effort and Transistor Sizing 31-08-2020 (31 Aug 2020) Material - I - 31 Aug 2020 - Logical - EffortDocument28 pages16 Logical Effort and Transistor Sizing 31-08-2020 (31 Aug 2020) Material - I - 31 Aug 2020 - Logical - EffortParth VijayNo ratings yet

- Embedded System Design: 1. Digital Parallel Input / OutputDocument36 pagesEmbedded System Design: 1. Digital Parallel Input / OutputNguyễn Đức TuấnNo ratings yet

- L11,12 DifferentiatorDocument36 pagesL11,12 Differentiatorbronzeboy737No ratings yet

- Cmpen 411 Vlsidiitlci It Vlsi Digital Circuits Spring 2011 Lecture 12: Logical EffortDocument33 pagesCmpen 411 Vlsidiitlci It Vlsi Digital Circuits Spring 2011 Lecture 12: Logical EffortToby DatorNo ratings yet

- Gogte Institute of Technology: Department of Electronics and CommunicationDocument6 pagesGogte Institute of Technology: Department of Electronics and CommunicationNeha PatilNo ratings yet

- Chap5 Lect15 ComboDocument11 pagesChap5 Lect15 ComboSravya ReddyNo ratings yet

- Lab 3 AnalogDocument10 pagesLab 3 AnalogArtour doto100% (1)

- Lecture 04 - Logic SimulationDocument44 pagesLecture 04 - Logic Simulationmayank pNo ratings yet

- De - Lab ExperimentsDocument62 pagesDe - Lab ExperimentssaipraneethpNo ratings yet

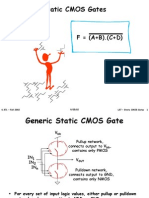

- Static CMOS Gates: F (A+B) - (C+D)Document22 pagesStatic CMOS Gates: F (A+B) - (C+D)Puneet ShrivastavaNo ratings yet

- Assignment 3Document9 pagesAssignment 3Nabil IbrahimNo ratings yet

- STI 2024 DIODES, BJT and MOSFET SMALL VARYING SIGNALSDocument15 pagesSTI 2024 DIODES, BJT and MOSFET SMALL VARYING SIGNALSArthur MoloNo ratings yet

- Blekinge Tekniska Högskolan: Inst. För Telekommunikation Och Signalbehandling Exam TCP/IP Internetworking ETC003Document2 pagesBlekinge Tekniska Högskolan: Inst. För Telekommunikation Och Signalbehandling Exam TCP/IP Internetworking ETC003Rohit KshirsagarNo ratings yet

- Lab 05Document4 pagesLab 05awab ahsanNo ratings yet

- Reversible Logic Gates and Its PerformancesDocument6 pagesReversible Logic Gates and Its Performancesnaysagupta2014No ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument66 pagesDigital Integrated Circuits: A Design Perspectiveapi-127299018No ratings yet

- Minimizing The Delay of C2mos D Flip Flop Using Logical Effort TheoryDocument3 pagesMinimizing The Delay of C2mos D Flip Flop Using Logical Effort TheorySavio SNo ratings yet

- Design and Implementation of Seven Segment Display Using Reversible Logic GatesDocument7 pagesDesign and Implementation of Seven Segment Display Using Reversible Logic GatesIJRASETPublicationsNo ratings yet

- DE ManualDocument92 pagesDE ManualGopinathan MNo ratings yet

- ECE551 - Homework 3 Solution - Spring 2019Document9 pagesECE551 - Homework 3 Solution - Spring 2019JAY CHHEDANo ratings yet

- DE - KOE 039 - Assignment #5Document1 pageDE - KOE 039 - Assignment #5dhdw kwhdhwNo ratings yet

- Chapter7 1Document2 pagesChapter7 1Chathuranga Swarna KumaraNo ratings yet

- Babazadeh Haghparast 1355 1361 PDFDocument8 pagesBabazadeh Haghparast 1355 1361 PDFkamarajme2006No ratings yet

- Review Lecture 1-14Document133 pagesReview Lecture 1-14vin adNo ratings yet

- Magic Tee As An IsolatorDocument7 pagesMagic Tee As An IsolatorkrNo ratings yet

- TSEK36 Labmanual 2009 SE v1Document47 pagesTSEK36 Labmanual 2009 SE v1Syamak KashfolayatNo ratings yet

- Expt No. 2 (B) Common Base AmplifierDocument11 pagesExpt No. 2 (B) Common Base Amplifierrani kumarNo ratings yet

- Delay Optimization & Logical EffortsDocument38 pagesDelay Optimization & Logical EffortsiknowiamanidiotNo ratings yet

- Design and Implementation of Combinational Circuits Using Reversible Logic On FPGA SPARTAN 3EDocument6 pagesDesign and Implementation of Combinational Circuits Using Reversible Logic On FPGA SPARTAN 3Evarsha muthyalaNo ratings yet

- en Signalwandler SVE4Document2 pagesen Signalwandler SVE4hamidouhouNo ratings yet

- 1-Digital Assignment Questions - Sem 2 2021 - 2022Document5 pages1-Digital Assignment Questions - Sem 2 2021 - 2022AtamFixItNo ratings yet

- Novel Rev Gate N ApplinsDocument6 pagesNovel Rev Gate N ApplinshdswethaNo ratings yet

- Lecture 14a CA II (En 214)Document7 pagesLecture 14a CA II (En 214)incognito.h125No ratings yet

- Ijest11-03-03-207 PDFDocument9 pagesIjest11-03-03-207 PDFKrishnaveni DhulipalaNo ratings yet

- Overview Data Sheets: F 3223: 4 Fold Input ModuleDocument4 pagesOverview Data Sheets: F 3223: 4 Fold Input ModulemohamadziNo ratings yet

- Ijramt 3 2 8Document4 pagesIjramt 3 2 8Mani shankarNo ratings yet

- PorteDocument34 pagesPortePeacson AdamadouNo ratings yet

- Non-Conventional Low Power Circuit Design TechniquesDocument9 pagesNon-Conventional Low Power Circuit Design Techniquesijire publicationNo ratings yet

- Basic Reversible Logic Gates and It's Qca Implementation: July 2014Document6 pagesBasic Reversible Logic Gates and It's Qca Implementation: July 2014GirijaNo ratings yet

- Week 6Document56 pagesWeek 6PATEL RUTVIKNo ratings yet

- Delay Estimation in Static Design: by Prasad PandeDocument33 pagesDelay Estimation in Static Design: by Prasad PandeRavi RajanNo ratings yet

- Experiment No: 4: TITLE: 4-Bit Comparator AIM: To Design 4-Bit Comparator Using IC 7485 Prior ConceptDocument43 pagesExperiment No: 4: TITLE: 4-Bit Comparator AIM: To Design 4-Bit Comparator Using IC 7485 Prior ConceptKelvin CooperNo ratings yet

- Upc2709t NecDocument16 pagesUpc2709t Necfarid.hamraniNo ratings yet

- Lec 4 CMOS Technology ICFabricationDocument46 pagesLec 4 CMOS Technology ICFabricationMainak TarafdarNo ratings yet

- Lec 6 CMOS Inverter Static CharacteristicsDocument36 pagesLec 6 CMOS Inverter Static CharacteristicsMainak TarafdarNo ratings yet

- Lec 7 MOS-CapacitanceDocument13 pagesLec 7 MOS-CapacitanceMainak TarafdarNo ratings yet

- Lec 5 CMOS Technology ScalingDocument11 pagesLec 5 CMOS Technology ScalingMainak TarafdarNo ratings yet

- Lec 3 Deep Submicron MOSFET OperationDocument14 pagesLec 3 Deep Submicron MOSFET OperationMainak TarafdarNo ratings yet

- Lect1 2 1642214538630Document17 pagesLect1 2 1642214538630Mainak TarafdarNo ratings yet

- I STHARADocument25 pagesI STHARAMainak TarafdarNo ratings yet

- Steps To Developing A Project ScheduleDocument3 pagesSteps To Developing A Project ScheduleUjjal RegmiNo ratings yet

- IntelDocument5 pagesIntelRini RafiNo ratings yet

- SG300-10SFP Datasheet: Quick SpecDocument3 pagesSG300-10SFP Datasheet: Quick SpecChuks ValentineNo ratings yet

- E53.17.x, E53.15.x, and E50.13.x Summary of Firmware ChangesDocument8 pagesE53.17.x, E53.15.x, and E50.13.x Summary of Firmware ChangesDaniel MirandaNo ratings yet

- Computer Basics: How Do I Connect To The Internet?Document8 pagesComputer Basics: How Do I Connect To The Internet?Ser Crz JyNo ratings yet

- PythonDocument65 pagesPythonvishal dasNo ratings yet

- AIO - Radio Station PlayerDocument2 pagesAIO - Radio Station PlayerOdysseas RapantasNo ratings yet

- Product - Guide - Bizhub 164 - vs1.0Document20 pagesProduct - Guide - Bizhub 164 - vs1.0vladimir2426No ratings yet

- Lesson Plan: Subject: Computer Class: Iv Term: Ii Term Topic/Module:Personalizing Windows 7 No. of Classes: 4Document5 pagesLesson Plan: Subject: Computer Class: Iv Term: Ii Term Topic/Module:Personalizing Windows 7 No. of Classes: 4Komal VaswaniNo ratings yet

- Sqlfordevscom Next Level Database Techniques For Developers Pages 11 17Document7 pagesSqlfordevscom Next Level Database Techniques For Developers Pages 11 17Kumar SIVANo ratings yet

- Seagate Diagnostic CommandDocument45 pagesSeagate Diagnostic CommandCepii Mojico100% (1)

- BSB50420 Diploma of Leadership and Management BSBPMG430 Undertake Project Work A1 - Knowledge QuestionsDocument6 pagesBSB50420 Diploma of Leadership and Management BSBPMG430 Undertake Project Work A1 - Knowledge QuestionsKushalNo ratings yet

- ABES Institute of TechnologyDocument10 pagesABES Institute of TechnologyViral TrendNo ratings yet

- 6AV66440AA012AX0 Datasheet enDocument6 pages6AV66440AA012AX0 Datasheet enJoseph MagonduNo ratings yet

- AM1H-M Am1B-Mdh AM1B-M: User ManualDocument68 pagesAM1H-M Am1B-Mdh AM1B-M: User ManualMilagros Carolina GarciaNo ratings yet

- CS552 Object-Oriented Design Project Mahender Kasarla, Pramod Reddy Dharma Rivier UniversityDocument37 pagesCS552 Object-Oriented Design Project Mahender Kasarla, Pramod Reddy Dharma Rivier UniversitySanjog PathakNo ratings yet

- UntitledDocument166 pagesUntitledarifNo ratings yet

- FS Online FullStack SyllabusDocument16 pagesFS Online FullStack SyllabusShreyas WaghmareNo ratings yet

- AFF A800 Systems Installation and SetupDocument2 pagesAFF A800 Systems Installation and Setupserkan887_790218525No ratings yet

- InRoads SDE GuidelinesDocument115 pagesInRoads SDE GuidelineshkbadboyNo ratings yet

- MadhusudhanR ResumeDocument11 pagesMadhusudhanR ResumesriNo ratings yet

- Chapter-1 - Analysing Business Goals and ContraintsDocument65 pagesChapter-1 - Analysing Business Goals and ContraintsJustify Ester PasaribuNo ratings yet

- S7plcsim Advanced Readme en-US en-US PDFDocument5 pagesS7plcsim Advanced Readme en-US en-US PDFDalethSepúlvedaNo ratings yet

- Hawassa University Institute of Technologyfaculty of Informaticsdepartment of Computer Scienceintroduction To Emerging Technology-Assignment IDocument7 pagesHawassa University Institute of Technologyfaculty of Informaticsdepartment of Computer Scienceintroduction To Emerging Technology-Assignment IDuresa GemechuNo ratings yet

- DNC - User Manual For Overseas VerificationDocument20 pagesDNC - User Manual For Overseas VerificationPrep Eve IELTSNo ratings yet

- Amazon - in - Order 403-8423612-4851555Document1 pageAmazon - in - Order 403-8423612-4851555Madhumitha LNo ratings yet

- Zerto Virtual Replication Operability MatrixDocument10 pagesZerto Virtual Replication Operability MatrixSuman RagiNo ratings yet

- Ef Apluscore sg060Document60 pagesEf Apluscore sg060Danno NNo ratings yet

- Java Network ProjectDocument20 pagesJava Network ProjectabbasmulaniNo ratings yet

- Complex Engineering Problem (Project Explanation)Document6 pagesComplex Engineering Problem (Project Explanation)Ahmed KhanNo ratings yet