Professional Documents

Culture Documents

Lecture Microprocessor 7 - 8

Uploaded by

John wick0 ratings0% found this document useful (0 votes)

12 views30 pagesOriginal Title

Lecture Microprocessor 7_8

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

12 views30 pagesLecture Microprocessor 7 - 8

Uploaded by

John wickCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 30

Microprocessor Systems

Lecture 7-8 Bus Structure

Engr. Rehan Azmat

Lecture 7-8

Recap

Cortex-M Processor Architecture, Registers, Execution of

Program in Cortex-M Processor, Address Space

Topics

Bus Introduction

Elements of Bus design

◦ Type

◦ Methods of Arbitration

◦ Timing

◦ Width

◦ Data Transfer Types

Engr. Rehan Azmat

Buses

There are a number of possible

interconnection systems

Single and multiple BUS structures

are most common

e.g. Control/Address/Data bus (PC)

e.g. Unibus (DEC-PDP)

What is a Bus?

A communication pathway connecting

two or more devices

Usually broadcast

Often grouped

◦ A number of channels in one bus

◦ e.g. 32 bit data bus is 32 separate single

bit channels

Power lines may not be shown

Data Bus

Carries data

◦ Remember that there is no difference

between “data” and “instruction” at this

level

Width is a key determinant of

performance

◦ 8, 16, 32, 64 bit

Address bus

Identify the source or destination of

data

e.g. CPU needs to read an instruction

(data) from a given location in memory

Bus width determines maximum

memory capacity of system

◦ e.g. Cortex M4 has 32 bit address bus

giving 4G address space

Control Bus

Control and timing information

◦ Memory read/write signal

◦ Interrupt request

◦ Clock signals

Bus Interconnection Scheme

Big and Yellow?

What do buses look like?

◦ Parallel lines on circuit boards

◦ Ribbon cables

◦ Strip connectors on mother boards

e.g. PCI

◦ Sets of wires

Physical Realization of Bus

Architecture

Single Bus Problems

Lots of devices on one bus leads to:

◦ Propagation delays

Long data paths mean that co-ordination of bus

use can adversely affect performance

If aggregate data transfer approaches bus

capacity

Most systems use multiple buses to

overcome these problems

Traditional (ISA)

(with cache)

High Performance Bus

Elements of Bus Design

Engr. Rehan Azmat

Bus Types

Dedicated

◦ Separate data & address lines

Multiplexed

◦ Shared lines

◦ Address valid or data valid control line

◦ Advantage - fewer lines

◦ Disadvantages

More complex control

Ultimate performance

Bus Arbitration

More than one module controlling the

bus

e.g. CPU and DMA controller

Only one module may control bus at

one time

Arbitration may be centralised or

distributed

Centralised or Distributed

Arbitration

Centralised

◦ Single hardware device controlling bus

access

Bus Controller

Arbiter

◦ May be part of CPU or separate

Distributed

◦ Each module may claim the bus

◦ Control logic on all modules

Timing

Co-ordination of events on bus

Synchronous

◦ Events determined by clock signals

◦ Control Bus includes clock line

◦ A single 1-0 is a bus cycle

◦ All devices can read clock line

◦ Usually sync on leading edge

◦ Usually a single cycle for an event

Synchronous Timing Diagram

Asynchronous Timing – Read

Diagram

Elements of Bus Design

Engr. Rehan Azmat

Bus Width

Address

◦ Impact on System Capacity

Data

◦ Impact on System Performance

Engr. Rehan Azmat

Data Transfer

Read

Write

Read-Modified-Write

Read-After-Write

Block

Engr. Rehan Azmat

Data Transfer

Engr. Rehan Azmat

Cortex M4 Processor

Engr. Rehan Azmat

Bus Interface

Three Advanced High-performance Bus-Lite (AHB-

Lite) interfaces:

◦ ICode Bus Interface

◦ Dcode Bus Interface

◦ System Bus Interfaces.

One Private Peripheral Bus (PPB) based on

Advanced Peripheral Bus (APB) interface.

◦ Bit-band support that includes atomic bit-band write and read

operations.

Engr. Rehan Azmat

Cortex M4

Engr. Rehan Azmat

Cortex M4 Bus Architecture

The processor provides three primary bus

interfaces implementing a variant of the

AMBA 3 AHB-Lite protocol. The processor

implements an interface for CoreSight and

other debug components using the AMBA 3

APB protocol.

Engr. Rehan Azmat

Multiple Bus Interfaces

Engr. Rehan Azmat

Memory Regions

Engr. Rehan Azmat

You might also like

- Interfacing Processors and Peripherals: CS151B/EE M116C Computer Systems ArchitectureDocument31 pagesInterfacing Processors and Peripherals: CS151B/EE M116C Computer Systems ArchitecturetinhtrilacNo ratings yet

- Bus architecture and components overviewDocument186 pagesBus architecture and components overviewSabrina JohnsonNo ratings yet

- Embedded Computing Platform DesignDocument44 pagesEmbedded Computing Platform DesignSatish KumarNo ratings yet

- Lecture#4 - Top Level View of Computer Function and InterconnectionDocument67 pagesLecture#4 - Top Level View of Computer Function and InterconnectionmuusdsdNo ratings yet

- ARM Cortex Processors: A Guide to Cortex-M3 ArchitectureDocument49 pagesARM Cortex Processors: A Guide to Cortex-M3 ArchitectureJyothi B.R.No ratings yet

- Microprocessor & Computer Architecture (Μpca) : Unit 4: Usb, Pci, Scsi,Amba And Asb Bus ArchitectureDocument12 pagesMicroprocessor & Computer Architecture (Μpca) : Unit 4: Usb, Pci, Scsi,Amba And Asb Bus ArchitecturePranathi PraveenNo ratings yet

- Computer Interconnection and Bus StructuresDocument37 pagesComputer Interconnection and Bus StructuresUs ManNo ratings yet

- Computer Organization & Architecture Lecture #15 A View of Computer Function and Interconnection Interconnections StructuresDocument12 pagesComputer Organization & Architecture Lecture #15 A View of Computer Function and Interconnection Interconnections Structuresavdheshg_1No ratings yet

- 04 BusDocument23 pages04 BusAnonymous uUFY09No ratings yet

- Unit - III - Interfacing: Anusha.K Ap, SiteDocument26 pagesUnit - III - Interfacing: Anusha.K Ap, SiterajgantNo ratings yet

- Bus InterconnectionDocument31 pagesBus InterconnectionAnonymous A72zb61100% (1)

- Group 29Document5 pagesGroup 29emanueldakho3No ratings yet

- 9 Bus ArchitectureDocument52 pages9 Bus Architecturesunny567No ratings yet

- Computer Organization and ArchitectureDocument31 pagesComputer Organization and Architecture-AkhilGannamrajuNo ratings yet

- Io BusesDocument56 pagesIo Buseslalokew375No ratings yet

- Bus Architecture ExplainedDocument14 pagesBus Architecture ExplainedAyushi SinghNo ratings yet

- CPU Architecture: Control Unit (CU)Document10 pagesCPU Architecture: Control Unit (CU)i study100% (1)

- Paper - History of Different Buses in A PCDocument20 pagesPaper - History of Different Buses in A PCammad ahmadNo ratings yet

- Computer Buses: What Is A Bus?Document14 pagesComputer Buses: What Is A Bus?masumiNo ratings yet

- BUS InterconnectionDocument27 pagesBUS InterconnectionDEEPIKA PAVUNDOSS 20BEC0285No ratings yet

- Direct Memory Access (DMA) Is A Feature of Modern Computers That Allows Certain HardwareDocument15 pagesDirect Memory Access (DMA) Is A Feature of Modern Computers That Allows Certain HardwareAshutosh KumarNo ratings yet

- WINSEM2021-22 ECE3004 TH VL2021220501593 Reference Material I 10-01-2022 LECTURE 3-Interconnection of Components-Simple Bus InterconnectDocument23 pagesWINSEM2021-22 ECE3004 TH VL2021220501593 Reference Material I 10-01-2022 LECTURE 3-Interconnection of Components-Simple Bus InterconnectDarsh GuptaNo ratings yet

- Multiple Interrupts and Buses StructureDocument17 pagesMultiple Interrupts and Buses Structureapi-3801329100% (2)

- Bus StructureDocument160 pagesBus Structurexperiac100% (2)

- Computer Organization and ArchitectureDocument25 pagesComputer Organization and ArchitectureNeel RavalNo ratings yet

- Unit-5: Types of Buses in Computer ArchitectureDocument19 pagesUnit-5: Types of Buses in Computer ArchitectureEphrage GurureNo ratings yet

- Ch02 - System InterconnectionDocument29 pagesCh02 - System InterconnectionViet Quang VoNo ratings yet

- BusesDocument19 pagesBusesprasath67No ratings yet

- Paper - History of Different Buses in A PCDocument21 pagesPaper - History of Different Buses in A PCammad ahmadNo ratings yet

- Bus Standards and TechnologiesDocument31 pagesBus Standards and TechnologiesDarmoni LaishramNo ratings yet

- Arm Ahb For McusDocument7 pagesArm Ahb For McusBharathwajan ParthasarathyNo ratings yet

- ISA BUS RaporuDocument10 pagesISA BUS Raporuravi02431No ratings yet

- Coa CT 1 QBDocument43 pagesCoa CT 1 QBNilesh bibhutiNo ratings yet

- Computer Interfacinglecture3Document20 pagesComputer Interfacinglecture3mohamed faragNo ratings yet

- Block Interconnection: Today's Topics Divide Into TwoDocument9 pagesBlock Interconnection: Today's Topics Divide Into TwoMohammad Seemab AslamNo ratings yet

- Computer Architecture & Organization UNIT 1Document17 pagesComputer Architecture & Organization UNIT 1Nihal GuptaNo ratings yet

- CHAPTER 6. Buses & Interfacing: Ec303 - Computer Architecture & OrganizationDocument17 pagesCHAPTER 6. Buses & Interfacing: Ec303 - Computer Architecture & OrganizationPrevenaManiamNo ratings yet

- Digital Signal Processing ECE301: Topic-Design of Microprocessor Based SystemsDocument3 pagesDigital Signal Processing ECE301: Topic-Design of Microprocessor Based SystemsGaurav SharmaNo ratings yet

- Lecture 1: Introduction To ARM Based Embedded SystemsDocument24 pagesLecture 1: Introduction To ARM Based Embedded SystemsSaurabh HedaNo ratings yet

- 2- A top-level view of computer function and interconnectionDocument39 pages2- A top-level view of computer function and interconnectionAliaa TarekNo ratings yet

- The Cpu: Central Processing UnitDocument26 pagesThe Cpu: Central Processing Unitjim_finn_1No ratings yet

- William Stallings Computer Organization and Architecture 7 Edition System BusesDocument50 pagesWilliam Stallings Computer Organization and Architecture 7 Edition System BusesRubeshan ShanNo ratings yet

- Bus StructureDocument160 pagesBus StructureRohit SaxenaNo ratings yet

- Coa Unit 1Document28 pagesCoa Unit 1vivek kumarNo ratings yet

- 212 Chapter06Document50 pages212 Chapter06HAU LE DUCNo ratings yet

- Chapter ModifedDocument107 pagesChapter ModifedgnanaNo ratings yet

- Introduction To The I/O Buses: Functions of Buses in ComputersDocument12 pagesIntroduction To The I/O Buses: Functions of Buses in ComputersrubinderNo ratings yet

- INTERFACING MEMORY AND I/O DEVICESDocument12 pagesINTERFACING MEMORY AND I/O DEVICESRemmy SilverNo ratings yet

- Computer ArchitectureDocument15 pagesComputer ArchitectureAbdul KapiteniNo ratings yet

- Bus ArchitectureDocument15 pagesBus ArchitectureNitin KumarNo ratings yet

- 4Document12 pages4Abdulaziz TilahunNo ratings yet

- PCI BUS SPEEDDocument41 pagesPCI BUS SPEEDNizamuddin Chapatle100% (1)

- CH 03 p2 BusStructureDocument37 pagesCH 03 p2 BusStructureAnanda Haykel IskandarNo ratings yet

- Pci BusDocument17 pagesPci BusA TNo ratings yet

- LectureSeries3 - BusesDocument19 pagesLectureSeries3 - BusesLamar ArnoldNo ratings yet

- Overview of Router Architecture and ComponentsDocument17 pagesOverview of Router Architecture and Components1975jmr 侯壮马No ratings yet

- Unit 15 Bus StructureDocument32 pagesUnit 15 Bus StructureRennie KawanguNo ratings yet

- 03-Bus-Bus Sistem (5-6)Document28 pages03-Bus-Bus Sistem (5-6)Viranata DarmaNo ratings yet

- My Lecture 2Document14 pagesMy Lecture 2Kashif KhanNo ratings yet

- Lecture MicroprocessorDocument18 pagesLecture MicroprocessorJohn wickNo ratings yet

- Lecture Microprocessor 3 - 4Document15 pagesLecture Microprocessor 3 - 4John wickNo ratings yet

- Lecture Microprocessor 1 - 2Document20 pagesLecture Microprocessor 1 - 2John wickNo ratings yet

- Experiment # 4Document5 pagesExperiment # 4John wickNo ratings yet

- Engineering Electromagnetics: Gauss' Law and DivergenceDocument33 pagesEngineering Electromagnetics: Gauss' Law and DivergenceJohn wickNo ratings yet

- AST Ascentia 200GXM/280M User GuideDocument85 pagesAST Ascentia 200GXM/280M User GuidemujmdNo ratings yet

- Experiment File3333Document38 pagesExperiment File3333teekamNo ratings yet

- SIP4 Timer Gate - CFCDocument5 pagesSIP4 Timer Gate - CFCEMD NSPCLNo ratings yet

- Airbag FsDocument2 pagesAirbag FsSanja StošićNo ratings yet

- QK3B UMA block diagramDocument33 pagesQK3B UMA block diagramNuno CarvalhoNo ratings yet

- Design and ASIC Implementation of Ethernet Switch For Network ApplicationDocument5 pagesDesign and ASIC Implementation of Ethernet Switch For Network Applicationnmrp84No ratings yet

- Embedded System of Automatic Level Control Based On FPGA: August 2010Document6 pagesEmbedded System of Automatic Level Control Based On FPGA: August 2010Mạnh TuấnNo ratings yet

- Dynamic Scheduling with ScoreboardingDocument10 pagesDynamic Scheduling with ScoreboardingArvind Krishnaa JNo ratings yet

- Lect28 2dff TFF JKFFDocument9 pagesLect28 2dff TFF JKFFpurwant10168No ratings yet

- Design and Implementation of a Unified BCD/Binary Adder/SubtractorDocument19 pagesDesign and Implementation of a Unified BCD/Binary Adder/SubtractorAbdullahJavedNo ratings yet

- Sequential Circuits: Cpe 443/L Advanced Logic CircuitsDocument35 pagesSequential Circuits: Cpe 443/L Advanced Logic CircuitsKent Genzen Corpus100% (1)

- Compal La 3281p UnlockedDocument47 pagesCompal La 3281p UnlockedHoracio AlvarezNo ratings yet

- 02 ARM Processor FundamentalsDocument65 pages02 ARM Processor Fundamentalsbengaltiger100% (2)

- VGA Controller Implementation PDFDocument36 pagesVGA Controller Implementation PDFbbshir0No ratings yet

- DP Sound Conexant 15035 DriversDocument222 pagesDP Sound Conexant 15035 DriversRajesh1146No ratings yet

- Nematron ePC215WMT: 21.5" Widescreen, Low-Cost, Fanless, Panel Mount Industrial ComputerDocument2 pagesNematron ePC215WMT: 21.5" Widescreen, Low-Cost, Fanless, Panel Mount Industrial ComputerjesusortegavNo ratings yet

- BMS CSE Lab ManualDocument84 pagesBMS CSE Lab ManualRuthwik S GowdaNo ratings yet

- E560 Cmu05 DSDocument3 pagesE560 Cmu05 DSSalvador FayssalNo ratings yet

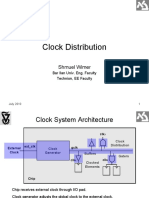

- Clock Distribution: Shmuel WimerDocument75 pagesClock Distribution: Shmuel Wimersenthilkumar100% (1)

- JNTU Hyderabad: B.Tech. II Year I & II Semester Regular/Supplementary Examinations Time Table 2011-2012Document34 pagesJNTU Hyderabad: B.Tech. II Year I & II Semester Regular/Supplementary Examinations Time Table 2011-2012MahabubnagarNo ratings yet

- MiniprojectsynopsisDocument4 pagesMiniprojectsynopsishelloNo ratings yet

- 16 Bit Multiplication 8051Document4 pages16 Bit Multiplication 8051Uday A Korat100% (5)

- Compaq Slt286 ManualDocument89 pagesCompaq Slt286 Manualalfe20001120No ratings yet

- The Highest Mountain on Earth - Mount EverestDocument4 pagesThe Highest Mountain on Earth - Mount EverestIhsanNurulHabibNo ratings yet

- COA LAb File-ShubhiDocument28 pagesCOA LAb File-ShubhiKrishan Kant ShuklaNo ratings yet

- Generating Optimizing and Verifying HDL Code With Matlab and SimulinkDocument46 pagesGenerating Optimizing and Verifying HDL Code With Matlab and Simulinkkpkarthi80No ratings yet

- DH55HC ProductGuide02 English PDFDocument82 pagesDH55HC ProductGuide02 English PDFricardogtNo ratings yet

- Accessing Real Time Clock Registers and NMI Enable BitDocument22 pagesAccessing Real Time Clock Registers and NMI Enable Bitdrhollywood2001No ratings yet

- Microprocessors and Digital ICs For Control of Power Electronics and DrivesDocument79 pagesMicroprocessors and Digital ICs For Control of Power Electronics and DrivesTianmingyuNo ratings yet