Professional Documents

Culture Documents

Otr 200 R18

Uploaded by

Admir BašićOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Otr 200 R18

Uploaded by

Admir BašićCopyright:

Available Formats

Silicon on Sapphire (SOS) Device

Technology

Toshiyuki Nakamura Hideaki Matsuhashi

Yoshiki Nagatomo

The history of the development of the Silicon on technology from Peregrine Semiconductor, including this

Sapphire (SOS) device technology is quite old, and dates UTSi® technology and began further development of the

back to the 1960s1). SOS devices are drawing a lot of process. Currently, both of the 0.50µm and the 0.25µm

attention as they are considered to be devices that are SOS processes are being developed. The 0.50µm SOS

capable of performing high-speed operations while process is at the device mass production stage, while the

consuming low amounts of power. However, to form the 0.25µm SOS process is at the application to product

silicon (Si) layer with only small crystallization defects development stage. This paper will introduce the

has been extremely difficult as there is up to a maximum fabricating process of the SOS devices and describe their

of 12.5% lattice unconformity between the crystal lattice characteristics and their advantages when compared

of the sapphire (Al2O3), which is the supporting substrate with other devices, such as bulk Si devices

of the SOS wafer and the Si crystal lattice, as shown in

Figure 1. This remained a formidable obstacle for

commercializing the SOS device products and restricted SOS wafer fabricating technology

all activities to research and development. The SOS wafer fabricating process using the UTSi®

technology is described in Figure 2. Firstly, an epitaxial

R side growth of the Si film is formed on the sapphire substrate

as shown in Figure 2 (a). The condition of the deposited

Si film at this time will show a lot of crystallization defects

due to the lattice unconformity with the sapphire. Next Si

ions are implanted inside the Si film, as shown in Figure 2

(b). This destroys the crystallization effects of the Si film

near the boundary with the sapphire substrate and

converts it into an amorphous condition. A heat treatment

is conducted in an oxidizing atmosphere, as shown in

Figure 2 (c), to form an Si film with far fewer flaws by re-

crystallizing the amorphous Si film with a solid phase

epitaxial growth from the Si film near the proximity of the

surface with fewer flaws. The oxide film is then removed

to obtain the desired Si film.

Al atom

Crystallization defects

(a) Silicon film formation

Si atom

(a) Sapphire crystal structure Silicon film

Sapphire

12.5%

(b) Implantation of silicon ion

Silicon film

Amorphous

6.0%

Sapphire

(b) Lattice unconformity rate of sapphire and silicon

Fig. 1 (a) Crystal structure of sapphire and

(b) Lattice unconformity with silicon crystal (c) Heat treatment & surface oxidation

SiO2 (later removed)

As we entered the 1990s, Peregrine Semiconductor,

of the United States, succeeded in their practical

application of a technology that greatly improved the Ultra thin Silicon

crystallization characteristics of the Si film on the

sapphire substrate2), called Ultra Thin Si (UTSi®), which

resulted in an acceleration of the commercialization of

SOS devices. Oki Electric implemented the SOS device Fig. 2 SOS wafer fabricating flow

66 Oki Technical Review

October 2004/Issue 200 Vol.71 No.4

Special Issue on Technologies that Support the e-Society

Twin Defects Complete separation of the silicon layer is possible

Silicon film

Sapphire Sapphire

(a) SOS device

SOS wafer fabricated by SOS wafer fabricated by

conventional technology UTSi® technology

Fig. 3 Transmission electron microscopic photograph3) of a

cross section of an SOS wafer P well N well

A transmission electron microscopic photograph of a Bulk Si

cross section of the SOS wafer is shown in Figure 3.

Conventional SOS wafers contain many crystallization (b) Bulk Si device

defects, primarily those known as “Twin Defects”. It is

possible to verify that with the SOS wafer fabricated using Fig. 5 Comparison of a MOSFET cross sectional structure of an

the aforementioned UTSi® technology, a favorable Si film SOS device and bulk Si device

can be formed with much fewer crystallization defects. By

using the UTSi® technology, it has become possible to P well

form Si films on sapphire substrates with a superior

crystallization, even when the formed film is about as thin

as 100nm.

Structure and fabricating process of the

SOS device

Separation: Narrow Separation: Wide

A transmission electron microscopic photograph of a

cross section of the SOS device is shown in Figure 4.

The SOS device is fabricated by forming a metal-oxide

semiconductor field-effect transistor (MOSFET) on the Si

film located on top of a sapphire substrate, which is an

insulator, as shown in Figure 5 (a). Since elements are

formed on top of insulating substrates, the footprints of N well

the source and drain, or the junction capacitance, is

structurally extremely small. Further, it is also possible to (a) SOS device (b) Bulk Si device

completely isolate individual elements by using element

separations, such as the local oxidation of Si (LOCOS). Fig. 6 Comparison of layout structures of an SOS device and

Therefore, the structure will be simple and small, making bulk Si device

it unnecessary to form well regions of a low impurity

concentration, essential for bulk Si devices as shown in The fabricating process flow of an SOS device is

Figure 5 (b). described, in Figure 7. Firstly, an element-separating

A comparison of structures from the aspect of layout region is formed with LOCOS, as shown in Figure 7 (a).

design is shown in Figure 6. The element separating The process continues with the individual injection of

distance between the NMOSFET and PMOSFET can be impurities to determine the threshold voltage, Vt, as

reduced because the well region is unnecessary with shown in Figure 7 (b). Next, the gate electrodes are

SOS devices, as described above. Further, since there is formed as shown in Figure 7 (c). Once the sidewalls have

no need for a contact to stabilize the electric potential of formed, as shown in Figure 7 (d), impurities are injected

the well region, it is easier to improve integration with to form the source and drain regions. Then contacts are

SOS devices than bulk Si devices. formed and wired to form the desired circuitry (Figure 7

(e)).

The SOS device fabricating process described here,

is the same as for the SOI device fabricated by forming

the MOSFET on the Silicon on Insulator (SOI) substrate,

Silicide which is fabricated by forming an embedded oxide film

layer and thin Si layer on the silicon substrate. Oki

Polysilicon Electric previously perfected the completely depleted-

gate type SOI device technology with a history of applying this

Gate

insulation technology to the fabrication of ultra-low power

film

Silicon layer consuming LSI. The SOS device technology has a great

affinity to this SOI device technology.

Sapphire

100nm

Fig. 4 Transmission electron microscopic photograph of a

cross section of an SOS MOSFET device

Oki Technical Review 67

October 2004/Issue 200 Vol.71 No.4

Si film 1.E+00

(a) Element separation PMOSFET: NMOSFET:

1.E-02 L/W = 0.5/50µm L/W = 0.8/50µm

1.E-04

1.E-06

Ids (A)

Sapphire

1.E-08 S value = 71mV/dec. S value = 70mV/dec.

LOCOS

1.E-10

(b) Impurity injection

1.E-12

1.E-14

-4 -2 0 2 4

Vgs (V)

Fig. 8 Ids - Vgs characteristics of an SOS MOSFET with a gate

length of 0.5µm

Resist

(c) Gate formation

1000

Maximum oscillation frequency [ GHz ]

SOS

Bulk Si 0.25µm SOS

90GHz

0.50µm SOS

42GHz

100

(d) Source and drain regions formation

10

0.01 0.1 1

Gate length [ µm ]

Fig. 9 Transistor high frequency characteristics of an SOS

Resist device and a bulk Si device

(e) Wiring

A comparison diagram for the transistor high

frequency characteristics of an SOS device and a bulk Si

device is shown in Figure 9. The performance of the

transistors can be directly compared with their high

frequency characteristics, by observing the maximum

oscillation frequency (Fmax). With the SOS device, Fmax =

NMOSFET PMOSFET 42GHz can be attained with a gate length of 0.50µm at

90GHz and above with 0.25µm. The Fmax of an SOS

device is approximately four times that of a bulk Si

device.

Fig. 7 Fabricating process flow of an SOS device

The high frequency characteristics of passive

Thus, the fabrication of SOS devices, as described elements are compared using the Q value (Quality

above, can be carried out similar to that of the SOI Factor) of inductors. Q values represent the energy loss,

devices by utilizing the same equipment used for bulk Si with higher values representing superior characteristics.

devices and by applying the bulk Si device process, An example of the Q value of the fabricated inductor and

which already has a proven history. the frequency characteristics of inductance L is shown in

Figure 10. The Q value is 8.7 for 1.7GHz with a bulk Si

device, while a Q value of 14.7 was attained for 6.5GHz

Characteristics of the SOS device with an SOS device. Since the passive elements of SOS

devices are fabricated on insulating substrates, higher Q

The lds - Vgs characteristics of the SOS device are

values than those of bulk Si devices, can be obtained in

shown in Figure 8. It is possible to evaluate the amount of

the high frequency range.

change of Vgs necessary to add one digit to Ids , or the

sub-threshold characteristics (S value) from the Ids - Vgs

characteristics. Smaller S values represent more superior Features of the SOS device

characteristics. The S values of the SOS devices show

favorable characteristics, with 70mV/decade for Summarizing the features of SOS devices:

NMOSFET and 71mV/decade for PMOSFET. Further, • Completely depleted-type MOSFET transistor.

since bulk Si and partially depleted-type MOSFET in • Complete separation of elements is possible.

general, indicate values of about 85mV/decade, it is • Junction capacitance is extremely small, which

believed that the SOS device runs a completely depleted

benefits high frequency performance and low power

operation.

consumption characteristics.

68 Oki Technical Review

October 2004/Issue 200 Vol.71 No.4

Special Issue on Technologies that Support the e-Society

Then again high integration and the large areas of

20

chips, such as those of bulk Si or SOI devices, are

SOS currently not possible since the flatness of the surfaces

15 Bulk Si for sapphire wafers are somewhat inferior. Even when the

Quality Factor

UTSi®1) technology is used and the quality of SOS wafers

10

are improved significantly, a few lattice defects still

remain. Further, the cost of a large-diameter sapphire

5

wafer is extremely high, which is a factor that will raise

the device’s cost. These issues, however, seem to have

0

been solved and the further advantages of SOS devices

0 2 4 6 8 10

are secured as the demand for SOS devices increases

Frequency [ GHz ] and improvement of SOS wafer quality, as well as a

reduction in costs, occur.

Conclusion

25

SOS Existing fabricating equipment, used for producing

20

Bulk Si bulk Si devices, can be used for the production of SOS

15 devices as well. SOS devices can also be fabricated by

L [ nH ]

using the proven bulk Si fabricating process. Further, it is

10

possible to implement a higher integration than with

5 GaAs devices and advantages exist over bulk Si or SOI

devices in terms of higher frequency performance and

0 lower power consumption. Furthermore, it is possible to

0 2 4 6 8 10 fabricate passive elements, such as inductors, with

Frequency [ GHz ] greater high frequency characteristics than those of bulk

Si or Bi-CMOS devices.

Fig. 10 Comparison of high frequency inductance We are currently developing these products for

characteristics of an SOS bulk device and a bulk Si device communications, but in the future we expect there will be

many more applications that utilize the advantages of

• Realization of high performance passive elements high frequency performances with low power

(such as inductors). consumption characteristics. Further, because the

Further, since they are based on sapphire substrates, sapphire is clear, it is possible to use these devices in

they have: modules with a mixed load of optical devices as well. We

• Extremely high radiation resistance. believe that SOS devices, with these advantages, will

• Low crosstalk. become key devices for the ubiquitous era.

• Clear state of elements after the completion of a

process. References

These can be mentioned as beneficial features as well. 1) H.M. Manasevit and W.I. Simpson: “Single-Crystal

A comparison of features between the SOS device, bulk Silicon on a Sapphire Substrate”, J.A.P., Vol.35

Si, SOI, Bi-CMOS and gallium arsenide (GaAs) devices, are pp.1349-1351, 1964.

shown in Table 1. Since the SOS device is fabricated on top

of a sapphire substrate, which is a completely insulating 2) M.L. Burgener and R.E. Reedy: “Minimum Charge

substrate and a completely depleted operating MOSFET, it FET Fabricated on an Ultrathin Silicon on a Sapphire

has advantages in terms of high frequency performance Wafer”, United States Patent No.5,416,043, 1995.

and low power consuming characteristics. Further, since it is 3) Y. Nagatomo and R.E. Reedy: “Latest Trends of SOS

also possible to fabricate passive elements with higher Q (Silicon on Sapphire) Technology”, Denshi Zairyo, Vol.

values, such as an inductor, there is a vast advantage over 42, No. 5, 2003.

other types of devices.

Table 1 Comparison of various device characteristics Authors

Toshiyuki Nakamura: Silicon Solutions Company,

SOS Bulk Si SOI Bi-CMOS GaAs Research Div., New Technology R&D Dept.

High frequency Hideaki Matsuhashi: Silicon Solutions Company,

performance Research Div., New Technology R&D Dept.

Yoshiki Nagatomo: Silicon Solutions Company, Research

High Q inductor

Div., New Technology R&D Dept., General Manager

Integration

Lowe power

consumption

Cost

Oki Technical Review 69

October 2004/Issue 200 Vol.71 No.4

You might also like

- Compendium of Atomic Alkali Resistant Optical Thin Films, Diffusion and Electrical Mobility in Diode Pumped Alkali Lasers (DPALs)From EverandCompendium of Atomic Alkali Resistant Optical Thin Films, Diffusion and Electrical Mobility in Diode Pumped Alkali Lasers (DPALs)No ratings yet

- Soimumps Process Flow: Keith Miller Foundry Process EngineerDocument17 pagesSoimumps Process Flow: Keith Miller Foundry Process Engineerrfar0028No ratings yet

- Vlsi - CHP04Document16 pagesVlsi - CHP04feki2607No ratings yet

- VLSI Physical Design Automation: Lecture 2. Review of Device/VLSI/AlgorithmDocument42 pagesVLSI Physical Design Automation: Lecture 2. Review of Device/VLSI/AlgorithmarunNo ratings yet

- In Frame FabricationDocument1 pageIn Frame Fabricationhasib_07No ratings yet

- Thin Solid Films, 31: (1976) 235-241 © Elsevier Sequoia S.A., Lausanne - Printed in SwitzerlandDocument7 pagesThin Solid Films, 31: (1976) 235-241 © Elsevier Sequoia S.A., Lausanne - Printed in SwitzerlandMuizzudin AzaliNo ratings yet

- Chapter 3 Fabrication of Cmos Integrated Circuits Jin Fu Li Department of Electrical Engineering National Central University Jhongli TaiwanDocument37 pagesChapter 3 Fabrication of Cmos Integrated Circuits Jin Fu Li Department of Electrical Engineering National Central University Jhongli TaiwanYusra AmeenNo ratings yet

- The Mainstreaming of SOI: G. K. Celler and Andrew WittkowerDocument4 pagesThe Mainstreaming of SOI: G. K. Celler and Andrew WittkowerMarco Aurélio DonatoNo ratings yet

- Smith 1992Document23 pagesSmith 1992Luisa CenchaNo ratings yet

- MEMS Design Chap 2-MEMS ProcessesDocument31 pagesMEMS Design Chap 2-MEMS ProcessesvuonglupNo ratings yet

- SOI TechnologyDocument12 pagesSOI Technologycomputer48No ratings yet

- Lec 03-04Document37 pagesLec 03-04Basem HeshamNo ratings yet

- State-of-the-Art and Perspectives On Silicon Waveguide Crossings: A ReviewDocument16 pagesState-of-the-Art and Perspectives On Silicon Waveguide Crossings: A ReviewKunal SharmaNo ratings yet

- Simulation of Electrochemical Etching of Silicon With COMSOLDocument6 pagesSimulation of Electrochemical Etching of Silicon With COMSOLTestingAccNo ratings yet

- Chapter 2Document37 pagesChapter 2gopismiles1987No ratings yet

- 2 TSS SiC Material Pres To Dr. Santi Dec 5, 2019Document39 pages2 TSS SiC Material Pres To Dr. Santi Dec 5, 2019Kunal RajaNo ratings yet

- Integrated Circuit (IC) FabricationDocument39 pagesIntegrated Circuit (IC) FabricationSHAIK MUSTHAFANo ratings yet

- Characterization of SOI PMOSFET Using Silvaco TCAD ToolsDocument7 pagesCharacterization of SOI PMOSFET Using Silvaco TCAD ToolseditorijaiemNo ratings yet

- Giúdice, 2004, Combinational Use of Extenders With Lamellar ZincDocument14 pagesGiúdice, 2004, Combinational Use of Extenders With Lamellar Zinccyclo DreamNo ratings yet

- 02.effects of Silicon On Microstructure and Corrosion Resistance of Diamond-Like-Carbon Film Prepared On 2024 Aluminum Alloy by PECVDDocument7 pages02.effects of Silicon On Microstructure and Corrosion Resistance of Diamond-Like-Carbon Film Prepared On 2024 Aluminum Alloy by PECVDMarco Di MaioNo ratings yet

- Solar CellsDocument25 pagesSolar Cells김동욱No ratings yet

- Materials Letters: Doo Won Lee, Muhammad Fahad Bhopal, Soo Hong LeeDocument4 pagesMaterials Letters: Doo Won Lee, Muhammad Fahad Bhopal, Soo Hong LeeM Fahad BhopalNo ratings yet

- Who, Jun 2011Document4 pagesWho, Jun 2011emediageNo ratings yet

- CMOS Technology: Only 15,432,758 More Mosfets To Do..Document30 pagesCMOS Technology: Only 15,432,758 More Mosfets To Do..manjulavkNo ratings yet

- Industrial Silicon Wafer Solar CellDocument15 pagesIndustrial Silicon Wafer Solar CellranggaNo ratings yet

- Afe 1 - 2020 - 11Document6 pagesAfe 1 - 2020 - 11Amit PathakNo ratings yet

- Integrated Circuits (IC) : EEE 1217 Analog Electronics CSE'20Document22 pagesIntegrated Circuits (IC) : EEE 1217 Analog Electronics CSE'20Ebrahim SiddikNo ratings yet

- Journal PublictionDocument5 pagesJournal PublictionM. Naeem JawaidNo ratings yet

- FA PPT - 1Document18 pagesFA PPT - 1babsjjkklNo ratings yet

- Presentation 1 LicDocument28 pagesPresentation 1 LicreporterrajiniNo ratings yet

- Zinc Coatings PDFDocument12 pagesZinc Coatings PDFMuhammadImaduddienSalamNo ratings yet

- C'Sij - Solener.2004.06.02320210911 22562 1h2coc2 With Cover Page v2Document8 pagesC'Sij - Solener.2004.06.02320210911 22562 1h2coc2 With Cover Page v2Aruma Gamage ruwan PrasannaNo ratings yet

- Soimumps Design Handbook: A Mumps® ProcessDocument26 pagesSoimumps Design Handbook: A Mumps® ProcessFallon RiosNo ratings yet

- Gatan, Inc. Preparation of A Cross-Sectional Semiconductor IC Device Sample For SEM ObservationDocument4 pagesGatan, Inc. Preparation of A Cross-Sectional Semiconductor IC Device Sample For SEM ObservationRutvij KotechaNo ratings yet

- Chap.3 CMOS Processing Technology (1) Technology (1) : Integrated Circuits Lecture Slides GDocument11 pagesChap.3 CMOS Processing Technology (1) Technology (1) : Integrated Circuits Lecture Slides GAkash TiwariNo ratings yet

- Oxidation PPT PDFDocument72 pagesOxidation PPT PDFdajNo ratings yet

- Frost&Sullivan Polysilicon 2010Document152 pagesFrost&Sullivan Polysilicon 2010Александр Козлов100% (1)

- Lec - 14 Diffusion - Theory of DiffusionDocument62 pagesLec - 14 Diffusion - Theory of DiffusionGAURAV CHHETRINo ratings yet

- 04.deposition of Si-DLC Film and Its Microstructural, Tribological and Corrosion PropertiesDocument6 pages04.deposition of Si-DLC Film and Its Microstructural, Tribological and Corrosion PropertiesMarco Di MaioNo ratings yet

- Silicon On InsulatorDocument6 pagesSilicon On InsulatorShivam VishnoiNo ratings yet

- 0105ecstDocument6 pages0105ecstqiha nahdahNo ratings yet

- Ch13 - Wafers and Chips PDFDocument51 pagesCh13 - Wafers and Chips PDFsaandilianNo ratings yet

- National Dong Hwa University (No. 1, Sec. 2, Da Hsueh RD., Shoufeng, Hualien 97401, Taiwan)Document1 pageNational Dong Hwa University (No. 1, Sec. 2, Da Hsueh RD., Shoufeng, Hualien 97401, Taiwan)哈特例No ratings yet

- SM ART-CUT@ Techno Logy S 0 1 A New High Volume Application For Ion ImplantationDocument4 pagesSM ART-CUT@ Techno Logy S 0 1 A New High Volume Application For Ion ImplantationMarco Aurélio DonatoNo ratings yet

- Mems Capacitive Accelerometer: (Design and Fabrication)Document16 pagesMems Capacitive Accelerometer: (Design and Fabrication)Sarmast Bilawal KhuhroNo ratings yet

- (Charles Bukowski) Mockingbird Wish Me LuckDocument7 pages(Charles Bukowski) Mockingbird Wish Me Lucksweety kumariNo ratings yet

- Patent Application Publication (10) Pub. No.: US 2007/0204519 A1Document9 pagesPatent Application Publication (10) Pub. No.: US 2007/0204519 A1rat0708No ratings yet

- Nicholas ThesisDocument185 pagesNicholas ThesissalmaamsayeddNo ratings yet

- Deep Wet Etching of Borosilicate Glass Using An Anodically Bonded Silicon Substrate As Mask PDFDocument4 pagesDeep Wet Etching of Borosilicate Glass Using An Anodically Bonded Silicon Substrate As Mask PDFtedmozbiNo ratings yet

- VLSI Technology Course Final SlidesDocument215 pagesVLSI Technology Course Final SlidesAyush SinghNo ratings yet

- IC FabricationDocument27 pagesIC FabricationJohn PaulNo ratings yet

- John Campbell - NucleationDocument4 pagesJohn Campbell - NucleationMostafa OthmanNo ratings yet

- Hochbaum 2009Document5 pagesHochbaum 2009Ponchirris CGNo ratings yet

- Characteristic of Al 7075 Reinforced Nano Sic Composites As An Armour Material Produced by Squeeze Casting ProcessDocument6 pagesCharacteristic of Al 7075 Reinforced Nano Sic Composites As An Armour Material Produced by Squeeze Casting ProcessYudhistira AdityawardhanaNo ratings yet

- CH 03 CMOS Fabrication Part 01Document18 pagesCH 03 CMOS Fabrication Part 01muneeb.abrarNo ratings yet

- Amorphous SeDocument41 pagesAmorphous SeMoeNo ratings yet

- Unit Iii-Surface MicromachiningDocument19 pagesUnit Iii-Surface MicromachiningCHETAN SETIYANo ratings yet

- Silicon Oxide Thin Films Prepared by Vacuum Evaporation and Sputtering Using Silicon MonoxideDocument6 pagesSilicon Oxide Thin Films Prepared by Vacuum Evaporation and Sputtering Using Silicon MonoxideFarid ElsehrawyNo ratings yet

- Thin Aluminum Films PDFDocument13 pagesThin Aluminum Films PDFsmani170No ratings yet

- Fabrication Process: Kanada TechnologiesDocument33 pagesFabrication Process: Kanada TechnologiesKarthigai ValliNo ratings yet

- RD 85 SpecDocument2 pagesRD 85 SpecAdmir BašićNo ratings yet

- 90041-As Rev2Document2 pages90041-As Rev2Admir BašićNo ratings yet

- Payment Confirmation Potvrda O Izvrsenom PlacanjuDocument1 pagePayment Confirmation Potvrda O Izvrsenom PlacanjuAdmir BašićNo ratings yet

- RAM Mapping 32 4 LCD Controller For I/O MC: FeaturesDocument20 pagesRAM Mapping 32 4 LCD Controller For I/O MC: FeaturesjahenNo ratings yet

- ACS71240 DatasheetDocument33 pagesACS71240 DatasheetAdmir BašićNo ratings yet

- ASR6601 Datasheet V1.0.2Document21 pagesASR6601 Datasheet V1.0.2Admir BašićNo ratings yet

- ZIGBEEDocument12 pagesZIGBEEAdmir BašićNo ratings yet

- E32-900M30S UserManual EN v1.0Document14 pagesE32-900M30S UserManual EN v1.0Admir BašićNo ratings yet

- E220-900M30S UserManual EN v1.0Document14 pagesE220-900M30S UserManual EN v1.0Admir BašićNo ratings yet

- Specifications: PartsDocument1 pageSpecifications: PartsAdmir BašićNo ratings yet

- E22-900T22S UserManual EN v1.2Document26 pagesE22-900T22S UserManual EN v1.2Admir BašićNo ratings yet

- 7812 Datasheet PDFDocument28 pages7812 Datasheet PDFSatkar AgrawalNo ratings yet

- E19-868M30S Usermanual EN v1.20Document14 pagesE19-868M30S Usermanual EN v1.20Admir BašićNo ratings yet

- Grupa 1 14 15 16 17 20 21 22 23 25 26 27 28 42 43 44 45 55 56 58 59 30 33 34 35Document1 pageGrupa 1 14 15 16 17 20 21 22 23 25 26 27 28 42 43 44 45 55 56 58 59 30 33 34 35Admir BašićNo ratings yet

- nRF24LE1 Product Specification Rev1 6Document196 pagesnRF24LE1 Product Specification Rev1 6Admir BašićNo ratings yet

- Kem R7002 Ec2 Ee2-1104574Document19 pagesKem R7002 Ec2 Ee2-1104574Admir BašićNo ratings yet

- T 1000S ManualDocument8 pagesT 1000S ManualAdmir BašićNo ratings yet

- T 1000S ManualDocument8 pagesT 1000S ManualAdmir BašićNo ratings yet

- NET Micro Framework White PaperDocument30 pagesNET Micro Framework White PaperAdmir BašićNo ratings yet

- The Lang 20W Class-A Mosfet AmplifierDocument7 pagesThe Lang 20W Class-A Mosfet AmplifiermoisesNo ratings yet

- Threshold VoltageDocument33 pagesThreshold Voltagemjmanish100% (1)

- Sound Fire ExtinguisherDocument5 pagesSound Fire ExtinguisherVendinGNo ratings yet

- Ec8351 Electronic Circuits I 1901883722 Ec8351 Ec IDocument19 pagesEc8351 Electronic Circuits I 1901883722 Ec8351 Ec IyogiNo ratings yet

- Me Vlsi Lab ManualDocument66 pagesMe Vlsi Lab Manualaarthi.lj5371No ratings yet

- Hybrid Power Boost (HPB) and Narrow VDC (NVDC) Combo Battery Charger With Smbus InterfaceDocument2 pagesHybrid Power Boost (HPB) and Narrow VDC (NVDC) Combo Battery Charger With Smbus InterfaceSelmar Cavalcanti0% (1)

- Question Bank: Srinivasa Institute of Engineering and TechnologyDocument45 pagesQuestion Bank: Srinivasa Institute of Engineering and TechnologyVijay M100% (2)

- Ultra Low Output Voltage Linear N-FET Controller: Global Mixed-Mode Technology IncDocument1 pageUltra Low Output Voltage Linear N-FET Controller: Global Mixed-Mode Technology IncDaniel Norberto DemariaNo ratings yet

- Design and Development of Microcontroller Based Solar Charge ControllerDocument4 pagesDesign and Development of Microcontroller Based Solar Charge ControllerolumideNo ratings yet

- ECE Proposed New Syllabus PDFDocument79 pagesECE Proposed New Syllabus PDFE.ramakrishnaNo ratings yet

- Optimize Design of Full Subtractor Using 45nm Technology: Swetha S, Reddy NSS and Hemalatha RDocument5 pagesOptimize Design of Full Subtractor Using 45nm Technology: Swetha S, Reddy NSS and Hemalatha RSwetha VanamNo ratings yet

- Mosfet: Prepared By: Gagandeep KaurDocument16 pagesMosfet: Prepared By: Gagandeep KaurGAGANNo ratings yet

- Ec8252 SyllabusDocument1 pageEc8252 SyllabusSarika AyyathuraiNo ratings yet

- Power Electronics - Unit-1 PDFDocument44 pagesPower Electronics - Unit-1 PDFdeepu4303No ratings yet

- Flux Gate Sensor Analysis PDFDocument17 pagesFlux Gate Sensor Analysis PDFmayaNo ratings yet

- Class E Amp Design PDFDocument12 pagesClass E Amp Design PDFAshutoshSharmaNo ratings yet

- Tndte M Scheme Ece BookDocument194 pagesTndte M Scheme Ece Booksmagendiran100% (2)

- Top249 1 PDFDocument52 pagesTop249 1 PDFCarlos Henrique Dos SantosNo ratings yet

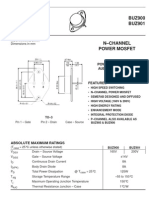

- BUZ900Document4 pagesBUZ900Miloud ChouguiNo ratings yet

- An 43Document28 pagesAn 43Jason WilsonNo ratings yet

- Mtw8n60e DDocument9 pagesMtw8n60e DAtiqurrehman UmairNo ratings yet

- DTT2 inDocument133 pagesDTT2 insỹ hoàng trầnNo ratings yet

- Ane Str3a100Document17 pagesAne Str3a100vietanh_askNo ratings yet

- str-w6754 Ds enDocument8 pagesstr-w6754 Ds enAdah BumbonNo ratings yet

- Motorola Application NotesDocument10 pagesMotorola Application Notesvasudeva yasasNo ratings yet

- Transform Calculus, Fourier Series and Numerical TechniquesDocument3 pagesTransform Calculus, Fourier Series and Numerical TechniquesRaimond RosarioNo ratings yet

- Chiplevel RepairingDocument3 pagesChiplevel Repairingshriram1082883No ratings yet

- MP3389 r1.04Document16 pagesMP3389 r1.04Kevin Yang YangNo ratings yet

- Electrical - Engg 3rd To 6th SemDocument74 pagesElectrical - Engg 3rd To 6th SembikrambhoiNo ratings yet

- 2N6660/2N6661 N-Channel Enhancement-Mode Vertical Dmos Fets: Features General DescriptionDocument3 pages2N6660/2N6661 N-Channel Enhancement-Mode Vertical Dmos Fets: Features General DescriptionThe ProgrammerNo ratings yet