Professional Documents

Culture Documents

Manual PDF

Manual PDF

Uploaded by

Obed AhmadOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Manual PDF

Manual PDF

Uploaded by

Obed AhmadCopyright:

Available Formats

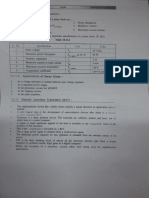

EE-231L

Electronics–I Lab Manual

Spring 2021

Edited by: _______________

_______________

Student Name: ___________________

Reviewed by: ________________

Registration No.: ________________

Approved by: _____________________

Faculty: ______________________

Section: ______________________

Faculty of Electrical Engineering

Ghulam Ishaq Khan Institute of Engineering Sciences and Technology

Instructions for Students

1. Attendance is mandatory for students in all the labs. If a student is absent from a lab due to any

reason, he/she will have to get written permission of the Dean to perform that lab.

2. Students should bring their textbooks to the lab, so that they can refer to theory and diagrams

whenever required.

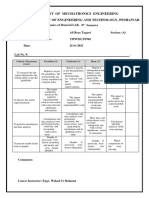

3. The assessment sheet at the end of every lab looks like this:

Student Name: ______________________ Reg. #: _________________

Score

PLOs Poor Satisfactory Good Excellent

CLOs

0 0.5-1.0 1.5-2.0 2.5-3.0

Can

Can setup and Can setup and

independently

Cannot setup or handle the handle the

CLO-1 PLO-5 setup, operate

handle the apparatus apparatus with apparatus with

and handle the

some help minimal help

apparatus

Data recorded

Data recorded

and presented is All required

and presented is

complete, but data is recorded

Data recorded only partially

accuracy is not and presented

with considerable complete. The

CLO-2 PLO-5 as per accurately and

assistance from required format

requirement. completely in

instructor is followed but

The required the required

with few

format is format

deficiencies

followed

Analyzes data

Analyzes and

correctly

Unable to analyze interprets data Analyzes and

however unable interprets data

and interpret data correctly for

CLO-3 to interpret it for correctly for all

PLO-4 for any tasks/ few tasks/

tasks/ tasks/

experiments in the experiments in

experiments in experiments in

lab the lab the lab

the lab

Student hands

Student does not over the

CLO-4 hand over the workstation in

PLO-8 the required NA

workstation in the

manner NA

required manner

Total Score in Lab /10

Instructor Signature: _________________

Date: _________________

EE231L – Electronics-I Lab Manual Page 2

Table of Contents

Lab - 1: Diode Characteristics ……………………….……………………….8

1.1 Objective ...................................................................... Error! Bookmark not defined.

...............................................................9

1.2 Equipment Required ..............................................................................................................9

1.3 Résumé of Theory....................................................................................................................9

1.4 Part 1 – Diode Test ............................................................................................................... 10

1.5 Part 2 – Forward Bias Diode Characteristics ............................................................. 11

1.6 Part 3 – Reverse Bias Diode Characteristics .............................................................. 13

1.7 Part 4 – DC Resistance ........................................................................................................ 13

1.8 Part 5 – AC Resistance ........................................................................................................ 14

1.9 Part 6 – Firing Potential ..................................................................................................... 15

1.10 Questions ................................................................................................................................. 15

1.11 Assessment Sheet ..................................................... Error! Bookmark not defined.

.............................................................16

1.12 Equipment Required ............................................... Error! Bookmark not defined.

..............................................................16

1.13 Résumé of Theory................................................................................................................. 16

1.14 Part 1 – Threshold Voltage................................................................................................ 17

1.15 Part 2 – Series Configuration ........................................................................................... 17

1.16 Part 3 – Parallel Configuration ........................................................................................ 20

1.17 Part 4 – Bridge Configuration .......................................................................................... 21

1.18 Assessment Sheet ................................................................................................................. 22

Lab - 2: Half-Wave and Full-Wave Rectification............................................................. 23

2.1 Objective .................................................................................................................................. 23

2.2 Equipment Required ........................................................................................................... 23

2.3 Résumé of Theory................................................................................................................. 23

2.4 Part 1 – Threshold Voltage................................................................................................ 24

2.5 Part 2 – Half-Wave Rectification ..................................................................................... 24

2.6 Part 3 – Half-Wave Rectification (continued)............................................................ 26

2.7 Part 4 – Half-Wave Rectification (continued)............................................................ 27

2.8 Part 5 – Full-Wave Rectification (Bridge Configuration) ...................................... 29

2.9 Assessment Sheet ................................................................................................................. 33

Lab – 3.1: Clipping Circuits ........................................................................................................ 33

3.1 Objective .................................................................................................................................. 34

3.2 Equipment Required ........................................................................................................... 34

3.3 Résumé of Theory................................................................................................................. 34

3.4 Part 1 – Threshold Voltage................................................................................................ 34

3.5 Part 2 – Parallel Clippers ................................................................................................... 34

3.6 Part 3 – Parallel Clippers (continued) .......................................................................... 38

3.7 Part 4 – Series Clippers ...................................................................................................... 39

3.2 Clamping Circuits .................................................................................................................... 42

3.8 Résumé of Theory................................................................................................................. 42

EE231L – Electronics-I Lab Manual Page 3

3.9 Part 1 – Threshold Voltage................................................................................................ 42

3.10 Part 2 – Clampers (R, C, Diode Combination) ............................................................ 42

3.11 Part 3 – Clampers with a DC Battery ............................................................................. 44

3.12 Part 4 – Clampers (Sinusoidal Input)............................................................................ 47

3.13 Part 5 – Clampers (Effect of R) ........................................................................................ 49

3.14 Assessment Sheet ................................................................................................................. 51

Lab - 4: Light-Emitting and Zener Diodes ......................................................................... 52

4.1 Objective .................................................................................................................................. 52

4.2 Equipment Required ........................................................................................................... 52

4.3 Résumé of Theory................................................................................................................. 52

4.4 Part 1 – LED Characteristics ............................................................................................. 53

4.5 Part 2 – Zener Diode Characteristics ............................................................................ 55

4.6 Part 3 – Zener Diode Regulation ..................................................................................... 57

4.7 Part 4 – LED-Zener Diode Combination....................................................................... 58

4.8 Assessment Sheet ................................................................................................................. 60

Lab - 5: Bipolar Junction Transistor (BJT) ....................................................................... 61

5.1 Objectives ................................................................................................................................ 61

5.2 Equipment Required ........................................................................................................... 61

5.3 Résumé of Theory................................................................................................................. 61

5.4 Part 1 – Determination of the Transistor’s Type, Terminals, and Material ... 61

5.5 Part 2 – The Collector Characteristics .......................................................................... 64

5.6 Part 3 – Variation of and ............................................................................................. 65

5.7 Exercises .................................................................................................................................. 66

5.8 Assessment Sheet ................................................................................................................. 67

Lab - 6: Fixed and Voltage- Divider Bias of BJTs ............................................................ 68

6.1 Objective .................................................................................................................................. 68

6.2 Equipment Required ........................................................................................................... 68

6.3 Résumé of Theory................................................................................................................. 68

6.4 Part 1 – Determining ....................................................................................................... 68

6.5 Part 2 – Fixed-Bias Configuration .................................................................................. 69

6.6 Part 3 – Voltage-Divider Configuration ........................................................................ 70

6.7 Exercises .................................................................................................................................. 72

6.8 Assessment Sheet ................................................................................................................. 74

Lab - 7: Emitter and Collector Feedback Bias of BJT .................................................... 75

7.1 Objective .................................................................................................................................. 75

7.2 Equipment Required ........................................................................................................... 75

7.3 Résumé of Theory................................................................................................................. 75

7.4 Part 1 – Emitter-Bias Configuration: Determining .............................................. 75

7.5 Part 2 – Emitter-Bias Configuration: Determining Operating Point ................. 76

7.6 Part 3 – Collector Feedback Configuration (RE = 0 ) ........................................... 77

7.7 Part 4 – Collector Feedback Configuration (with RE) ............................................. 79

7.8 Part 5 – Problems and Exercises .................................................................................... 80

7.9 Assessment Sheet ................................................................................................................. 83

EE231L – Electronics-I Lab Manual Page 4

Lab - 8: Design of BJT Bias Circuits ..................................................................................... 84

8.1 Objective .................................................................................................................................. 84

8.2 Equipment Required ........................................................................................................... 84

8.3 Résumé of Theory................................................................................................................. 84

8.4 Part 1 – Collector-Feedback Configuration ................................................................ 85

8.5 Part 2 – Emitter-Bias Configuration .............................................................................. 87

8.6 Part 3 – Voltage-Divider Configuration ........................................................................ 90

8.7 Exercises .................................................................................................................................. 92

8.8 Assessment Sheet ................................................................................................................. 94

Lab - 9: JFET Characteristics ................................................................................................. 95

9.1 Objective .................................................................................................................................. 95

9.2 Equipment Required ........................................................................................................... 95

9.3 Résumé of Theory................................................................................................................. 95

9.4 Part 1 – Measurement of Saturation Current and Pinch-Off Voltage ............... 95

9.5 Part 2 – Output Characteristics ....................................................................................... 97

9.6 Part 3 – Transfer Characteristics .................................................................................... 98

9.7 Exercises .................................................................................................................................. 99

9.8 Assessment Sheet .............................................................................................................. 102

Lab - 10: JFET Bias Circuits ................................................................................................... 103

10.1 Objective ............................................................................................................................... 103

10.2 Equipment Required ........................................................................................................ 103

10.3 Résumé of Theory.............................................................................................................. 103

10.4 Part 1 – Fixed-Bias Network.......................................................................................... 103

10.5 Part 2 – Self-Bias Network ............................................................................................. 105

10.6 Part 3 – Voltage-Divider-Bias Network ..................................................................... 106

10.7 Exercises ............................................................................................................................... 107

10.8 Assessment Sheet .............................................................................................................. 108

Lab - 11: Design of JFET Bias Circuits ................................................................................ 109

11.1 Objectives ............................................................................................................................. 109

11.2 Equipment Required ........................................................................................................ 109

11.3 Résumé of Theory.............................................................................................................. 109

11.4 Part 1 – Determining IDSS and VP .................................................................................. 109

11.5 Part 2 – Self-Bias Circuit Design................................................................................... 110

11.6 Part 3 – Voltage-Divider Circuit Design .................................................................... 113

11.7 Exercises ............................................................................................................................... 115

11.8 Assessment Sheet .............................................................................................................. 117

Lab - 12: Compound Configurations .................................................................................. 117

12.1 Objectives ............................................................................................................................. 118

12.2 Equipment Required ........................................................................................................ 118

12.3 Résumé of Theory.............................................................................................................. 118

12.4 Part 1 – Determining the BJT () and JFET (IDSS and VP) Parameters ........... 119

12.5 Part 2 – Capacitive-Coupled Multistage System with Voltage-Divider Bias 120

12.6 Part 3 – DC-Coupled Multistage Systems ................................................................. 121

12.7 Part 4 – A BJT-JFET Compound Configuration ....................................................... 122

EE231L – Electronics-I Lab Manual Page 5

12.8 Exercises ............................................................................................................................... 124

12.9 Assessment Sheet .............................................................................................................. 125

Lab - 13:Open Ended Lab…………………………………………………………………………………126

EE231L – Electronics-I Lab Manual Page 6

List of Figures

Figure 1-1: Silicon and Germanium Diode Characteristics ............................................................................ 9

Figure 1-2: AC resistance........................................................................................................................................ 100

Figure 1-3: Diode Testing: Forward Bias ............................................................................................................ 11

Figure 1-4: Forward bias diode characteristics ............................................................................................ 121

Figure 1-5: Plot diode characteristics ............................................................................................................... 122

Figure 1-6: Reverse bias diode characteristics ................................................................................................ 13

Figure 1-7 Forward-biased silicon diodes ..................................................................................................... 167

Figure 1-8: Firing voltage for silicon and germanium. ............................................................................... 177

Figure 1-9: Series configuration .......................................................................................................................... 177

Figure 1-10: Series configuration ....................................................................................................................... 187

Figure 1-11: Series combination of Si and Ge diodes ................................................................................. 188

Figure 1-12: Parallel Configuration....................................................................................................................... 20

Figure 1-13: Parallel Configuration.................................................................................................................... 209

Figure 1-14: Parallel Configuration.................................................................................................................... 209

Figure 1-15: Bridge Configuration...................................................................................................................... 210

Figure 2-1 Half-wave and Full-wave rectified signal .................................................................................. 232

Figure 2-2 Half-wave rectifiers ............................................................................................................................ 243

Figure 2-3: Sinusiodal Input (e)........................................................................................................................... 243

Figure 2-4: Sketch waveform ................................................................................................................................... 25

Figure 2-5: Sketch waveform ................................................................................................................................... 26

Figure 2-6: Half wave rectification ........................................................................................................................ 26

Figure 2-7 ...................................................................................................................................................................... 265

Figure 2-8: Sketch waveform ................................................................................................................................... 27

Figure 2-9: Half-wave rectification (continued) ........................................................................................... 286

Figure 2-10: Sketch waveform ................................................................................................................................ 28

Figure 2-11: Sketch waveform ................................................................................................................................ 28

Figure 2-12: Sketch waveform ................................................................................................................................ 29

Figure 2-13: Full wave rectification ...................................................................................................................... 29

Figure 2-14: Sketch waveform ................................................................................................................................ 30

Figure 2-15: Sketch waveform ................................................................................................................................ 30

Figure 2-16: Sketch waveform ................................................................................................................................ 31

Figure 2-17: Sketch waveform ................................................................................................................................ 31

Figure 3-1: Parallel Clippers .................................................................................................................................... 35

Figure 3-2: Sketch waveform ................................................................................................................................... 35

Figure 3-3: Sketch waveform ................................................................................................................................... 36

Figure 3-4: Sketch waveform ................................................................................................................................... 36

Figure 3-5: Sketch waveform ................................................................................................................................... 37

Figure 3-6: Prallel CLippers...................................................................................................................................... 38

Figure 3-7: Sketch waveform ................................................................................................................................... 38

Figure 3-8: Sketch waveform ................................................................................................................................... 39

Figure 3-9: Sketch waveform ...................................................................... ........................................................39

Error! Bookmark not defined.

Figure 3-10: Sketch waveform ............................................................................................................................39

Error! Bookmark not defined.

Figure 3-11: Series Clippers ..................................................................................................................................... 39

Figure 3-12: Sketch waveform ................................................................................................................................ 40

Figure 3-13: Sketch waveform ................................................................................................................................ 40

Figure 3-14: Sketch waveform ................................................................................................................................ 41

Figure 3-15: Sketch waveform ................................................................................................................................ 41

Figure 3-16 : Sketch waveform ..........................................................................................................................41

Error! Bookmark not defined.

Figure 3-17: Sketch waveform ................................................................... ........................................................42

Error! Bookmark not defined.

Figure 3-18: Clampers ............................................................................................................................................. 421

Figure 3-19: Sketch waveform ............................................................................................................................. 432

Figure 3-20: Sketch waveform ............................................................................................................................. 432

EE231L – Electronics-I Lab Manual Page 7

Figure 3-21 : Sketch waveform ............................................................................................................................ 443

Figure 3-22: Sketch waveform ............................................................................................................................. 443

Figure 3-23: Clampers with a DC battery ........................................................................................................ 454

Figure 3-24: Sketch waveform ............................................................................................................................. 454

Figure 3-25: Sketch waveform ............................................................................................................................. 465

Figure 3-26: Sketch waveform ............................................................................................................................. 475

Figure 3-27: Sketch waveform ............................................................................................................................. 476

Figure 3-28: Sketch waveform ............................................................................................................................. 486

Figure 3-29: Sketch waveform ............................................................................................................................. 487

Figure 3-30: Sketch waveform ............................................................................................................................. 498

Figure 3-31 Sketch waveform............................................................................................................................... 508

Figure 4-1: LED Characteristics ........................................................................................................................... 532

Figure 4-2: Sketch waveform ................................................................................................................................ 542

Figure 4-3: LED characteristics ............................................................................................................................ 543

Figure 4-4: Zener Diode Characteristics........................................................................................................... 554

Figure 4-5: Sketch waveform ................................................................................................................................ 564

Figure 4-6: Zener Diode .......................................................................................................................................... 565

Figure 4-7: Zener diode regulation..................................................................................................................... 575

Figure 4-8: Combining LED and Zener diode ................................................................................................. 586

Figure 5-1: Determination of the identities of BJT leads .............................................................................. 62

Figure 5-2: Circuit to determine the characteristics of a BJT. .................................................................... 64

Figure 5-3Characteristic curves from the experimental data of Part 2............................................... 642

Figure 6-1: Determining ......................................................................................................................................... 69

Figure 6-2: Voltage divider configuration .......................................................................................................... 71

Figure 7-1: Emitter bias configuration................................................................................................................. 76

Figure 7-2 Collector Feedback withour RE ......................................................................................................... 77

Figure 7-3 Collector feedback configuration with RE.................................................................................. 795

Figure 8-1: Collector feedback configuration.................................................................................................... 85

Figure 8-2: Emitter bias configuration................................................................................................................. 88

Figure 8-3: Voltage divider configuration .......................................................................................................... 90

Figure 9-1: Saturation current and pinch-off voltage .................................................................................... 96

Figure 9-2 Transfer characteristics: 2N4416 .................................................................................................... 97

Figure 9-3 Drain-current curve: 2N4416............................................................................................................ 98

Figure 9-4 Pinch-off voltage curve: 2N4416...................................................................................................... 99

Figure 9-5 Transconductance versus VGS of 2N4416. ................................................................................. 101

Figure 10-1 Fixed-bias circuit............................................................................................................................... 104

Figure 10-2: Sketch the waveform...................................................................................................................... 104

Figure 10-3: Self Bias Circuit ................................................................................................................................. 105

Figure 10-4: Voltage-divider-bias circuit........................................................................................................ 106

Figure 11-1: Network to determine IDSS and VP. ........................................................................................... 110

Figure 11-2Figure 2 Self-bias configuration to be designed. ................................................................... 110

Figure 11-3 Transfer characteristic for the 2N4416 JFET. ....................................................................... 111

Figure 11-4 Voltage-divider configuration to be designed....................................................................... 113

Figure 12-1 Determining ..................................................................................................................................... 119

Figure 12-2 Determining IDSS and VP. ................................................................................................................. 120

Figure 12-3 AC-coupled multistage amplifier. ............................................................................................... 121

Figure 12-4 DC-coupled multistage amplifier................................................................................................ 122

Figure 12-5 BJT-JFET compound configuration............................................................................................ 123

EE231L – Electronics-I Lab Manual Page 8

Lab 1: Diode Characteristics and Configuration

Objectives:

• To calculate, compare, draw, and measure the characteristics of silicon and

germanium diodes.

• To analyze networks with diodes in a series or parallel configuration

• To calculate and measure the circuit voltages of various diode circuits

Equipment Required

Instruments DMM

Resistors: 1k, 1m

Components

Diodes: Si, Ge

Supplies : DC Power Supply

Résumé of Theory

Most modern-day digital multimeters can be used to determine the operating condition of a

diode. They have a scale denoted by a diode symbol that indicates the condition of a diode in

the forward- and reverse-bias regions. If connected to establish a forward-bias condition, the

meter will display the forward voltage across the diode at a current level typically about 2 mA.

If connected to establish a reverse-bias condition, an “OL” should appear on the display to

support the open-circuit approximation frequently applied to this region. If the meter does not

have the diode checking capability, the condition of the diode can also be checked by obtaining

some measure of the resistance level in the forward and reverse bias regions. Both techniques

for checking a diode will be introduced in the first part of the experiment.

Figure 0-1: Silicon and Germanium Diode Characteristics

The current–volt characteristics of a silicon or germanium diode have the general shape shown

in Fig. 1.1. Note the change in scale for both the vertical and horizontal axes. In the reverse-

biased region the reverse saturation currents are constant from 0 V to the Zener potential. In

EE231L – Electronics-I Lab Manual Page 9

the forward-bias region the current increases quite rapidly with increasing diode voltage. Note

that the curves are rising almost vertically at a forward-biased voltage of less than 1 V. The

forward-biased diode current will be limited solely by the network in which the diode is

connected or by the maximum current or power rating of the diode.

The firing or threshold voltage is determined by extending a straight line tangent to the curves

until it hits the horizontal axis. The intersection with the VD axis will determine the threshold

voltage VT at which the current begins to rise rapidly.

Figure 0-2: AC resistance

The DC or static resistance of a diode at any point on the characteristics is determined by the

ratio of the diode voltage at that point, divided by the diode current. That is,

𝑉𝐷

𝑅𝐷𝐶 =

𝐼𝐷

The AC resistance at a particular diode current or voltage can be determined using a tangent

line drawn as shown in Fig. 1.2. The resulting voltage (V) and current (I) deviations can

then be used to find AC resistance as follows:

∆𝑉

𝑟𝑑 =

∆𝐼

The application of differential calculus shows that the AC resistance of a diode in the vertical-

rise section of the characteristics is given by

26𝑚𝑉

𝑟𝑑 =

𝐼𝐷

For levels of current at and below the knee of the curve, the AC resistance of a silicon diode

is better approximated by

26𝑚𝑉

𝑟𝑑 = 2 ( )

𝐼𝐷

Part 1 – Diode Test

a) The diode-testing scale of a DMM can be used to determine operating condition of a diode.

With one polarity, DMM should provide the “firing potential” of diode, while the reverse

connection should result in an “OL” response to support open-circuit approximation.

b) Using the connections shown in Fig. 1.3, the constant-current source of about 2 mA

internal to the meter will forward bias the junction, and a voltage of about 0.7 V will be

EE231L – Electronics-I Lab Manual Page 10

obtained for silicon and 0.3 V (300 mV) for germanium. If leads are reversed, you’ll see

OL.

Figure 0-3: Diode Testing: Forward Bias

c) If a low reading (less than 1 V) is obtained in both directions, the junction is shorted

internally. If an OL indication is obtained in both directions, the junction is open. Perform

the tests for silicon and germanium diodes and record your readings below:

Test Si Ge

Forward

Reverse

d) Based on the results, are both diodes in good condition?

Resistance Scales

As indicated in the theory section of this experiment, the condition of a diode can also be

checked using the resistance scales of a volt ohm meter (VOM) or digital meter. Using the

appropriate scales of the VOM or DMM, determine the resistance levels of the forward and

reverse bias regions of the Si and Ge diodes. Enter the results in following table:

Test Si Ge Meter

Forward VOM

Reverse DMM

Although the firing potential is not revealed using the resistance scales, a “good” diode will

result in a lower resistance level in the forward bias state and a much higher resistance level

when reverse-biased. Based on the results, are both diodes in good condition?

Part 2 – Forward Bias Diode Characteristics

a) In this part of the experiment we will obtain sufficient data to plot the forward-bias

characteristics of the silicon and germanium diodes. Construct the network of Fig 1. 4 with

the supply (E) set at 0 V. Record the measured value of the resistor.

EE231L – Electronics-I Lab Manual Page 11

+ VR -

+

R = 1 kΩ

Supply (E)

DC Power

VD

Si

ID

-

Figure 0-4: Forward bias diode characteristics

b) Increase the supply voltage E until VR (not E) reads 0.1 V. Then measure VD and insert its

voltage in following table. Calculate the value of corresponding current ID:

𝐈𝐃 = 𝐕𝐑 ⁄𝐑 𝐦𝐞𝐚𝐬

VR (V) 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 2 3 4 5 6 7 8 9 10

VD (V)

𝐈𝐃 (mA)

c) Replace the silicon diode by a germanium diode and complete the table below:

VR (V) 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 2 3 4 5 6 7 8 9 10

VD (V)

𝐈𝐃 (mA)

d)

On Fig. 1.5, plot ID versus VD for the silicon and germanium diodes. Complete the curves

by extending the lower region of each curve to the intersection of the axis at 𝐼𝐷 = 0 𝑚𝐴

and 𝑉𝐷 = 0 𝑉. Label each curve and clearly indicate data points. Be neat!

Figure 0-5: Plot diode characteristics

e) How do the two curves differ? What are their similarities?

EE231L – Electronics-I Lab Manual Page 12

Part 3 – Reverse Bias Diode Characteristics

a) In Fig. 1.6, a reverse-biased condition has been established. Since the reverse saturation

current will be relatively small, a large resistance of 1 M is required if the voltage across

R is to be of measurable amplitude. Construct the circuit of Fig. 1.6 and record the

measured value of R.

- VR +

R = 1 MΩ

- VD +

Si

E 20 V

IS

Figure 0-6: Reverse bias diode characteristics

b) Measure the voltage VR. Calculate the reverse saturation current from

𝑉𝑅

𝐼𝑆 =

𝑅𝑚𝑒𝑎𝑠 ||𝑅𝑚

The internal resistance (Rm) of the DMM is included because of the large magnitude of the

resistance R. Your instructor will provide the internal resistance of the DMM for your

calculations. If unavailable, use a typical value of 10 M.

RM =_____________

VR (measured) =_____________

IS (calculated) =_____________

c) Repeat Part 3(b) for the germanium diode.

VR (measured) =_____________

IS (calculated) =_____________

d) How do the resulting levels of IS for silicon and germanium compare?

e) Determine the DC resistance levels for the silicon and germanium diodes using the

equation given below:

𝑉𝐷 𝑉𝐷 𝐸 − 𝑉𝑅

𝑅𝐷𝐶 = = =

𝐼𝐷 𝐼𝑆 𝐼𝑆

RDC (calculated) (Si) =____________

RDC (calculated) (Ge) =____________

f) Are the resistance levels sufficiently high to be considered open circuit equivalents if

appearing in series with resistors in the low kΩ range?

Part 4 – DC Resistance

a) Using the Si curve of Fig. 1.5, determine the diode voltage at the diode current levels

indicated in the table below. Then determine the DC resistance at each current level. Show

all calculations.

EE231L – Electronics-I Lab Manual Page 13

ID (mA) VD (V) RDC (Ω)

0.2

1

5

10

b) Repeat Part (a) for germanium and complete the following table

ID (mA) VD (V) RDC (Ω)

0.2

1

5

10

c) Does the resistance (for Si and Ge) change as the diode current increases and we move up

the vertical-rise section of the characteristics?

Part 5 – AC Resistance

a) Using the equation 𝑟𝑑 = 𝑉/𝐼 (Eq. 2), determine the AC resistance of the silicon diode

at 𝐼𝐷 = 9 𝑚𝐴 using the curve of Fig. 1.5. Show all work.

b) Determine the AC resistance at 𝐼𝐷 = 9 𝑚𝐴 using the equation 𝑟𝑑 = 26 𝑚𝑉/𝐼𝐷 (𝑚𝐴) for

the silicon diode. Show all work.

rd (calculated) =__________

c) How do the results of Parts 5(a) and 5(b) compare?

d) Repeat Part 5 a) for ID = 2 mA for the Si diode.

rd (calculated) =___________

e) Repeat Part 5 b) for ID = 2 mA for the Si diode.

rd (calculated) =___________

f) How do the results of Parts 5(d) and 5(e) compare?

EE231L – Electronics-I Lab Manual Page 14

Part 6 – Firing Potential

Graphically determine the firing potential (threshold voltage) of each diode from its

characteristics as defined in theory. Show the straight-line approximations on Fig. 1.5.

VT (silicon) =___________

VT (germanium) =___________

Questions

a) Compare the characteristics of silicon and germanium in the forward- and reverse-bias

regions. In particular, which diode is closer to the short-circuit approximation in the

forward-bias region and which is closer to the open-circuit approximation in the reverse-

bias region? How are they similar and what are their most noticeable differences?

b) Research the effect of heat on the terminal resistance of semiconductor materials and

briefly review why the terminal resistance will decrease with the application of heat.

EE231L – Electronics-I Lab Manual Page 15

1.9 Diode Configurations

Résumé of Theory

The analysis of circuits with diodes and a DC input requires that the state of the diodes first

be determined. For silicon diodes (with a transition voltage or “firing potential” of 0.7 V), the

voltage across the diode must be at least 0.7 V with the polarity appearing in Fig. 1.7 for the

diode to be in the “on” state. Once the voltage across the diode reaches 0.7 V the diode will

turn “on” and have the electrical equivalent of Fig. 1.7. For VD < 0.7 V or for voltages with

the opposite polarity of Fig. 1.7, the diode can be approximated as an open circuit. For

germanium diodes, replace the transition voltage by the germanium value of 0.3 V.

In most networks where the applied DC voltage exceeds the transition voltage of the diodes,

the state of the diode can usually be determined simply by mentally replacing the diode by a

resistor and determining the direction of current through the resistor. If the direction matches

the arrowhead of the diode symbol, the diode is in the “on” state, and if the opposite, it is in

the “off” state. Once the state is determined, simply replace the diode by the transition voltage

or open circuit and analyze the rest of the network.

ID

0.7 V

+ VD > 0.7 -

0 0.7

VD

(a) (b)

Figure 1-7 Forward-biased silicon diodes

Be alert to the location of the output voltage VO = VR = IRR. This is particularly helpful in

situations where a diode is in an open-circuit condition and the current is zero. For IR = 0, VO

= VR = IRR = 0(R) = 0 V. In addition, an open circuit can have a voltage across it, but the

current is zero. Further, a short circuit has a zero-volt drop across it, but the current I limited

only by the external network or limitations of the diode.

The analysis of logic gates requires that one make an assumption about the state of the diodes,

determine the various voltage levels, and then determine whether the results violate any basic

laws, such as that a point in a network (such as VO) can have only one voltage level. It is

usually helpful to keep in mind that there must be a forward-bias voltage across a diode equal

to the transition voltage to turn it “on.” Once VO is determined and no laws are violated with

the diodes in their assumed state, a solution to the configuration can be assumed.

EE231L – Electronics-I Lab Manual Page 16

Part 1 – Threshold Voltage

For both the silicon and the germanium diode, determine the threshold using the diode-

checking capability of the DMM or a curve tracer. For this experiment, the “firing voltages”

obtained will establish the equivalent characteristics for each diode appearing in Fig. 1.8.

Record the value of VT obtained for each diode in Fig. 1.8. If the diode-checking capability or

curve tracer is unavailable, assume VT = 0.7 V for silicon and VT = 0.3 V for germanium.

ID ID

Si Ge

VD VD

0 0

VT = ---------- VT = ----------

Figure 1-8: Firing voltage for silicon and germanium.

Part 2 – Series Configuration

a) Construct the circuit of Fig. 1.9. Record the measured value of R.

+ VD -

ID

+

Si

VO

R 2.2 kΩ

E 5V

-

Rmeas = --------

Figure 1-9: Series configuration

b) Using the firing voltages of the Si and Ge diodes as measured in Part 1 and the measured

resistance for R, calculate the theoretical values of VO and ID. Insert the level of VT for VD.

VD=________________________

VO (calculated) =___________________

ID (calculated) =____________________

c) Measure the voltages VD and VO, using the DMM. Calculate the current ID from measured

values. Compare with the results of Part (B).

VD (measured)=________________________

VO (measured) =___________________

ID (from measured) = VO/R = ____________________

d) Construct the circuit of Fig. 1.10. Record the measured values for each resistor.

EE231L – Electronics-I Lab Manual Page 17

R1 + VD -

ID

+

2.2 kΩ Si

VO

R2 1 kΩ

E 5V

-

R1 meas = -------- R2 meas = --------

Figure 1-10: Series configuration

e) Using the measured values of VD and VO from Part 1 and the measured resistance values

for R1 and R2, calculate the theoretical values of VO and ID. Insert the level of VT for VD.

VD=________________________

VO (calculated) =___________________

ID (calculated) =____________________

f) Measure the voltages VD and VO, using the DMM. Calculate the current ID from measured

values. Compare with the results of step 2(e).

VD (measured)=________________________

VO (measured) =___________________

ID (from measured)= VO/R2 = ____________________

g) Reverse the silicon diode in Fig. 2.4 and calculate theoretical values of VD, VO, and ID.

VD=________________________

VO (calculated) =___________________

ID (calculated) =____________________

h) Measure VD and VO for the conditions of Part 2(g). Calculate the current ID from measured

values. Compare with the results of Part 2(g).

VD (measured)=________________________

VO (measured) =___________________

ID (from measured) = VO/R2 = ____________________

i) Construct the network of Fig. 1.11. Record the measured value of R.

+ V1 -

VO

ID

Si Ge

R 2.2 kΩ

E 5V

Rmeas = --------

Figure 1-11: Series combination of Si and Ge diodes

j) Using the firing voltages of the silicon and germanium diodes as measured in Part 1,

calculate the theoretical values of V1 (across both diodes), Vo, and ID.

V1=________________________

EE231L – Electronics-I Lab Manual Page 18

VO (calculated) =___________________

ID (calculated) =____________________

k) Measure V1 and Vo, and compare to the results of Part 2(j). Calculate the current ID from

measured values and compare to the level of Part 2(j).

V1 (measured)=________________________

VO (measured) =___________________

ID (from measured) = VO/R2 = ____________________

EE231L – Electronics-I Lab Manual Page 19

Part 3 – Parallel Configuration

a) Construct the network of Fig. 1.12. Record the measured value of R.

+ VR - Rmeas = --------

+

R = 2.2 kΩ

VO

Si Ge

E 5V

-

Figure 1-12: Parallel Configuration

b) Using the firing voltages of the silicon and germanium diodes as measured in Part 1,

calculate the theoretical values of VO and VR.

VO (calculated) =_________________

VR (calculated) =_________________

c) Measure VO and VR and compare with the results of Part 3(b).

VO (measured) =_________________

VR (measured) =_________________

d) Construct the network of Fig.1. 13. Record the measured value of each resistor.

+ VR1 -

R1 = 2.2 kΩ +

VO

Si R2 1 kΩ

E 5V

-

R1 meas = -------- R2 meas = --------

Figure 1-13: Parallel Configuration

e) Using the firing voltages of the silicon diode as measured in Part 1, calculate the theoretical

values of VO, VR1, and ID.

VO(calculated) =__________

VR1 (calculated) =__________

ID (calculated) =__________

f) Measure VO and VR1. Using the measured values of VO and VR1, calculate IR2 and IR1 and

determine ID. Compare to the results of Part 3(e).

VO (measured) =__________

VR1 (measured) =__________

ID (from measured) =__________

g) Construct the network of Fig. 1.14. Record the measured value of the resistor.

+ VR - Rmeas = --------

+

R = 2.2 kΩ

VO

Si Ge

E 5V

-

Figure 1-14: Parallel Configuration

EE231L – Electronics-I Lab Manual Page 20

h) Using the firing voltages of the silicon and germanium diodes as measured in Part 1,

calculate the theoretical values of VO and VR.

VO (calculated) =_________________

VR (calculated) =_________________

i) Measure VO and VR and compare with the results of Part 3(h).

VO (measured) =_________________

VR (measured) =_________________

Part 4 – Bridge Configuration

a) Construct the network of Fig. 1.15. Record the measured value of each resistor.

Si Si

R1 = 1kΩ

E 5V

- Vo +

R2 = 2.2kΩ

R1 meas = --------

R2 meas = --------

R3 meas = --------

Figure 1-15: Bridge Configuration

b) Using the VT for both diodes as measured in Part 1, calculate theoretical value of VO and

VR3.

VO (calculated) =___________

VR3 (calculated) =___________

c) Measure VO and VR3 and compare to the results of Part 5(b). Use a low voltage scale when

measuring VO.

VO (measured) =____________

VR3 (measured) =____________

d) If the diode in the top right branch of Fig. 2.9 was damaged, creating an internal open

circuit, calculate the resulting levels of VO and VR3.

VO (calculated) =___________

VR3 (calculated) =___________

e) Remove the top right diode from Fig. 2.9 and measure VO and VR3. Compare the results

with those predicted in Part 6(a).

VO (measured) =___________

VR3 (measured) =___________

EE231L – Electronics-I Lab Manual Page 21

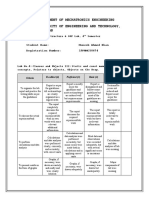

Assessment Sheet

Student Name: ______________________ Reg. #: _________________

Score

PLOs Poor Satisfactory Good Excellent

CLOs

0 0.5-1.0 1.5-2.0 2.5-3.0

Can

Can setup and Can setup and

independently

Cannot setup or handle the handle the

CLO-1 PLO-5 setup, operate

handle the apparatus apparatus with apparatus with

and handle the

some help minimal help

apparatus

Data recorded

Data recorded

and presented is All required

and presented is

complete, but data is recorded

Data recorded only partially

accuracy is not and presented

with considerable complete. The

CLO-2 PLO-5 as per accurately and

assistance from required format

requirement. completely in

instructor is followed but

The required the required

with few

format is format

deficiencies

followed

Analyzes data

Analyzes and

correctly

Unable to analyze interprets data Analyzes and

however unable interprets data

and interpret data correctly for

CLO-3 to interpret it for correctly for all

PLO-4 for any tasks/ few tasks/

tasks/ tasks/

experiments in the experiments in

experiments in experiments in

lab the lab the lab

the lab

Student hands

Student does not over the

CLO-4 hand over the workstation in

PLO-8 the required NA

workstation in the

manner NA

required manner

Total Score in Lab /10

Instructor Signature: _________________

Date: _________________

EE231L – Electronics-I Lab Manual Page 22

Lab-2: Half wave and Full wave Rectifiers

2.1 Objective

To calculate, draw, and measure DC output voltages of half-wave and full-wave rectifier

circuits.

2.2 Equipment Required

Instruments Oscilloscope, DMM

Resistors: 2.2 k, 3.3 k

Components Diodes: Si

Supplies: Function Generator

Miscellaneous: 12.6-V center-tapped

transformer with fused line cord

2.3 Résumé of Theory

The primary function of half-wave and full-wave rectification systems is to establish a DC

level from a sinusoidal input signal that has zero average (DC) level. The half-wave voltage

signal of Fig. 3.1, normally established by a network with a single diode, has an average or

equivalent DC voltage level equal to 31.8% of the peak voltage Vm. That is,

𝑽𝑫𝑪 = 𝟎. 𝟑𝟏𝟖 𝑽𝒑𝒆𝒂𝒌 𝑽𝒐𝒍𝒕𝒔

The full wave rectified signal of Fig. 3.1 has twice the average or DC level of the half-wave

signal, or 63.6% of the peak value Vm. That is,

𝑽𝑫𝑪 = 𝟎. 𝟔𝟑𝟔 𝑽𝒑𝒆𝒂𝒌 𝑽𝒐𝒍𝒕𝒔

For large sinusoidal inputs (Vm>> VT) the forward-biased transition voltage VT of a diode can

be ignored. However, for situations when the peak value of the sinusoidal signal is not that

much greater than VT, VT can have a noticeable effect on VDC.

Figure 2-1 Half-wave and Full-wave rectified signal

In rectification systems the peak inverse voltage (PIV) must be considered carefully. The PIV

voltage is the maximum reverse-bias voltage that a diode can handle before entering the Zener

breakdown region. For typical single-diode half-wave rectification systems, the required PIV

level is equal to the peak value of the applied sinusoidal signal. For the four-diode full wave

bridge rectification system, the required PIV level is again the peak value, but for a two-diode

center-tapped configuration, it is twice the peak value of the applied signal.

EE231L – Electronics-I Lab Manual Page 23

Part 1 – Threshold Voltage

Choose one of the four silicon diodes and determine the threshold voltage, VT, using the diode-

checking capability of the DMM or a curve tracer.

VT =______________

2.4 Part 2 – Half-Wave Rectification

a) Construct the circuit of Fig. 2.2 using Si diode. Record the measured value of the resistance

R. Set the function generator to a 1000-Hz 8-Vp-p sinusoidal voltage using the

oscilloscope.

+ Vd -

+

Si

+

VO

e = 4 sin(wt)

f = 1000 Hz

R 2.2 kΩ

-

-

Rmeas = --------

Figure 2-2 Half-wave rectifiers

b) The sinusoidal input (e) of Fig. 2.2 has been plotted on the screen of Fig. 3.3 Determine

the chosen vertical and horizontal sensitivities. Note that the horizontal axis is the 0 V line.

Figure 2-3: Sinusoidal Input (e)

Vertical sensitivity =___________ Horizontal sensitivity =__________

c) Using the threshold voltage VT from previous section, determine the theoretical output

voltage VO for the circuit of Fig. 3.2 and sketch the waveform on Fig. 3.3 for one full cycle

using the same sensitivities employed in Part (B). Indicate the maximum and minimum

values on the output waveform.

d) Using the oscilloscope with AC-GND-DC coupling switch in DC position, obtain the

voltage VO and sketch the waveform on Fig. 3.4. Before viewing VO be sure to set the VO

= 0 V line using the GND position of the coupling switch. Use the same sensitivities as in

Part (B).

EE231L – Electronics-I Lab Manual Page 24

Figure 2-4: Sketch waveform

e) How do the results of Parts 2(c) and 2(d) compare?

f) Calculate the DC level of the half-wave rectified signal of Part 2(d) using Eq. 1.

VDC (calculated) =______________

g) Measure DC level of VO using DC scale of the DMM and find the percent difference

between the measured value and the calculated value of Part 2(e) using the following

equation:

𝑉𝐷𝐶(𝑐𝑎𝑙𝑐) − 𝑉𝐷𝐶(𝑚𝑒𝑎𝑠)

% 𝐷𝑖𝑓𝑓𝑒𝑟𝑒𝑛𝑐𝑒 = | | ∗ 100%

𝑉𝐷𝐶(𝑐𝑎𝑙𝑐)

VDC (measured) =_______________

% Difference =_______________

h) Switch the AC-GND-DC coupling switch to the AC position. What is the effect on the

output signal VO? Does it appear that the area under the curve above the zero axis equals

the area under the curve below the zero axis? Discuss the effect of the AC position on

waveforms that have an average value over one full cycle.

i) Reverse the diode of Fig. 2.2 and sketch the output waveform obtained using the

oscilloscope on Fig. 2.5. Be sure the coupling switch is in the DC position and the VO = 0

V line is preset using the GND position. Include the maximum and minimum voltage

levels on the plot as determined using the chosen vertical sensitivity.

EE231L – Electronics-I Lab Manual Page 25

Figure 2-5: Sketch waveform

j) Calculate and measure the DC level of the resulting waveform of Fig. 2.5. Insert the proper

sign for the polarity of VDC as defined by Fig. 2.2 using Eq.1.

VDC (calculated) =___________

VDC (measured) =___________

2.5 Part 3 – Half-Wave Rectification (continued)

a) Construct the network of Fig. 2.6. Record the measured value of the resistor R.

+

R = 2.2 kΩ

+

VO

e = 4 sin(wt)

f = 1000 Hz Si

-

-

Rmeas = --------

Figure 2-6: Half wave rectification

b) Using the threshold voltage of Part 1, determine the theoretical output voltage VO for Fig.

2.6 and sketch the waveform on Fig. 2.7 for one full cycle using the same sensitivities

employed in Part 2(b). Indicate maximum and minimum values on the output waveform.

Figure 2-6

EE231L – Electronics-I Lab Manual Page 26

c) Using the oscilloscope with the coupling switch in the DC position, obtain the voltage VO

and sketch the waveform on Fig. 2.8. Before viewing VO be sure to set the VO = 0 V line

using the GND position of the coupling switch. Use the same sensitivities as in Part 3(b).

Figure 2-7: Sketch waveform

d) How do the results of Parts 3(b) and 3(c) compare?

e) What is the most noticeable difference between the waveform of Fig. 2.8 and that obtained

in Part 2(h)? Why did the difference occur?

f) Calculate the DC level of the waveform of Fig. 2.8 using the following equation:

𝑇𝑜𝑡𝑎𝑙 𝐴𝑟𝑒𝑎 2𝑉𝑚 − (𝑉𝑇 )𝜋 𝑉𝑇

𝑉𝐷𝐶 = ≅ = 0.318𝑉𝑚 − 𝑉𝑜𝑙𝑡𝑠

2𝜋 2𝜋 2

VDC (calculated) =______________

g) Measure the output DC voltage with the DC scale of the DMM and calculate the percent

difference using the same equation appearing in Part 2(f).

VDC (measured) =______________

(% Difference) =______________

2.6 Part 4 – Half-Wave Rectification (continued)

a) Construct the network of Fig. 2.9. Record the measured value of each resistor.

EE231L – Electronics-I Lab Manual Page 27

R1

+

2.2 kΩ

+

VO

e = 4 sin(wt) R2 2.2 kΩ

f = 1000 Hz Si

-

-

R1 meas = --------

R2 meas = --------

Figure 2-8: Half-wave rectification (continued)

b) Using the measured resistor values and VT from Part 1, forecast the appearance of the

output waveform VO and sketch the result on Fig. 2.10. Use the same sensitivities

employed in Part 2(b) and insert the maximum and minimum values of the waveform.

Figure 2-9: Sketch waveform

c) Using the oscilloscope with the coupling switch in the DC position, obtain the waveform

for VO and record on Fig. 2.11. Again, be sure to preset the VO = 0 V line using the GND

position of the coupling switch before viewing the waveform. Using the chosen

sensitivities, determine the maximum and minimum values and place on the sketch of Fig.

2.11.

Figure 2-10: Sketch waveform

d) Are the waveforms of Figs. 2.10 and 2.11 relatively close in appearance and magnitude?

EE231L – Electronics-I Lab Manual Page 28

e) Reverse the direction of the diode and record the resulting waveform on Fig. 2.12 as

obtained using the oscilloscope.

Figure 2-11: Sketch waveform

f) Compare the results of Figs. 2.11 and 2.12. What are the major differences and why?

2.7 Part 5 – Full-Wave Rectification (Bridge Configuration)

a) Construct the full-wave bridge rectifier of Fig. 2.13. Be sure that the diodes are inserted

correctly and that the grounding is as shown. If unsure, ask your instructor to check your

setup. Record the measured value of the resistor R.

Figure 2-12: Full wave rectification

In addition, measure the rms voltage at the transformer secondary using the DMM set to

AC. Record that rms value below. Does it differ from the rated 12.6 V?

Vrms (measured) =____________

b) Calculate the peak value of the secondary voltage using the measured value (Vpeak =

1.414Vrms).

Vpeak (calculated) =______________

EE231L – Electronics-I Lab Manual Page 29

c) Using the VT of Part 1 for each diode, sketch the expected output waveform VO on Fig.

2.14. Choose a vertical and a horizontal sensitivity based on the amplitude of the secondary

voltage. Consult your oscilloscope to obtain a list of possible sensitivities. Record your

choice for each below.

Figure 2-13: Sketch waveform

Vertical sensitivity =_____________ Horizontal sensitivity =_____________

d) Using the oscilloscope with the coupling switch in the DC position, obtain the waveform

for VO and record on Fig 2.15. Use the same sensitivities employed in Part 5(c) and be

sure to preset the VO = 0 V line using the GND position of the coupling switch. Label the

maximum and minimum values of the waveform using the chosen vertical sensitivity.

Figure 2-14: Sketch waveform

e) How do the waveforms of Parts 5(c) and 5(d) compare?

f) Determine the DC level of the full-wave rectified waveform of Fig. 2.15

VDC (calculated) =_____________

EE231L – Electronics-I Lab Manual Page 30

g) Measure the DC level of the output waveform using the DMM and calculate the percent

difference between the measured and calculated values.

VDC (measured) =____________

(% Difference) =____________

h) Replace diodes D3 and D4 by 2.2 k resistors and forecast the appearance of the output

voltage VO including the effects of VT for each diode. Sketch the waveform on Fig. 2.16

and label the magnitude of the maximum and minimum values. Record your choice of

sensitivities below.

Figure 2-15: Sketch waveform

Vertical sensitivity =___________ Horizontal sensitivity =___________

i) Using the oscilloscope, obtain the waveform for VO and reproduce it on Fig. 2.17,

indicating the maximum and minimum values. Use the same sensitivities as determined in

Part 5(g).

Figure 2-16: Sketch waveform

j) How do the waveforms of Figs. 2.16 and 2.17 compare?

EE231L – Electronics-I Lab Manual Page 31

k) Calculate the DC level of the waveform of Fig. 2.17.

VDC (calculated) =_____________

l) Measure the DC level of the output voltage using the DMM and calculate the percent

difference.

VDC (measured) =_____________

(% Difference) =_____________

m) What was the major effect of replacing the two diodes with resistors?

EE231L – Electronics-I Lab Manual Page 32

2.8 Assessment Sheet

Student Name: ______________________ Reg. #: _________________

Score

PLOs Poor Satisfactory Good Excellent

CLOs

0 0.5-1.0 1.5-2.0 2.5-3.0

Can

Can setup and Can setup and

independently

Cannot setup or handle the handle the

CLO-1 PLO-5 setup, operate

handle the apparatus apparatus with apparatus with

and handle the

some help minimal help

apparatus

Data recorded

Data recorded

and presented is All required

and presented is

complete, but data is recorded

Data recorded only partially

accuracy is not and presented

with considerable complete. The

CLO-2 PLO-5 as per accurately and

assistance from required format

requirement. completely in

instructor is followed but

The required the required

with few

format is format

deficiencies

followed

Analyzes data

Analyzes and

correctly

Unable to analyze interprets data Analyzes and

however unable interprets data

and interpret data correctly for

CLO-3 to interpret it for correctly for all

PLO-4 for any tasks/ few tasks/

tasks/ tasks/

experiments in the experiments in

experiments in experiments in

lab the lab the lab

the lab

Student hands

Student does not over the

CLO-4 hand over the workstation in

PLO-8 the required NA

workstation in the

manner NA

required manner

Total Score in Lab /10

Instructor Signature: _________________

Date: _________________

EE231L – Electronics-I Lab Manual Page 33

Lab 3: Clipping Circuits

3.1 Objective

• To calculate, draw, and measure output voltages of series and parallel clipping circuits.

• To calculate, draw, and measure the output voltage of clampers.

3.2 Equipment Required

Instruments Oscilloscope, DMM

Resistors: 2.2 k, 3.3 k

Components Diodes: Si

Supplies: Function Generator,

1.5-V D cell and holder

3.3 Résumé of Theory

The primary function of clippers is to “clip” away a portion of an applied alternating signal.

The process is typically performed by a resistor-diode combination. DC batteries are used to

provide additional shifts or “cuts” of applied voltage. The analysis of clippers with square-

wave inputs is the easiest to perform since there are only two levels of input voltage. Each

level can be treated as a DC input and the output voltage for corresponding time interval

determined. For sinusoidal and triangular inputs, various instantaneous values can be treated

as DC levels and the output level determined. Once a sufficient number of plot points for the

output voltage VO has been determined, it can be sketched in total. Once the behavior of

clippers is established, the effect of the placement of elements in various positions can be

predicted and the analysis completed.

Part 1 – Threshold Voltage

Determine the threshold voltage for the silicon and germanium diodes using the diode-

checking capability of the DMM or a curve tracer. Round off to the hundredths place when

recording in the designated space below. If the diode checking capability or curve tracer is

unavailable, assume VT = 0.7 V for the silicon diode and 0.3 V for the germanium diode.

VT (Si) =____________

VT (Ge) =____________

Part 2 – Parallel Clippers

a) Construct the clipping network of Fig. 3.1. Record the measured resistance value and

voltage of the D cell. Note that the input is an 8 Vp-p sine wave at a frequency of 1000

Hz.

EE231L – Electronics-I Lab Manual Page 34

Figure 3-1: Parallel Clippers

b) Using the measured values of R, E, and VT, calculate the voltage VO when the applied sine

wave is +4 V. What is the level of VO? Show all the steps of your calculations to determine

VO.

VO (calculated) =_____________

c) Repeat Part 2(b) when the applied sine wave is –4 V.

VO (calculated) =____________

d) Using the results of Parts 2(b) and 2(c), sketch the expected waveform for VO using the

horizontal axis of Fig. 3.2 as the VO = 0 V line. Use a vertical sensitivity of 1 V/cm and a

horizontal sensitivity of 0.2 ms/cm. Sketch of VO from calculated results:

Figure 3-2: Sketch waveform

e) Using the sensitivities settings provided in Part 2(d), set the input sine wave and record VO

on Fig. 3.3 using the oscilloscope. Be sure to preset the VO = 0 V line using the GND

position of the coupling switch (and the DC position to view the waveform).

Sketch of VO from measured results:

EE231L – Electronics-I Lab Manual Page 35

Figure 3-3: Sketch waveform

f) How does the waveform of Fig. 3.3 compare with the predicted result of Fig. 3.2?

g) Reverse the battery of Fig. 3.1 and, using the measured values of R, E, and VT, calculate

the level of VO for the time interval when Vi = +4 V.

VO (calculated) =____________

h) Repeat Part 2(f) for the time interval when Vi = –4 V.

VO (calculated) =____________

i) Using the results of Parts 2(f) and 2(g), sketch the expected waveform for VO using the

horizontal axis of Fig. 3.4 as the VO = 0 V line. Use the same sensitivities provided in Part

2(d). Sketch of VO From calculated results:

Figure 3-4: Sketch waveform

EE231L – Electronics-I Lab Manual Page 36

j) Set the input sine wave and record VO on Fig. 3.5 using the oscilloscope. Be sure to preset

the VO = 0 V line using the GND position of the coupling switch (and the DC position to

view the waveform). Sketch of VO from measured results:

Figure 3-5: Sketch waveform

k) How does the waveform of 3.4 compare with the predicted result of Fig. 3.5?

EE231L – Electronics-I Lab Manual Page 37

Part 3 – Parallel Clippers (continued)

a) Construct the network of Fig. 3.6. Record the measured value of the resistance. Note that

the input is now a 4 Vp-p square wave at f = 1000 Hz.

+ VR - Rmeas = --------

+

R1 = 2.2 kΩ

VO

+ Si

4V p-p square wave Ge

f = 1000 Hz

-

-

Figure 3-6: Parallel Clippers

b) Using the levels of VT determined in Part 1, calculate the level of VO for the time interval

when Vi = +2 V.

VO (calculated) =__________

c) Repeat Part 3(b) for the time interval when Vi = –2 V.

VO (calculated) =_____________

d) Using the results of Parts 3(b) and 3(c), sketch the expected waveform for VO using the

horizontal axis of Fig. 3.7 as the VO = 0 V line. Insert your chosen vertical and horizontal

sensitivities below.

Vertical sensitivity =__________

Horizontal sensitivity =__________

Sketch of VO from calculated results:

Figure 3-7: Sketch waveform

e) Using the sensitivity settings chosen in Part 3(d), set the input square wave and record VO

on Fig. 3.8 using the oscilloscope. Be sure to preset the VO = 0 V line using the GND

position of the coupling switch (and the DC position to view the waveform).

EE231L – Electronics-I Lab Manual Page 38

f) Sketch of VO from measured results:

Figure 3-8: Sketch waveform

g) How does the waveform of Fig. 3.8 compare with the predicted result of Fig. 3.7?

Part 4 – Series Clippers

a) Construct the circuit of Fig. 3.11. Record the measured resistance value and the DC level

of the D cell. The applied signal is an 8 Vp-p square wave at a frequency of 1000 Hz.

Si E

+

+ 1.5V

8V p-p square wave

VO

f = 1000 Hz R 2.2 kΩ

T = 1ms -

-

Rmeas = --------

Emeas = --------

Figure 3-9: Series Clippers

b) Using the measured values of R, E, and VT, calculate the voltage VO for the time interval

when Vi = +4 V.

VO (calculated) =_____________

c) Repeat Part 5(b) for the time interval when Vi = –4 V.

VO (calculated) =_____________

d) Using the results of Parts 5(b) and 5(c), sketch the expected waveform for VO using the

horizontal axis of Fig. 3.12 as the VO = 0 V line. Insert your chosen vertical and horizontal

sensitivity settings below.

EE231L – Electronics-I Lab Manual Page 39

e) Sketch of VO from calculated results:

Figure 3-10: Sketch waveform

Vertical sensitivity =_____________

Horizontal sensitivity =_____________

f) Using the sensitivities chosen in Part 5(d), set the input square wave and record VO on Fig.

4.13 using the oscilloscope. Be sure to preset the VO = 0 V line using the GND position of

the coupling switch (and the DC position to view the waveform).

Sketch of VO from measured results:

Figure 3-11: Sketch waveform

g) How does the waveform of Fig. 3.13 compare with the predicted result of Part 5(d)?

h) Reverse the battery of Fig. 3.11 and, using the measured values of R, E, and VT, calculate

the level of VO for the time interval when Vi = +4 V.

VO (calculated) =_____________

EE231L – Electronics-I Lab Manual Page 40

i) Repeat Part 5(f) for the time interval when Vi = –4 V.

VO (calculated) =_____________

j) Using the results of Parts 5(f) and 5(g), sketch the expected waveform for VO using the