Professional Documents

Culture Documents

CH - 2 Page1

CH - 2 Page1

Uploaded by

razuOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CH - 2 Page1

CH - 2 Page1

Uploaded by

razuCopyright:

Available Formats

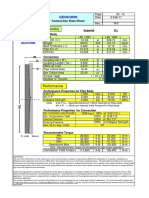

Layer Description Representation

metal

m1 m2 m3 m4 m5

well

nw

polysilicon

poly

contacts & vias

ct v12,v23,v34,v45 nwc pwc

active area

and FETs

ndif pdif nfet pfet

select

nplus pplus prb

Colorplate 1. CMOS layers and representations

(for vanilla 0.25 µm CMOS process)

0.3µ (contact to contact)

m1 0.36µ

m2

via contact

0.14µ (poly to contact)

poly

0.09µ (metal to contact)

poly-m1

poly-m1-m2 overlap overlap

0.14µ (ndif to contact)

m1

0.28µ (transistor to contact) 0.35µ

poly

metal-to-poly

n+ contact

Colorplate 4. Design rules regarding contacts and vias.

Overlapping layers are marked by merged colors.

You might also like

- General Reference ConnectionDocument51 pagesGeneral Reference ConnectionMichenerparkNo ratings yet

- Pipe Design For Lateral TestDocument1 pagePipe Design For Lateral TestSantosh ZunjarNo ratings yet

- Electronic Components, Tubes and Transistors: The Commonwealth and International Library: Electrical Engineering DivisionFrom EverandElectronic Components, Tubes and Transistors: The Commonwealth and International Library: Electrical Engineering DivisionNo ratings yet

- NDT Method Magnetic Particle InspectionDocument23 pagesNDT Method Magnetic Particle Inspectionabhaymehta67No ratings yet

- 13.375 Inch Geoconn 64-QDocument1 page13.375 Inch Geoconn 64-QBalkis FatihaNo ratings yet

- Clock Tree SynthesisDocument2 pagesClock Tree Synthesisrazu100% (1)

- Color PlatesDocument4 pagesColor PlatesChaitanya KumarNo ratings yet

- MOSFET Model - L3Document24 pagesMOSFET Model - L3AlfredRaskolnikovNo ratings yet

- Leoni Special Cables GMBH: Design WireDocument2 pagesLeoni Special Cables GMBH: Design WireLeodoletaNo ratings yet

- Mask Summary: The Only Mask Involved With Contacts To Active or PolyDocument1 pageMask Summary: The Only Mask Involved With Contacts To Active or PolyCarlos SaavedraNo ratings yet

- ACI Design - 05 - Design of Slab SectionDocument2 pagesACI Design - 05 - Design of Slab SectionArcal General ConstructionNo ratings yet

- Lecture 18-19Document25 pagesLecture 18-19Ahmed SFNo ratings yet

- E Book SemiconductorsDocument8 pagesE Book SemiconductorskaanNo ratings yet

- Chapter 1 Introduction: Fabrication ProcessDocument1 pageChapter 1 Introduction: Fabrication ProcessCarlos SaavedraNo ratings yet

- The Development of Flexible Integrated Circuits Based On Thin-Film TransistorsDocument10 pagesThe Development of Flexible Integrated Circuits Based On Thin-Film TransistorsJOAM MANUEL RINCÓN ZULUAGANo ratings yet

- Tightening Torque 0,4 NM: Dehnpipe Dpi MD 24 M 2SDocument6 pagesTightening Torque 0,4 NM: Dehnpipe Dpi MD 24 M 2Syvan_huamanNo ratings yet

- Cmos Layout Design RulesDocument18 pagesCmos Layout Design RulesbharathababuNo ratings yet

- Sub-D Feedthroughs: Three Versions For Different Technical RequirementsDocument2 pagesSub-D Feedthroughs: Three Versions For Different Technical RequirementsDeaNo ratings yet

- AXE340124Document9 pagesAXE340124jenny flyerNo ratings yet

- 16 MM XA Series & 22 MM XW Series SEMI S2 Compliant EMO SwitDocument8 pages16 MM XA Series & 22 MM XW Series SEMI S2 Compliant EMO SwitMuhamad PriyatnaNo ratings yet

- Final Design Calculation 2 MLD 09-06-16Document54 pagesFinal Design Calculation 2 MLD 09-06-16abu bakkarNo ratings yet

- Non-Volatile Magnetic Random Access Memories (MRAM) : R.C. Sousa, I.L. PrejbeanuDocument10 pagesNon-Volatile Magnetic Random Access Memories (MRAM) : R.C. Sousa, I.L. PrejbeanuQueary OnlyNo ratings yet

- M63850P MitsubishiElectricDocument5 pagesM63850P MitsubishiElectricsrinitce_meNo ratings yet

- 2) Full ReportDocument85 pages2) Full Reportapi-3784079No ratings yet

- MS419863-33 OTN DAT EN v1.1Document4 pagesMS419863-33 OTN DAT EN v1.1victor mauricio colonia rangelNo ratings yet

- Leoni Coaxial Cable 50 Ohm TypeDocument2 pagesLeoni Coaxial Cable 50 Ohm TypepeizanuNo ratings yet

- L45466 B18 C76 en PDFDocument2 pagesL45466 B18 C76 en PDFpeizanu100% (1)

- Compliance Statement: Specification For Fiber Optic Cable Requirement P117&P116Document7 pagesCompliance Statement: Specification For Fiber Optic Cable Requirement P117&P116Komal GowdaNo ratings yet

- Cathodic Calculation RuleDocument8 pagesCathodic Calculation RulegtomehNo ratings yet

- Sisymposiumharrisburgpaworkshoptraceyvincent PDFDocument76 pagesSisymposiumharrisburgpaworkshoptraceyvincent PDFNancyNo ratings yet

- Datasheet Uni LPB RoughDocument2 pagesDatasheet Uni LPB RoughSaepul RochmanNo ratings yet

- An Introduction To Integrated An Introduction To Integrated Circuits and CMOS TechnologyDocument34 pagesAn Introduction To Integrated An Introduction To Integrated Circuits and CMOS Technologymm16467No ratings yet

- Ribbon Anode Soil Och ConcreteDocument1 pageRibbon Anode Soil Och ConcreteSoltani AliNo ratings yet

- Ultra-Low Profile Dome Key B3DDocument3 pagesUltra-Low Profile Dome Key B3DMuhamad PriyatnaNo ratings yet

- AS5000-MS-10-300 SpecAS5311 v0 1 PDFDocument7 pagesAS5000-MS-10-300 SpecAS5311 v0 1 PDFBruno TondinNo ratings yet

- Industrial Ethernet Cat 5E: Leoni Special Cables GMBHDocument2 pagesIndustrial Ethernet Cat 5E: Leoni Special Cables GMBHLeodoletaNo ratings yet

- Adobe Scan 06-Oct-2021Document1 pageAdobe Scan 06-Oct-2021Lakshmipavani PonnapalliNo ratings yet

- EMI Characteristics AnalysisDocument16 pagesEMI Characteristics AnalysisToánNo ratings yet

- l6 Fabrication StepsDocument16 pagesl6 Fabrication StepsMohit GautamNo ratings yet

- Steel Base Plate (LRFD) : ConcreteDocument2 pagesSteel Base Plate (LRFD) : ConcreteAbdullahibnfulanNo ratings yet

- 08-ICT - CMOS Process IntegrationDocument63 pages08-ICT - CMOS Process IntegrationCyrille MagdiNo ratings yet

- S1 PDFDocument4 pagesS1 PDFjohnyNo ratings yet

- E Term01Document2 pagesE Term01Izzan FirdausNo ratings yet

- Sector Group Sub - GroupDocument8 pagesSector Group Sub - Grouppradeep parajuliNo ratings yet

- Intro To 2d PhysicsDocument66 pagesIntro To 2d PhysicsabdoNo ratings yet

- Leoni Sealine: Cable Type: 9Y (ST) CH 4X2X0.6/1.2-100 Li GN FRNCDocument2 pagesLeoni Sealine: Cable Type: 9Y (ST) CH 4X2X0.6/1.2-100 Li GN FRNCLeodoletaNo ratings yet

- Cuellar 2012Document6 pagesCuellar 2012Dr. Arijit RoyNo ratings yet

- Serrated Washers, Locknuts MetricDocument1 pageSerrated Washers, Locknuts MetricSamdan NamhaisurenNo ratings yet

- 8 LD Mesh Ribbon AnodesDocument2 pages8 LD Mesh Ribbon AnodesFareed KhanNo ratings yet

- Digital Integrated Circuit (IC) Layout and DesignDocument23 pagesDigital Integrated Circuit (IC) Layout and DesignPoornima RajanNo ratings yet

- TDS 33KV 150sqmm X 3C+50 AL-XLPE-SCT-PVC ABC Refer TNB SpecDocument2 pagesTDS 33KV 150sqmm X 3C+50 AL-XLPE-SCT-PVC ABC Refer TNB SpecShahril ShahibullahNo ratings yet

- Dic Lec 02 Fabrication v01Document68 pagesDic Lec 02 Fabrication v01fatmaadelmoNo ratings yet

- Lec 5Document19 pagesLec 5api-3721075No ratings yet

- A New Structure For Lateral Double Diffused MOSFET To Control The Breakdown Voltage and The On-ResistanceDocument9 pagesA New Structure For Lateral Double Diffused MOSFET To Control The Breakdown Voltage and The On-ResistanceamrNo ratings yet

- CMOS Fabrication 3Document10 pagesCMOS Fabrication 3rajendran2501No ratings yet

- October 07b 2002Document16 pagesOctober 07b 2002Pokala CharantejaNo ratings yet

- Lubricants 07 00017 PDFDocument14 pagesLubricants 07 00017 PDFGabriel Ivan AviñaNo ratings yet

- Line SideDocument1 pageLine SideJaiNo ratings yet

- Sic Mos Trench SJ J.spmi.2018.10.016Document14 pagesSic Mos Trench SJ J.spmi.2018.10.016terry chenNo ratings yet

- Basic Linux CommandsDocument5 pagesBasic Linux CommandsrazuNo ratings yet

- Double PatterningDocument2 pagesDouble Patterningrazu100% (1)

- Decap CellsDocument1 pageDecap CellsrazuNo ratings yet

- 05 HammerDocument59 pages05 HammerrazuNo ratings yet

- Ucin 1235504983Document152 pagesUcin 1235504983razuNo ratings yet

- Aspdac 05 PGDocument4 pagesAspdac 05 PGrazuNo ratings yet

- EC202Document7 pagesEC202razuNo ratings yet

- FulltextDocument7 pagesFulltextrazuNo ratings yet

- Its HLSDocument70 pagesIts HLSrazuNo ratings yet

- Fdocuments - in - Introduction To Digital Vlsi Design Vlsi Digivlsislidesrouting82pdf200608Document25 pagesFdocuments - in - Introduction To Digital Vlsi Design Vlsi Digivlsislidesrouting82pdf200608razuNo ratings yet

- Lect 22Document13 pagesLect 22razuNo ratings yet

- CH - 2 Page2Document1 pageCH - 2 Page2razuNo ratings yet

- Arf Lithography Technologies For 65Nm-Node Cmos (Cmos5) With 30Nm Logic Gate and High Density Embedded MemoriesDocument1 pageArf Lithography Technologies For 65Nm-Node Cmos (Cmos5) With 30Nm Logic Gate and High Density Embedded MemoriesrazuNo ratings yet

- CHAPTER - 2 (Extra) DmiaDocument6 pagesCHAPTER - 2 (Extra) DmiarazuNo ratings yet

- CH - 2 Page3Document1 pageCH - 2 Page3razuNo ratings yet