Professional Documents

Culture Documents

cs302p Assignment 2 Solution by Dilshad Ahmad

Uploaded by

MUHAMMAD NABEEL SHAHOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

cs302p Assignment 2 Solution by Dilshad Ahmad

Uploaded by

MUHAMMAD NABEEL SHAHCopyright:

Available Formats

SUBSCRIBE @ VU with Dilshad Ahmad

Total marks = 20

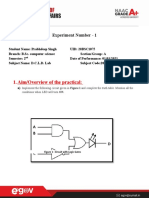

Digital Logic Design Practical

(CS302P) Deadline

th

Assignment # 02 24 of January,

Fall 2022 2023

Please carefully read the following instructions before attempting the assignment.

RULES FOR MARKING

It should be clear that your assignment would not get any credit if:

▪ The assignment is submitted after the due date.

▪ The submitted assignment does not open or the file is corrupt.

▪ Strict action will be taken if the submitted solution is copied from any other student

or the internet.

You should consult the recommended books to clarify your concepts as handouts are not

sufficient.

You are supposed to submit your assignment in Doc or Docx format & EWB File (If required).

Any other formats like scan images, PDF, ZIP, RAR, PPT, BMP, etc. will not be accepted.

Topic Covered:

• Lab Work - Week # 09 - Building Logic Circuits using Multiplexers

• Lab Work - Week # 10 - Building Digital Logic Circuits using Decoders

• Lab Work - Week # 11 - Sequential Circuits

NOTE

No assignment will be accepted after the due date via email in any case (whether it is the case

of load shedding or internet malfunctioning etc.). Hence refrain from uploading assignments

in the last hour of the deadline. It is recommended to upload the solution file at least two days

before its closing date.

If you people find any mistake or confusion in the assignment (Question statement), please

consult with your instructor before the deadline. After the deadline, no queries will be

entertained in this regard.

For any query, feel free to email me at:

cs302p@vu.edu.pk

Click Here to Watch Origional Video

SUBSCRIBE @ VU with Dilshad Ahmad

Question Statement Marks (20)

You have been provided with a function table for a 4-Variable boolean function as given below:

Number A B C D F

0 0 0 0 0 0

1 0 0 0 1 0

2 0 0 1 0 0

3 0 0 1 1 1

4 0 1 0 0 0

5 0 1 0 1 0

6 0 1 1 0 0

7 0 1 1 1 1

8 1 0 0 0 0

9 1 0 0 1 1

10 1 0 1 0 1

11 1 0 1 1 0

12 1 1 0 0 0

13 1 1 0 1 0

14 1 1 1 0 0

15 1 1 1 1 1

You are required to:

1. Generate the Boolean Expression for the Output (F) for the given table.

2. Draw the NAND Level Diagram using Electronic Workbench with the OUTPUT labelled with your

VU Student ID.

Note: Copied assignments will not be accepted. Student Must have to mention their VU Student ID in the shared circuit

diagram, otherwise, your assignment will be marked as a Copy Case as well.

Click Here to Watch Origional Video

SUBSCRIBE @ VU with Dilshad Ahmad

The simplified boolen expression is:

AB’CD’+AB’C’D+A’CD+BCD

The Nand Level diagram is following:

Click Here to Watch Origional Video

You might also like

- Troubleshooting Electronic Circuits: A Guide to Learning Analog ElectronicsFrom EverandTroubleshooting Electronic Circuits: A Guide to Learning Analog ElectronicsNo ratings yet

- DLD Project Report CompleteDocument10 pagesDLD Project Report CompleteAMMAD MAHMOODNo ratings yet

- The Ultimate Closed SicilianDocument180 pagesThe Ultimate Closed SicilianJorge Frank Ureña100% (4)

- Legacy - Wasteland AlmanacDocument33 pagesLegacy - Wasteland AlmanacВлад «Befly» Мирошниченко100% (3)

- Fall 2022 - CS302P - 2Document2 pagesFall 2022 - CS302P - 2MUHAMMAD NABEEL SHAHNo ratings yet

- Fall 2023 - CS302P - 2Document2 pagesFall 2023 - CS302P - 2SHFAIQ BAIGNo ratings yet

- Introduction To Computing (CS101) : Assignment # 01Document2 pagesIntroduction To Computing (CS101) : Assignment # 01bc200200813 JUNAID ARSHADNo ratings yet

- Introduction To VHDL: Boumerdes UniversityDocument6 pagesIntroduction To VHDL: Boumerdes UniversityTi NaNo ratings yet

- Assignment - Fall 2023 - CS302P - 2Document2 pagesAssignment - Fall 2023 - CS302P - 2ammadip465No ratings yet

- Department of Information Technology Academic Year: 2020-2021 Subject: DLD SAP ID-60003200163Document3 pagesDepartment of Information Technology Academic Year: 2020-2021 Subject: DLD SAP ID-60003200163Vashisth ZatakiaNo ratings yet

- Bahria University, Lahore Campus: Department of Computer SciencesDocument5 pagesBahria University, Lahore Campus: Department of Computer SciencesAbdul BasitNo ratings yet

- 6 PLC Program To Implement Binary To BCD ConverterDocument5 pages6 PLC Program To Implement Binary To BCD ConverterMaria GuerreroNo ratings yet

- ProjectDocument11 pagesProjectShadman ShalheNo ratings yet

- Done FPGA (Lab1)Document11 pagesDone FPGA (Lab1)Farah DurraniNo ratings yet

- Vivek MittalDocument27 pagesVivek Mittalvivek122No ratings yet

- Exp 8 (DLD)Document4 pagesExp 8 (DLD)shah hassaanNo ratings yet

- Digital Logic Design Lab 11Document3 pagesDigital Logic Design Lab 11M. Ahmad RazaNo ratings yet

- Bahria University, Lahore Campus: Department of Computer SciencesDocument4 pagesBahria University, Lahore Campus: Department of Computer SciencesAbdul BasitNo ratings yet

- DLC OEL Section o G 6Document16 pagesDLC OEL Section o G 6mashfiqur mNo ratings yet

- Paper Instructions For Students: Islamia College University Peshawar Final-Term ExaminationDocument3 pagesPaper Instructions For Students: Islamia College University Peshawar Final-Term ExaminationAltaf Ur Rehman BangashNo ratings yet

- DCLD Exp 1Document6 pagesDCLD Exp 1Prabh deepNo ratings yet

- ACTIVITY NO 7 Encoders - ELLINE PATAGANAODocument3 pagesACTIVITY NO 7 Encoders - ELLINE PATAGANAOElline PataganaoNo ratings yet

- Voting Machine Lab 11 Grp7Document19 pagesVoting Machine Lab 11 Grp7Aisha SheikhNo ratings yet

- Lab 8 CALDDocument15 pagesLab 8 CALDSara AdnanNo ratings yet

- Lab 3Document14 pagesLab 3trongnhansuper1No ratings yet

- CS101-Assignmnet 1Document5 pagesCS101-Assignmnet 1M Noaman AkbarNo ratings yet

- Zaid Zukari Coe Lab5Document6 pagesZaid Zukari Coe Lab5zaidzukari.11No ratings yet

- Best Lab ExpsDocument45 pagesBest Lab ExpsshivaNo ratings yet

- Bahria University, Lahore Campus: Department of Computer SciencesDocument7 pagesBahria University, Lahore Campus: Department of Computer SciencesAbdul BasitNo ratings yet

- Title:Implementation of 4-Line-To - 2-Line Encoder & 8-Line-To-3-Line Encoder Lab Worksheet #10Document5 pagesTitle:Implementation of 4-Line-To - 2-Line Encoder & 8-Line-To-3-Line Encoder Lab Worksheet #10MUNEEB SHAHNo ratings yet

- BC220202131 cs302pDocument2 pagesBC220202131 cs302pfecem12298No ratings yet

- 4 Logic Gates and Logic CircuitsDocument2 pages4 Logic Gates and Logic CircuitsEbad AhmedNo ratings yet

- Introduction To Robotics - MidtermDocument9 pagesIntroduction To Robotics - Midtermumar khanNo ratings yet

- Assignment No: 3: Carry Save AdderDocument7 pagesAssignment No: 3: Carry Save AdderHasnain AwanNo ratings yet

- Logic Design Lab HomeworkDocument8 pagesLogic Design Lab HomeworkKhaled Iyad DahNo ratings yet

- Encoder & Decoder Using CircuitsDocument2 pagesEncoder & Decoder Using CircuitsRaja PatelNo ratings yet

- Activity No. 4.2 and GateDocument2 pagesActivity No. 4.2 and Gatemuphils2019No ratings yet

- Title: Multiplexer Instruction AimsDocument5 pagesTitle: Multiplexer Instruction Aimssuv_fame100% (1)

- BC220201548 cs302pDocument2 pagesBC220201548 cs302pfecem12298No ratings yet

- Assignment No: 17 Group CDocument5 pagesAssignment No: 17 Group CAyimen LatheefNo ratings yet

- Data Hasil Percobaan: Tabel 6.1. Encoder 10 To 4Document2 pagesData Hasil Percobaan: Tabel 6.1. Encoder 10 To 4daffa aldiNo ratings yet

- CS223 Laboratory Assignment 2 Full Adder, 2-Bit Adder, Lab Calculator On FPGADocument5 pagesCS223 Laboratory Assignment 2 Full Adder, 2-Bit Adder, Lab Calculator On FPGAYarkin ErginNo ratings yet

- Fow Seng Joe (B1757) - LAB 1-Logic GatesDocument13 pagesFow Seng Joe (B1757) - LAB 1-Logic GatesRobert Fow JOENo ratings yet

- Implementation of A 4-Bit Binary Full AdderDocument8 pagesImplementation of A 4-Bit Binary Full AdderTanvir AhmedNo ratings yet

- Vlsi ManualDocument74 pagesVlsi ManualRameshkumar JayaramanNo ratings yet

- Digital Circuits: EE/CE 3320 / Spring 2020 / Lecture 11Document104 pagesDigital Circuits: EE/CE 3320 / Spring 2020 / Lecture 11Muhammad MontahaNo ratings yet

- Lab7: Part (A) : Design of 2-Out-Of-5 To BCD Code Converter With DisplayDocument7 pagesLab7: Part (A) : Design of 2-Out-Of-5 To BCD Code Converter With DisplaySanan yaqoobNo ratings yet

- CS302P Assignment No 02Document2 pagesCS302P Assignment No 02Waqar AhmadNo ratings yet

- Data Hasil Percobaan: Tabel 6.1. Decoder 4 To 10Document2 pagesData Hasil Percobaan: Tabel 6.1. Decoder 4 To 10daffa aldiNo ratings yet

- 2 3242 Remainder 2 1621 0 2 810 1 2 405 0 2 202 1 2 101 0 2 50 1 2 25 0 2 12 1 2 6 0 2 3 0 1 1Document2 pages2 3242 Remainder 2 1621 0 2 810 1 2 405 0 2 202 1 2 101 0 2 50 1 2 25 0 2 12 1 2 6 0 2 3 0 1 1Mahmmood AlamNo ratings yet

- 16-311: Introduction To Robotics Mid-Term Examination Spring 2007 Professor Howie Choset SolutionsDocument8 pages16-311: Introduction To Robotics Mid-Term Examination Spring 2007 Professor Howie Choset Solutionsumar khanNo ratings yet

- Lab Assignment Digital Design - نسخةDocument5 pagesLab Assignment Digital Design - نسخةMaged SarhanNo ratings yet

- Assement 04Document5 pagesAssement 04Naina PrasharNo ratings yet

- ECE 120 Worksheet 5: From Problem Statement To Digital CircuitDocument4 pagesECE 120 Worksheet 5: From Problem Statement To Digital CircuitAnatasyaOktavianiHandriatiTata100% (1)

- DLD Lab-07 Designing Decoder - BCD To 7-Segment & Binary To Gray Code Convertor and Vice VersaDocument11 pagesDLD Lab-07 Designing Decoder - BCD To 7-Segment & Binary To Gray Code Convertor and Vice VersaSubhanNo ratings yet

- Lab 10Document13 pagesLab 10Arham SiddiquiNo ratings yet

- 11 PLC Program To Implement BCD To Gray Code ConversionDocument4 pages11 PLC Program To Implement BCD To Gray Code ConversionMaria GuerreroNo ratings yet

- RIVERA Logics - Lab 8Document5 pagesRIVERA Logics - Lab 8Ricardo Edrell RiveraNo ratings yet

- Fow Seng Joe (B1757) - LAB 4-Arduino (LED Binary Counter)Document15 pagesFow Seng Joe (B1757) - LAB 4-Arduino (LED Binary Counter)Robert Fow JOENo ratings yet

- RIVERA LOGICS - Lab 6Document4 pagesRIVERA LOGICS - Lab 6Ricardo Edrell RiveraNo ratings yet

- Recent PHD ResultDocument72 pagesRecent PHD ResultSavita Kiran BNo ratings yet

- What's Cooking: Digital Transformation of the Agrifood SystemFrom EverandWhat's Cooking: Digital Transformation of the Agrifood SystemNo ratings yet

- Scribe America Final, Emergency DepartmentDocument41 pagesScribe America Final, Emergency DepartmentJulio CastilloNo ratings yet

- Hapter Stereochemistry: Lesson 1Document15 pagesHapter Stereochemistry: Lesson 1Ej FerrerNo ratings yet

- STT Tecnica QuirúrgicaDocument5 pagesSTT Tecnica QuirúrgicaNathaly GuevaraNo ratings yet

- The Invention of The Internet Connecting The WorldDocument14 pagesThe Invention of The Internet Connecting The WorldSolomia Sushko100% (1)

- Ash Behaviour of Lignocellulosic Biomass in BFB Combustion - Fuel Vol 85 - Issue 9Document9 pagesAsh Behaviour of Lignocellulosic Biomass in BFB Combustion - Fuel Vol 85 - Issue 9Eduardo DreifusNo ratings yet

- Topic 5 - Market Forces - SupplyDocument5 pagesTopic 5 - Market Forces - Supplysherryl caoNo ratings yet

- 2022 VersaDocument508 pages2022 Versaedhi9175No ratings yet

- Teachnology RubricsDocument2 pagesTeachnology RubricsGenevieve MainitNo ratings yet

- Capacity DevDocument23 pagesCapacity DevankurmanuNo ratings yet

- Hci - Web Interface DesignDocument54 pagesHci - Web Interface DesigngopivrajanNo ratings yet

- An Investigation Into The Use of GAMA Water Tunnel For Visualization of Vortex Breakdown On The Delta WingDocument7 pagesAn Investigation Into The Use of GAMA Water Tunnel For Visualization of Vortex Breakdown On The Delta WingEdy BudimanNo ratings yet

- Ramesh Patel Resume (Civil) 02Document4 pagesRamesh Patel Resume (Civil) 02RameshNo ratings yet

- Khao Yai Draft 1Document4 pagesKhao Yai Draft 1Phimthida KodcharatNo ratings yet

- Random Puzzle Questions PDF For Ibps RRB Clerk Prelims ExamDocument22 pagesRandom Puzzle Questions PDF For Ibps RRB Clerk Prelims ExamApyrvaNo ratings yet

- Waruna FernandoDocument5 pagesWaruna FernandowarunafernandoNo ratings yet

- 4 Measurement of AirspeedDocument23 pages4 Measurement of AirspeedNagamani ArumugamNo ratings yet

- Bai Tap On Tap Unit 123Document8 pagesBai Tap On Tap Unit 123Le VanNo ratings yet

- Gram Negative RodsDocument23 pagesGram Negative RodsYasir KareemNo ratings yet

- BañadosHenneaux-1993-Geometry of The 2+1 Black HoleDocument52 pagesBañadosHenneaux-1993-Geometry of The 2+1 Black HoleGuido FranchettiNo ratings yet

- Laro NG LahiDocument6 pagesLaro NG LahiIlog Mark Lawrence E.No ratings yet

- Rules and Reminders For Online Classes 2Document14 pagesRules and Reminders For Online Classes 2api-220703221No ratings yet

- Dhilp ProjectDocument53 pagesDhilp ProjectSowmiya karunanithiNo ratings yet

- SIEPAN 8PU Low Voltage Switchboards Technology by SiemensDocument4 pagesSIEPAN 8PU Low Voltage Switchboards Technology by SiemensaayushNo ratings yet

- Assignment On Rules of InferenceDocument1 pageAssignment On Rules of InferenceAlone100% (1)

- Pathorchur Coleus Aromaticus A Review of The MedicDocument9 pagesPathorchur Coleus Aromaticus A Review of The MedicDung NguyenNo ratings yet

- Benzathine Penicillin, Metronidazole and Benzyl PenicillinDocument5 pagesBenzathine Penicillin, Metronidazole and Benzyl PenicillinJorge Eduardo Espinoza RíosNo ratings yet

- ARUBA 303 SERIES DatasheetDocument7 pagesARUBA 303 SERIES DatasheethendraNo ratings yet

- Bag of Words Algorithm - Saanvi XCDocument3 pagesBag of Words Algorithm - Saanvi XCsaanviNo ratings yet