0% found this document useful (0 votes)

88 views8 pagesGate Level Minimization Lab Rubrics

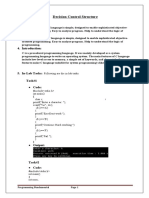

This document provides rubrics for evaluating a lab on gate level minimization of Boolean functions using K-maps. It lists several rubrics including: [1] use of engineering knowledge and following experiment procedures, [2] ability to record raw data, [3] following coding standards, [4] understanding tools, [5] individual work contributions, and [6] management of team work. It then provides a lab report on verifying the operation of multiplexers including objectives, theory, and in-lab tasks to implement 4x1 and 8x1 multiplexers using logic gates and integrated circuits. It concludes with a post-lab assignment to design a 16x1 multiplexer.

Uploaded by

Talha TufailCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOCX, PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

88 views8 pagesGate Level Minimization Lab Rubrics

This document provides rubrics for evaluating a lab on gate level minimization of Boolean functions using K-maps. It lists several rubrics including: [1] use of engineering knowledge and following experiment procedures, [2] ability to record raw data, [3] following coding standards, [4] understanding tools, [5] individual work contributions, and [6] management of team work. It then provides a lab report on verifying the operation of multiplexers including objectives, theory, and in-lab tasks to implement 4x1 and 8x1 multiplexers using logic gates and integrated circuits. It concludes with a post-lab assignment to design a 16x1 multiplexer.

Uploaded by

Talha TufailCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOCX, PDF, TXT or read online on Scribd