Professional Documents

Culture Documents

설계07. 전기기기 제어용 발진회로 설계

Uploaded by

댕댕이Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

설계07. 전기기기 제어용 발진회로 설계

Uploaded by

댕댕이Copyright:

Available Formats

전기공학설계1

설계 7.

전기기기 제어용 발진회로 설계

7.1 설계 목적

7.2 설계 주제

7.3 설계장비 및 부품

7.4 설계내용

7.5 연구과제 및 토론주제

7.6 참고 이론

설계 7. 전기기기 제어용 발진회로 설계 - 117 -

전기공학설계1

7.1 설계 목적

• 전기기기의 제어에 사용되는 발진 회로의 기본 원리를 이해한다.

• 발진회로에 가장 널리 사용되는 타이머 IC 555 소자의 동작원리와 기본적인 사용

법을 이해한다.

• 555 타이머 IC를 이용한 단안정, 비안정 발진회로의 구성과 주파수 조정회로를

구성하여 동작을 확인한다.

• 실제 전기기기의 제어에 사용되는 신호를 발생하는 발진회로를 구현한다.

7.2 설계 주제

• 40 kHz의 구형파 신호를 이용하여 구동되는 물체감지용 초음파 센서를 구동시키

기 위한 회로를 제작하고자 한다. 40 kHz의 구형파 신호가 50 Hz의 주기로 간헐

적으로 발생되는 발진회로를 설계하시오.

7.3 설계장비 및 부품

장비 / 부품명 기능 / 규격 수량

Capacitor [uF] 0.01, 0.05, 0.1, 0.2, 10 각 3개

Resistor [Ω] 10 k, 22 k, 100 k, 470 k, 1M 각 3개

Transistor [NPN] 2N2222 3 개

OP-AMP uA741 5 개

Timer IC NE555 3 개

Digital multi tester 1 개

Oscilloscope 1 대

Power Supply 1 대

설계 7. 전기기기 제어용 발진회로 설계 - 118 -

전기공학설계1

7.4 설계내용

7.4.1 단안정 동작

1) 그림 7-8의 회로를 구성하고 RA=1 MΩ, C1=10 μF을 연결한다.

2) 1-3번 단자 사이의 전압을 오실로스코프로 측정한다.

3) 표 7-2에 공식에 의한 펄스폭을 계산하여 기록한다.

4) 스위치 S1을 순간적으로 B 로 이동시킨 후, 출력펄스의 폭을 측정하고 표7-

2에 기록하라.

5) S1을 이용하여 또 다른 타이밍 사이클을 시작시키고 출력이 High인 동안 S1

을 수 차례 동작시켜 RA 및 C1 에 의해 셋 된 타이밍 사이클에 영향을 미치

지 않은 것을 확인하라(이 타이밍 사이클은 약 11초간 계속).

6) 3), 4)번을 반복하여 표 7-2를 완성하라.

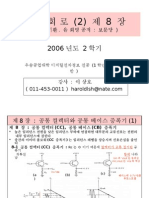

그림 7-8. 555 단안정(one-shot) 설계회로

설계 7. 전기기기 제어용 발진회로 설계 - 119 -

전기공학설계1

표 7-2. 555 단안정 회로 설계

RA[Ω] C1[μF] W (계산값) W (측정값)

1M 10

470 k 10

100 k 10

10 k 10

470 k 1

470 k 0.1

7.4.2 비안정 동작

1) 그림 7-9 의 회로를 구성하고 RA =33k, RB= 3k, C1=0.1uF을 연결한다.

2) 표 7-3 에 공식에 의한 주파수와 듀티 사이클을 계산하여 표 7-3에 기록하

라.

3) 오실로스코프로 출력을 측정하여 측정된 주파수 및 듀티 사이클을 표 7-3

에 기록하라.

4) 저항 RA 및 RB 를 변화시키면서 표 7-3을 완성하라. 이 때 파형과 그 scale

도 정확히 기록하라.

그림 7-9. 비안정 설계회로

설계 7. 전기기기 제어용 발진회로 설계 - 120 -

전기공학설계1

표 7-3. 555 비안정 회로 설계

주파수 듀티 사이클

RA [Ω] RB [Ω] C[ [μF] 계산값 측정값 계산값 측정값

33 k 3k 0.1

33 k 33 k 0.1

33 k 3k 0.01

33 k 33 k 0.01

7.4.3 제어용 발진회로 설계

그림 7-10과 같은 발진 파형이 나오도록 555 타이머와 AND gate IC를 이용하

여 회로를 구현하고 결과를 파형으로 나타내어라.

그림 7-10. 전기기기 제어용 발진파형

설계 7. 전기기기 제어용 발진회로 설계 - 121 -

전기공학설계1

7.5 연구과제 및 토론주제

7.5.1 연구과제

1. Op-amp를 이용한 위상이동발진회로를 도시하고, 동작원리를 설명하시오.

2. Transistor를 이용한 단안정, 비안정 발진회로를 설계하고, 이를 모의설계를 통해

결과를 확인하시오. (발진주파수: 10 kHz로 설계)

3. 타이머를 이용하여 발진회로를 설계할 때, 주파수를 조정하는 방법과 Duty ratio

를 조정하는 방법을 각각 설명하시오.

7.5.2 토론주제

- 일반적인 전기기기의 제어에 사용되는 발진회로를 조사하고, 이의 동작원리를 설

명하시오.

설계 7. 전기기기 제어용 발진회로 설계 - 122 -

전기공학설계1

7.6 참고 이론

7.6.1 555 타이머의 구성

타이머 IC인 555는 오늘날 시간조정용 신호 발생기회로로서 가장 널리 쓰이는

소자이며 1972년 처음 시판되었다. 예로서 한국전자에서 생산되는 555 타이머

(KIA 555 P/F)의 내부 구성은 그림 7-1과 같으며 적은 수의 저항 및 커패시터를

연결하여 다양한 타이밍펄스를 발생시킬 수 있다. VCC 및 논리 1과 0의 범위가

4.5∼16 [V]의 넓은 범위에서 허용된다. 내부의 R-S 플립플롭의 입∙출력 관계는

표 7-1과 같으며 R, S 두 입력이 모두 제거 되어도 출력은 그대로 유지되는 특징

을 갖고 있다. 두 개의 비교기는 논리 1과 0를 발생시키는 순간을 결정하며, R-S

플립플롭(또는 셋-리셋 래치)은 이들 비교기의 출력을 받아 0 또는 1신호를 출력

한다.

표 7-1. R-S 플립플롭 동작표.

R S Q (t) 비 교

0 0 Q(t-1) 변화 없음

0 1 1 Set

1 0 0 Reset

1 1 Not define

VCC DISCHARGE THRESHOLD CONTROL

VOLTAGE

8 7 6 5

R Q10

+

-

COMP1

R

R VREF

+

S Q

-

R COMP2

1 2 3 4

GND TRIGGER OUTPUT RESET

그림 7-1. 한국전자 555타이머IC의 내부 블록도(KIA 555 P/F)

설계 7. 전기기기 제어용 발진회로 설계 - 123 -

전기공학설계1

각 단자의 기능은 다음과 같다.

1) Ground: 1번 단자는 두 개의 전원단자 중 접지 또는 공통단자로 쓰이는

단자이다.

2) +VCC: 8번 단자는 양극 전원단자이다. VCC 는 4.5∼16 V 사이에서 사용가

능하며 일부 소자는 3 V까지 가능한 것도 있다. 최대 VCC 는 18 V 이하이며

최대 전력소모는 600 mW 이하로 제한된다.

3) Output: 3번 단자는 출력단자로서 다른 회로에 연결된다. 이곳의 전압은

플립플롭의 조건에 따라 제어되며 1 또는 0 상태가 된다. 0 상태에서는 0 V

또는 접지전위이며 1 상태에서는 +VCC가 된다.

4) Trigger: 2번 단자에는 COMP2의 트리거 전압이 인가된다. 1/3∙VCC이하의

전압이 나타나면 COMP2의 상태가 바뀌어 출력은 1 상태가 된다.

5) Threshold: 6번 단자에는 COMP1의 문턱전압이 인가된다. 보통은 이 단자

와 접지 사이에 커패시터가 연결된다. 555 타이머의 2번 입력이 순간적으로

영으로 트리거되면 출력은 1이 되면서 내부 트래지스터가 오프되고 커패시

터는 VCC로 충전되기 시작한다. 커패시터의 전압이 2/3∙ VCC의 문턱전압 이

상이 되면 COMP1는 상태를 바꾸게 되고 플립플롭을 리셋시켜 출력은 0

상태가 된다.

6) Reset: 4번 단자는 플립플롭을 직접 제어하는 리셋 입력이다. 이 단자의

입력은 다른 모든 단자의 입력과 무관하게 영향을 미친다. 이 리셋 단자에

0 V 가 인가되면 3번 Output 단자와 7번 Discharge 단자는 0 상태가 된다.

이 단자를 사용하지 않을 때는 +VCC 단자에 연결한다.

7) Discharge: 7번 단자는 외부 커패시터의 방전에 사용된다. 이 단자는 저항

을 통하거나 또는 직접 6번 단자에 연결한다. 출력이 1상태이면 7번 단자

에 연결된 내부 트랜지스터(Q10)이 OFF 되어 외부 커패시터를 VCC 로 충전

한다. 출력이 0 상태가 되면 ON 되어 커패시터를 접지로 방전시킨다.

8) Control Voltage: 5번 단자는 제어 전압 입력(FM)이다. 이 단자는 내부적으

로 비교기의 기준전압 분배기인 세 개의 저항 사이에 연결된다. 이 단자에

인가된 전압은 문턱 및 트리거 전압을 변화시켜 출력을 변조시킨다. 이 단

자를 사용하지 않을 때는 0.01 μF의 커패시터를 접지 단자에 연결하여 전

원의 리플과 잡음을 바이패스 시켜 영향을 최소화한다.

흔히 사용되는 555타이머 IC의 외형을 그림 7-2에 보였다.

설계 7. 전기기기 제어용 발진회로 설계 - 124 -

전기공학설계1

F PACKAGE

GND 1 14 VCC

H PACKAGE*

NC 2 13 NC

VCC

TRIGGER 3 12 DISCHARGE

N, FE PACKAGE

⑧

GROUND

GROUND 1 8 VCC OUTPUT 4 11 NC ① ⑦ DISCHARGE

TRIGGER 2 7 DISCHARGE NC 5 10 THRESHOLD TRIGGER ② ⑥ THRESHOLD

OUTPUT 3 6 THRESHOLD RESET 6 9 NC OUTPUT ③ ⑤ CONTROL

VOLTAGE

④

RESET 4 5 CHNTROL NC 7 8 CONTROL

VOLTAGE VOLTAGE RESET

(a) 8핀 미니-DIP (b) 14핀 DIP (c) 8핀 금속 캔

(한국전자 KIA 555 P/F)

그림 7-2. 555타이머 IC의 일반적 외형

7.6.2 단안정 동작

단안정(one shot)이란 단 한 가지의 안정상태를 가지며 외부 트리거 신호에

의하여 미리 정해진 시간동안 상태가 바뀌었다가 다시 원래 상태로 돌아온다. 그

림 7-3처럼 외부 단자에 저항 및 커패시터를 연결한 후 외부 트리거 입력이

VCC/3이하가 되면 COMP2의 출력이 높아져 플립플롭을 세트시킨다. 결국 이 트

랜지스터가 OFF 되어 커패시터는 충전된다.

그림 7-3. 555를 이용한 단안정 회로구성

설계 7. 전기기기 제어용 발진회로 설계 - 125 -

전기공학설계1

커패시터가 충전되어 Threshold 입력이 비교기의 기준전압 2/3VCC 이상이 되면

비교기는 트리거되고 플립플롭은 리셑된다. 플립플롭이 리셑되면 방전 트랜지스터

가 ON되어 커패시터는 급격히 방전된다. 커패시터 C 는 저항 R 을 통하여 충전되

어야 하므로 RC 시정수가 커패시터의 충전속도를 결정하여 출력펄스의 폭을 결정

한다. 커패시터 전압에 대한 지수식을 구하면 펄스 폭은

W 1.1.RC[sec] (7-1)

의 식으로 주어지며 W 는 sec, R 은 Ω, C 는 F의 단위를 갖는다. 그 관계는

그림 7-4와 같다. 단안정 동작은 시간지연, 손상된(ragged)펄스파형의 재생, 입력

펄스 확장, 바운스 없는 스위치 등의 용도에 사용된다. 일반적으로 설계회로에서는

IC내부의 블록인 OP-amp나 플립플롭, 저항 등은 나타내지 않으며 다만 그림 7-5

와 같이 IC와 외부소자의 연결만을 나타낸다.

그림 7-4. 단안정 동작과 파형

설계 7. 전기기기 제어용 발진회로 설계 - 126 -

전기공학설계1

+VCC

R 4 8

7 3

Vout

555

6 5

C

2 1

0.01μF

TRIGGER

그림 7-5. 555 단안정 회로

7.6.3 비안정 동작

555 IC를 그림 7-6처럼 연결하면 비안정(자유 러닝: free running or astable)

동작을 하므로 클럭 발생기로도 불린다. 출력은 구형파이고 리셑 단자는 VCC 에

연결하며 5번 단자에는 Cf 가 잡음제거용으로 연결된다. 방전 트랜지스터는 OFF

되어 있고 C 는 RA, RB를 통하여 충전되므로 시정수는 다음과 같다.

( R A RB )C (7-2)

C 가 충전되어 문턱전압이 2/3VCC 이상이 되면 COMP1이 높은 출력이 되어

플립플롭을 리셑시킨다. 방전 트랜지스터가 온 되어 7번 단자는 접지된다. 이제

커패시터는 RB 를 통하여 방전된다. 방전시 시정수는 τ = RB∙C 이다. 커패시터 전

압이 VCC/3 이하로 떨어지면 COMP2가 높은 출력이 되어 플립플롭을 세트시키고

방전 트랜지스터는 오프되고 C는 RA, RB를 통하여 다시 충전된다. 충전 시정수는

방전 시정수보다 길어서 출력은 대칭적이 아니며 1인 상태가 더 오래 지속된다.

설계 7. 전기기기 제어용 발진회로 설계 - 127 -

전기공학설계1

+VCC

RA

4 8

7 3

Vout

555

RB 6 5

2 1 0.01μF

C

그림 7-6. 비안정 발진회로

비대칭 정도를 나타내는 것으로 듀티 사이클(duty cycle)이 있으며 D=W/T×

100 %로 정의된다. RA와 RB의 값에 따라 듀티 사이클은 50∼100 %값을 갖게 된

다. 출력 주파수와 듀티 사이클은 다음과 같다.

1.44 (7-3)

f

( R A 2 R B )C

R A RB

D 100 % (7-4)

R A 2RB

7.6.4 부하의 연결

555의 출력은 토템폴 구성을 기본으로 하며 타이머의 출력을 그림 7-7(a)와 같

이 두 트랜지스터의 베이스회로에 위쪽 트랜지스터에는 직접 연결하고 아래쪽 트랜

지스터에는 인버터를 거쳐 연결한다.

이 경우 타이머의 출력이 낮은 경우 아래쪽 트랜지스터가 온 되어 부하를 통하여

아래쪽 트랜지스터가 전류 싱크처럼 동작하여 정상상태에서 출력은 영이 된다. 타

이머의 출력이 높은 상태이면 위쪽 트랜지스터가 전류소스처럼 동작하여 부하전류

가 흐르게 되고 정상상태에서 1이 된다.

설계 7. 전기기기 제어용 발진회로 설계 - 128 -

전기공학설계1

+VCC +VCC

Off On

3 Output=0V 3 Output=Vcc

On Off

(a) (b)

그림 7-7. 부하의 연결 (토템플 출력)

설계 7. 전기기기 제어용 발진회로 설계 - 129 -

전기공학설계1

설계 7. 전기기기 제어용 발진회로 설계 - 130 -

You might also like

- 설계06. DC power supply 설계 및 제작Document17 pages설계06. DC power supply 설계 및 제작댕댕이No ratings yet

- 제 1장 RC 회로의 시간 응답Document11 pages제 1장 RC 회로의 시간 응답E석ᄒNo ratings yet

- 설계04. AD - DA 컨버터 응용 전기회로 설계Document12 pages설계04. AD - DA 컨버터 응용 전기회로 설계댕댕이No ratings yet

- 설계05. 전기기기 전원부의 정전압 및 정전류 회로 설계Document16 pages설계05. 전기기기 전원부의 정전압 및 정전류 회로 설계댕댕이No ratings yet

- 전자회로실험 2Document16 pages전자회로실험 2윤영주No ratings yet

- ES-5925-0001 전문 교류차단기Document29 pagesES-5925-0001 전문 교류차단기박정모No ratings yet

- 발진기Document36 pages발진기뜌링뚜No ratings yet

- (06차시) 자동차제어회로 설계기술기초Document21 pages(06차시) 자동차제어회로 설계기술기초bestupNo ratings yet

- 세기전자정비메뉴얼 (구형) 노랑색Document28 pages세기전자정비메뉴얼 (구형) 노랑색최영진No ratings yet

- 전자회로의 기초Document44 pages전자회로의 기초지용No ratings yet

- 아날로그집적회로설계Document56 pages아날로그집적회로설계fourier76100% (6)

- 전자기계회로 (4-아날로그 전자회로)Document29 pages전자기계회로 (4-아날로그 전자회로)fourier76No ratings yet

- VS (Ver 4.3) (021-040)Document20 pagesVS (Ver 4.3) (021-040)NikoNo ratings yet

- 전자회로1 1학기실험책Document56 pages전자회로1 1학기실험책명지훈No ratings yet

- A Study On The Generation of Stable Negative Voltage For IT EquipmentsDocument6 pagesA Study On The Generation of Stable Negative Voltage For IT Equipmentswoojoo1324No ratings yet

- 컨버터 병렬제어Document44 pages컨버터 병렬제어조용규No ratings yet

- 레포트광운대 전기과Document24 pages레포트광운대 전기과beom oNo ratings yet

- 3.회로기판고장진단및수리기초 기본교안Document123 pages3.회로기판고장진단및수리기초 기본교안터미네이터No ratings yet

- Battery Charger (Tdc-9030a) ManualDocument15 pagesBattery Charger (Tdc-9030a) Manualauto etrustNo ratings yet

- Reprot For UniversityDocument24 pagesReprot For Universitybeom oNo ratings yet

- 계통전압제어Document66 pages계통전압제어KI OHNo ratings yet

- (2022) E07 스피커 구동용 Power Amp 이해Document23 pages(2022) E07 스피커 구동용 Power Amp 이해김지수No ratings yet

- Transistor D2012 PDFDocument1 pageTransistor D2012 PDFajcontre447No ratings yet

- Cable Supervision CS-08TDocument11 pagesCable Supervision CS-08Tdonald33No ratings yet

- MS Servo PDFDocument29 pagesMS Servo PDFdae hee hanNo ratings yet

- 실습1 - Op Amp를 이용한 다양한 Amplifier 설계Document5 pages실습1 - Op Amp를 이용한 다양한 Amplifier 설계임수민No ratings yet

- 물리학및실험2 4주차 실험레포트 202310718 김동욱Document12 pages물리학및실험2 4주차 실험레포트 202310718 김동욱rhddnr0201No ratings yet

- Cam Switch 02Document70 pagesCam Switch 02Nguyễn Anh TuấnNo ratings yet

- Time Constant and RC&RL CircuitDocument19 pagesTime Constant and RC&RL CircuitokysNo ratings yet

- TR그래프보는법Document4 pagesTR그래프보는법First PlanetNo ratings yet

- 변압기 명판 설명 (현대중공업)Document8 pages변압기 명판 설명 (현대중공업)Joey seoNo ratings yet

- Grounding and Grounding Fault AnalysisDocument31 pagesGrounding and Grounding Fault AnalysisWonbae ChoiNo ratings yet

- Study On Transformer Saturation in Isolated Full-Bridge DC-DC ConvertersDocument8 pagesStudy On Transformer Saturation in Isolated Full-Bridge DC-DC ConvertersArmandinho CaveroNo ratings yet

- Making Digtal Watch Using BreadboardDocument7 pagesMaking Digtal Watch Using Breadboarddbswnddl1010No ratings yet

- Kasys Relay Socket - KoreaDocument44 pagesKasys Relay Socket - Koreatuanvutt0% (1)

- 정류기 운영 Manual - - REV01Document24 pages정류기 운영 Manual - - REV01Justice KNo ratings yet

- UntitledDocument60 pagesUntitled구서경No ratings yet

- 01 - ACD3 SystemDocument9 pages01 - ACD3 SystemRenee CarranzaNo ratings yet

- 2.회로기판고장진단및수리기초 기본교안Document110 pages2.회로기판고장진단및수리기초 기본교안bloodyseo083 lolNo ratings yet

- Sconi 2250 ADocument2 pagesSconi 2250 A반기서No ratings yet

- VS (Ver 4.3) (041-060)Document20 pagesVS (Ver 4.3) (041-060)NikoNo ratings yet

- EC1 Quiz2 Solution 2015 1Document7 pagesEC1 Quiz2 Solution 2015 1이진규No ratings yet

- 전자회로 설계 및 실험 5 예보Document10 pages전자회로 설계 및 실험 5 예보dendy0721No ratings yet

- 발전기 출력곡선 이해Document30 pages발전기 출력곡선 이해이경No ratings yet

- 2018년2회전기기사 (최종수정)Document11 pages2018년2회전기기사 (최종수정)leemhyunseok100% (1)

- 01장 들어가기Document24 pages01장 들어가기jessica0418kNo ratings yet

- 전기전자기초실험Document87 pages전기전자기초실험b3031105No ratings yet

- 2.저항 콘덴서 (test1)Document60 pages2.저항 콘덴서 (test1)Yoon-Il KimNo ratings yet

- 설계실습4. 예비보고서 - 정세현20220828Document3 pages설계실습4. 예비보고서 - 정세현20220828tpguseeNo ratings yet

- D-26-2012 공정용 안전밸브의 기술지침Document27 pagesD-26-2012 공정용 안전밸브의 기술지침최재원No ratings yet

- 108Document69 pages108necrosed12No ratings yet

- Electron 08Document19 pagesElectron 08fourier76No ratings yet

- 제 3장 MOSFET 증폭기의 주파수 응답Document7 pages제 3장 MOSFET 증폭기의 주파수 응답E석ᄒNo ratings yet

- As 124153 LJ-X8000 SG C11ko KK KR 2101 1Document47 pagesAs 124153 LJ-X8000 SG C11ko KK KR 2101 1이용상No ratings yet

- 2장Document4 pages2장soonkyu KwonNo ratings yet

- (강의교안) 아날로그 오실로스코프Document15 pages(강의교안) 아날로그 오실로스코프PARK, SANGYEOLNo ratings yet

- VFD-M 한글메뉴얼 PDFDocument131 pagesVFD-M 한글메뉴얼 PDF조현의No ratings yet