Professional Documents

Culture Documents

2 Input Nand Gate

Uploaded by

naimur 03Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

2 Input Nand Gate

Uploaded by

naimur 03Copyright:

Available Formats

Experiment Number: 01

Experiment Name: Design 2- input NAND gate using Vivado Xilinx Design Suite.

Objective:

The objective of this experiment is to design a 2-input NAND gate using the Vivado Xilinx Design

Suite, and to verify the functionality of the design through simulation and testing.

Theory:

The NAND gate with two inputs is a digital logic gate that performs a NOT-AND operation on

two input signals. The NAND gate is a combination of an AND gate and a NOT gate, with the

AND gate's output inverted. A 2-input NAND gate is represented by a standard AND gate with a

small circle on the output indicating inversion. The inputs are marked A and B, and the output is

marked Y. The truth table for a two-input NAND gate displays the output for all possible input

combinations. When both A and B inputs are high (1), the output Y is low (0). When either input

A or B is zero, the output Y is positive (1).The 2-input NAND gate functions as a NOT-AND gate,

which means it will output a high signal (1) if both inputs are not high (0) and a low signal (0) if

both inputs are high (1). It can also be used as an AND-NOT gate, producing a high signal (1)

when one or both inputs are low (0) and a low signal (0) when both inputs are high (1).

Figure-1: Symbol of 2- input NAND gate.

Truth Table of 2-input NAND gate:

A(input) B(input) Y(output)

0 0 1

0 1 1

1 0 1

1 1 0

Required Apparatus:

1. Vivado Xilinx Design Suite HLx editions.

2. Personal Computer.

VHDL Code for 2-input NAND gate:

entity nand_gate10 is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

Y : out STD_LOGIC);

end nand_gate10;

architecture Behavioral of nand_gate10 is

begin

Y <= not (A and B);

end Behavioral;

OUTPUT:

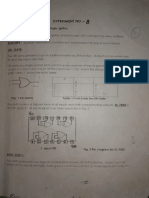

Figure-2: Schematic diagram of 2- input NAND gate.

Figure-3: Output waveform of 2- input NAND gate.

Result and Discussion:

In this experiment, we came to know about implementing NAND gate using VHDL language in

Vivado Xilinx design suite. Two input NAND gate is introduced here. After initiating proper

logical steps, output schematic and waveform is accomplished. Force clock pulses are given to

observe real time value of NAND gate operation. The waveform was generating accurate value of

input and output bits. The output is achieved by implementation, synthesis and simulation after

providing necessary instructions.

Precaution:

1. The VHDL code was correctly written.

2. The code was executed after it had completed its checks.

3. The output was thoroughly examined.

You might also like

- DLD Lab Report 3 PDFDocument6 pagesDLD Lab Report 3 PDFArnab DeyNo ratings yet

- STLD Lab ExperimentsDocument30 pagesSTLD Lab Experimentslokesh krapaNo ratings yet

- Lab 2Document4 pagesLab 2Arif KamalNo ratings yet

- DLD Lab 02 - Basic Logic Gates - V3Document16 pagesDLD Lab 02 - Basic Logic Gates - V3Hamna MansoorNo ratings yet

- DSD Lab ManualDocument65 pagesDSD Lab Manualmjeevansai07No ratings yet

- Logic Gates Lab ReportDocument9 pagesLogic Gates Lab ReportZAINUL ABIDEENNo ratings yet

- De All ManualsDocument44 pagesDe All ManualsAbhipsha PatroNo ratings yet

- Microprocessor Lab - Excperiment-01Document4 pagesMicroprocessor Lab - Excperiment-01Samin Sadique AurinNo ratings yet

- DLD - Lab - 1Document7 pagesDLD - Lab - 1Bunty HaqueNo ratings yet

- NEHRU SMARAKA VIDYALAYA BANGALORE Investigatory Project on Logic GatesDocument21 pagesNEHRU SMARAKA VIDYALAYA BANGALORE Investigatory Project on Logic GatesTarun ReddyNo ratings yet

- Exp 1Document4 pagesExp 1tahiaNo ratings yet

- 92301704031 DE.EXPERIMENT 1 (1)Document14 pages92301704031 DE.EXPERIMENT 1 (1)harvi.kotadiya121816No ratings yet

- DE Lab EXP.1,2,3Document18 pagesDE Lab EXP.1,2,3Saksham DhawanNo ratings yet

- 20bce2919 VL2020210700016 Ast01Document54 pages20bce2919 VL2020210700016 Ast01Sudarshan BhattaNo ratings yet

- DLD Lab Report 3 - 010324Document4 pagesDLD Lab Report 3 - 010324haideraliNo ratings yet

- Dlda - ItDocument23 pagesDlda - Itnitin_s_chauhan5239No ratings yet

- Logic Gates 1Document17 pagesLogic Gates 1saurav chauhanNo ratings yet

- Experiment Name: Study of Basic Logic GatesDocument17 pagesExperiment Name: Study of Basic Logic GatesA K M Fahim Faysal (182016018)No ratings yet

- Analog Electronic Experiment No. 1b (Digital)Document18 pagesAnalog Electronic Experiment No. 1b (Digital)SatyamNo ratings yet

- DLC LAB - 01 - Student - ManualDocument12 pagesDLC LAB - 01 - Student - ManualCarry GamingNo ratings yet

- Logic DesignDocument4 pagesLogic DesignRoshan AjithNo ratings yet

- DLD ManualDocument34 pagesDLD ManualmkollamNo ratings yet

- Digital Electronics Lab ManualDocument34 pagesDigital Electronics Lab ManualVirender ChauhanNo ratings yet

- EE203 02 Logic GatesDocument29 pagesEE203 02 Logic GatesrayNo ratings yet

- Logic Gates and Integrated Circuits GuideDocument24 pagesLogic Gates and Integrated Circuits Guidepriyadarshan sundarNo ratings yet

- 65 Mohit Tiwari IT 2 STLD FileDocument78 pages65 Mohit Tiwari IT 2 STLD FileMohit TiwariNo ratings yet

- Basic Logic Gates LabDocument18 pagesBasic Logic Gates LabMuhammad Hamza AminNo ratings yet

- DigitalDocument186 pagesDigitalAnushaChittiNo ratings yet

- 99 SG STLD LabDocument81 pages99 SG STLD Labtradersindian4No ratings yet

- Lab No 06 - Logic DesignDocument8 pagesLab No 06 - Logic DesignIDK 2No ratings yet

- Assignment No.01 (DTM) .Document14 pagesAssignment No.01 (DTM) .Om TNo ratings yet

- AI CT LOGIC GATE WORK SsuetDocument13 pagesAI CT LOGIC GATE WORK SsuetizhanfilzaNo ratings yet

- Experiment No.1 Digital Logic Gates Familirization: I. ObjectivesDocument8 pagesExperiment No.1 Digital Logic Gates Familirization: I. ObjectivesJun TobiasNo ratings yet

- Lab 1-DLDDocument4 pagesLab 1-DLDArif KamalNo ratings yet

- Digital Logic Design Lab Manual Assignment 1Document13 pagesDigital Logic Design Lab Manual Assignment 1Pirzada SwatiNo ratings yet

- Logic_Design_Lab_manualDocument7 pagesLogic_Design_Lab_manualPradhumnNo ratings yet

- 220644-663-666-DLD-Lab#1 (00Document18 pages220644-663-666-DLD-Lab#1 (00Muhammad HamzaNo ratings yet

- Experiment No. 1: FollowDocument7 pagesExperiment No. 1: FollowjainamNo ratings yet

- Fundamentals of Logic GatesDocument12 pagesFundamentals of Logic Gatesquickrelease_32100% (2)

- Ec 308 1Document58 pagesEc 308 1PRAVEEN KUMARNo ratings yet

- Digital Electronics ManualDocument49 pagesDigital Electronics ManualPratik SinghNo ratings yet

- Home Assignment No-4: Digital Logic Design BEE-1B&CDocument4 pagesHome Assignment No-4: Digital Logic Design BEE-1B&COzi ---No ratings yet

- National Institute of Technology Warangal Electronics & Communication Engineering DepartmentDocument5 pagesNational Institute of Technology Warangal Electronics & Communication Engineering DepartmentNaveen ShankarNo ratings yet

- EC Lab4 202211008 MergedDocument78 pagesEC Lab4 202211008 Mergedmexodic205No ratings yet

- DE Exp 1Document8 pagesDE Exp 1Akshat MehrotraNo ratings yet

- Lab Report Electronics 5thDocument18 pagesLab Report Electronics 5thMuhammad kawish iqbal100% (1)

- Lab-1 DLDDocument9 pagesLab-1 DLDdatamass14No ratings yet

- Digital Electronics 3rd SemDocument39 pagesDigital Electronics 3rd SemPriyanshu ThawaitNo ratings yet

- Logic Gates: Knowledge CloudDocument14 pagesLogic Gates: Knowledge CloudswarimaNo ratings yet

- Physics TheoryDocument20 pagesPhysics TheoryTANUJ CHAKRABORTYNo ratings yet

- Physics Project Theory Logic Gates ClassDocument9 pagesPhysics Project Theory Logic Gates ClassGourav BhardwajNo ratings yet

- Logic Gates and Boolean Algebra ImplementationDocument12 pagesLogic Gates and Boolean Algebra ImplementationEdmond100% (1)

- NAND, NOR, XOR and XNOR Gates ExplainedDocument15 pagesNAND, NOR, XOR and XNOR Gates ExplainedKai MoraNo ratings yet

- COA Lab Term WorkDocument28 pagesCOA Lab Term WorkHarsh JainNo ratings yet

- Logic Design Lab ManualDocument45 pagesLogic Design Lab ManualPrerna GuptaNo ratings yet

- VHDL Lab Practical File for EC EngineeringDocument32 pagesVHDL Lab Practical File for EC EngineeringTarunNo ratings yet

- Lesson 1 Logic GatesDocument29 pagesLesson 1 Logic GatesGerundio, Jean Liven H.No ratings yet

- Digital Logic Technology: Engr. Muhammad Shan SaleemDocument9 pagesDigital Logic Technology: Engr. Muhammad Shan SaleemAroma AamirNo ratings yet

- Verify The Truth Table For Basic Gates and Others Logic Gates.Document2 pagesVerify The Truth Table For Basic Gates and Others Logic Gates.হাসিন মুসাইয়্যাব আহমাদ পুণ্যNo ratings yet

- SystemDocument8 pagesSystemmappy396458100% (1)

- Westermo Ds General SFP 100 Mbit Fibre Copper Transceiver 1901 RevfDocument2 pagesWestermo Ds General SFP 100 Mbit Fibre Copper Transceiver 1901 Revfklamar5No ratings yet

- Edm PowerexplanationDocument8 pagesEdm Powerexplanationapi-3711466No ratings yet

- Electrical Design Engineer ResumeDocument2 pagesElectrical Design Engineer ResumeMukesh KumarNo ratings yet

- Emergency Lighting Supply Unit Ceaguard 48: 1at 2atDocument15 pagesEmergency Lighting Supply Unit Ceaguard 48: 1at 2atNicusor MiertescuNo ratings yet

- RF and Microwave Power Dividers and Circulators (EC 31005Document46 pagesRF and Microwave Power Dividers and Circulators (EC 31005POPURINo ratings yet

- Dynamic Resolution of Image Edge Detection Technique Among Sobel, Log, and Canny AlgorithmsDocument5 pagesDynamic Resolution of Image Edge Detection Technique Among Sobel, Log, and Canny AlgorithmsijsretNo ratings yet

- Ewis Training ManualDocument36 pagesEwis Training ManualNikolaos Kechagias100% (2)

- CSS10 - Teacher - Made - Home - Task - MELC 1.2 Computer Hardware IdentificationDocument7 pagesCSS10 - Teacher - Made - Home - Task - MELC 1.2 Computer Hardware IdentificationFaye LouraneNo ratings yet

- Modular Analog Audio Mixer - PAPERDocument11 pagesModular Analog Audio Mixer - PAPERFabio MonteiroNo ratings yet

- Control Flow Rate LabDocument5 pagesControl Flow Rate LabAnas OmarNo ratings yet

- SK-24 Operation ManualDocument13 pagesSK-24 Operation Manualgarden00589No ratings yet

- Digital Image Enhancement TechniquesDocument42 pagesDigital Image Enhancement TechniquesJahanvi VyasNo ratings yet

- Operation Smart-UPS® VTDocument44 pagesOperation Smart-UPS® VTویرا محاسب پاسارگادNo ratings yet

- IP SMC - For SLA Team AllDocument374 pagesIP SMC - For SLA Team AllAmanNo ratings yet

- Cps Tds Conduits ElectricalDocument2 pagesCps Tds Conduits Electricalbabakfun2000No ratings yet

- 8999 4928 00 Diagrams and DrawingsDocument258 pages8999 4928 00 Diagrams and DrawingsCarlos RiveraNo ratings yet

- Project Title A New Three Phase Seven-Level Inverter With Cascaded H-Bridge TopologyDocument6 pagesProject Title A New Three Phase Seven-Level Inverter With Cascaded H-Bridge TopologyEjNo ratings yet

- Soundwel AE Product CatalogueDocument18 pagesSoundwel AE Product CatalogueHenry CruzNo ratings yet

- 1.1 Laser CommunicationDocument15 pages1.1 Laser CommunicationSonali MaliNo ratings yet

- Snubber Circuits ExplainedDocument9 pagesSnubber Circuits ExplainedcoolsinghrkNo ratings yet

- BTC Pump Data SheetDocument10 pagesBTC Pump Data SheetПенови ИнженерингNo ratings yet

- Different Views on Keyboard: Inside the Keyboard and How it Communicates with the ComputerDocument14 pagesDifferent Views on Keyboard: Inside the Keyboard and How it Communicates with the ComputerDebashis SarkarNo ratings yet

- d43256 Memorie de 256kDocument25 pagesd43256 Memorie de 256kapi-252724932No ratings yet

- Norge Av Max Nov 07 ReviewDocument3 pagesNorge Av Max Nov 07 ReviewbabanpNo ratings yet

- 6 - Dynamic Model of The Induction MotorDocument11 pages6 - Dynamic Model of The Induction MotorQuynh tran100% (2)

- Transfer Functions and Frequency Responses ExplainedDocument13 pagesTransfer Functions and Frequency Responses Explainedorg25grNo ratings yet

- Sony cfd-v10 SMDocument50 pagesSony cfd-v10 SMFerran AlfonsoNo ratings yet

- ASR903 HW InstallDocument166 pagesASR903 HW InstallStanislaw Martins RodriguesNo ratings yet

- VAMP 260: Power Monitoring UnitDocument162 pagesVAMP 260: Power Monitoring UnitAli HassanNo ratings yet