Professional Documents

Culture Documents

LOGIC - CIRCUITS Final Exam Q3 2009 - 2010 ANSWER KEY Ver 2003

Uploaded by

Simon Gregory MabantaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

LOGIC - CIRCUITS Final Exam Q3 2009 - 2010 ANSWER KEY Ver 2003

Uploaded by

Simon Gregory MabantaCopyright:

Available Formats

School of EECE

LOGIC CIRCUITS &

FINAL EXAMINATION Q3 SY 2009 - 2010

SWITCHING THEORY I

NOTE: CHEATING IN ANY FORM WILL NULLIFY YOUR EXAM AND WILL BE A GROUND FOR AN

AUTOMATIC GRADE OF 5.00.

MULTIPLE CHOICE: Select the most appropriate answer from the given choices.

1. This is a group of n bits that assume up to 2n distinct combinations of 1’s and 0’s, with each

combination representing one element of the set that is being coded.

a. 2n-bit binary code c. 2n-bit binary code

b. 2n-1-bit binary code d. n-bit binary code

2. A datapath, when combined with the control unit, forms a component referred to as ______.

a. central processing unit c. output unit

b. input unit d. memory unit

3. The equivalent of the decimal number 41.6875 in the binary numbering system is _________

a. 101011.1101 c. 101001.1011

b. 101010.0011 d. 101011.0111

4. The binary number 101100 01101011.11110010, when converted to hexadecimal is ______

a. C D 7 A . 2 F c. B 1 A 2 . 2 F

b. 1 C 6 C . F 2 d. 2 C 6 B . F 2

5. Using the signed-1’s complement format, the representation of -7 is __________.

a. 1001 c. 1000

b. 1111 d. 0111

6. Each of the following 4 numbers has a different base. Which of the four numbers have the same

value in decimal ?

(a) 20225 (b) 120113 (c) 33124 (d) 19A12

a. b & d c. a & d

b. c & d d. b & c

7. Given two decimal numbers 694 and 835. Their sum in BCD is ________

a. 00111111001001 c. 0001010100101001

b. 01011111001001 d. none of these

8. The result of subtracting 654253758 from 740152368 is ___________

a. 6367541 c. 6267641

b. 6367641 d. 6367541

9. The Boolean expression (X+Y+Z)’ = X’Y’Z’ is an example of which Law/Theorem?

a. Commutative Law c. Idempotent Law

b. DeMorgan’s Theorem d. Consensus Theorem

“Knowledge is of no value unless you put it into practice.”

- Heber J. Grant

10. The Boolean expression (X’)’ is an example of which Law/Theorem?

a. Commutative Law c. Idempotent Law

b. Involution Law d. DeMorgan’s Theorem

11. The Boolean expression X + Y = Y + X is an example of which Law/Theorem?

a. Commutative Law c. Idempotent Law

b. Involution Law d. DeMorgan’s Theorem

12. This is the basic mathematics needed for the study of the logic design of digital systems.

a. Combinational Design c. Boolean Algebra

b. Sequential Design d. Quine-McCluskey Technique

13. This has one or more inputs and one or more outputs which take on discrete values.

a. digital system c. finite state machine

b. switching circuit d. algorithmic state machine

14. This part of the design of digital system involves determining how to interconnect basic logic

building blocks to perform a specific function

a. block diagram c. iterative design

b. system design d. logic design

15. This is a standard binary code for the alphanumeric characters that uses seven bits to code 128

characters.

a. Hollerith Code c. EBCDIC Code

b. Gray Code d. ASCII Code

16. This is defined as a single variable within a term, in complemented or uncomplemented form.

a. constant c. coefficient of variable

b. literal d. unary variable

17. Digital integrated circuits are classified not only by their complexity or logical operation, but also by

the specific circuit technology to which they belong. The circuit technology is referred to as _____.

a. large-scale integration c. small-scale integration

b. medium-scale integration d. digital logic family

18. What logical reason/s can you give why NAND and NOR gates are considered universal gates?

a. they can appear anywhere in the circuit c. they can imitate function of other gates

b. they can produce universal operation d. they cannot be partial

19. A race condition happens in an R-S latch when the inputs are ______

a. both zero c. both one

b. either zero or one d. none of these

20. This is the time needed by a gate in processing its input signals before the output signal can be

generated

a. setup time c. hold time

b. propagation delay time d. threshold time

“Knowledge is of no value unless you put it into practice.”

- Heber J. Grant

21. Which of the following circuits function like an inverter or NOT gate?

a) c)

b) d)

21. This is the maximum external noise voltage added to an input signal that does not cause an

undesirable change in the circuit output

a. maximum noise ceiling c. noise margin

b. noise saturation d. tolerance

23. What will happen if the function v(w+x+y)z would be implemented using NOR gates?

a. Not possible using NOR gates c. Six NOR gates will be used

b. given function must be implemented d. none of these

using OR and NAND gates

For Questions 24 to 28, refer to the circuit diagram shown below.

A T1

B T4

T2

C T5

D T3

24. What is the expression for T1?

a. A + B c. AB

b. A B d. (A B)’

25. What is the expression for T2?

a. BC c. (BC)’

b. (C B)’ d. (C B)

26. What is the expression for T3?

a. CD c. (CD)’

b. (C D) d. C + D

“Knowledge is of no value unless you put it into practice.”

- Heber J. Grant

27. What is the expression for T4?

a. ( A B)(BC) c. ( A B)(B C )

b. AB ( B C ) d. AB ( B C )

28. What is the expression for T5?

a. ( B C ) CD c. ( BC)(C D)

b. ( B C ) CD d. ( B C )(C D)

29. The simplest expression (in sum-of-products form) for the function F(A,B,C,D,E) =

∑m (1,3,5,7,8,12,15,18,19,22,23,24,27,28,31) is

a. ABE + CD’E + AB’D+ADE+BD’E’ c. ABE + CD’E + AB’D+A’DE+BD’E’

b. A’B’E + CDE + AB’D + ADE + BD’E’ d. A’B’E + CD’E + AB’D+ADE+BD’E’

30. Use the K-map to find the minimum sum of products of F(A,B,C,D) = ∏M (0,2,4,6,8,10,12,14)

a. F = D c. F = A’D

b. F = D’ d. none of these

31. Simplify the Expression (wx + yz)(w’y’+xz’) using Boolean Algebra:

a. w’x’y’ c. wx’z

b. wxz’ d. w’xz

32. Given the function F(a,b,c,d) = ∏M(1,3,5,9,12,14,15) determine its canonical form.

a. F = M1 + M3 + M5 + M9 + M12 + M14 + M15 c. F = m1m3m5m9m12m14m15

b. F = m1 + m3 + m5 + m9 + m12 + m14 + m15 d. F = M1M3M5M9M12M14M15

33. The behavior of this system depends upon the input signals at any instant of time and the

order in which the inputs change

a. synchronous combinational circuit c. asynchronous sequential circuit

b. synchronous sequential circuit d. asynchronous combinational circuit

For questions 34 to 40, refer to the behavior of the synchronous sequential circuit below. Assume

that the states are identified as the combination ABC.

“Knowledge is of no value unless you put it into practice.”

- Heber J. Grant

X

Y

D Q T Q J Q

A B C

Q Q K Q

CP

34. What is the next state for an input of 0 if the current state is 000?

a. 010 c. 110

b. 011 d. none of these

35. What is the next state for an input of 1 if the current state is 001?

a. 100 c. 101

b. 010 d. none of these

36. What is the next state for an input of 0 if the current state is 010?

a. 000 c. 100

b. 001 d. none of these

37. What is the next state for an input of 1 if the current state is 011?

a. 100 c. 110

b. 101 d. none of these

38. What is the next state for an input of 0 if the current state is 100?

a. 100 c. 111

b. 101 d. none of these

39. What is the next state for an input of 1 if the current state is 101?

a. 000 c. 110

b. 001 d. none of these

40. What is the next state for an input of 0 if the current state is 110?

a. 100 c. 110

b. 101 d. none of these

For questions 41 to 44, refer to the given J-K flip-flop excitation table below.

Line Q(t) Q(t + 1) J K

1 0 0

2 0 1

3 1 0

4 1 1

“Knowledge is of no value unless you put it into practice.”

- Heber J. Grant

41. In line 1 of the given table, what should be the value of K if J = 0?

a. 0 c. X

b. 1 d. undefined

42. In line 2 of the given table, what should be the value of K if J = 1?

a. 0 c. X

b. 1 d. undefined

43. In line 3 of the given table, what should be the value of J if K = 0?

a. 0 c. X

b. 1 d. undefined

44. In line 4 of the given table, what should be the value of J if K = 1?

a. 0 c. X

b. 1 d. undefined

45. It consists of a series connection of complementing flip-flops, with the output of each flip-flop

connected to the C input of the next higher order flip-flop.

a. binary synchronous counter c. binary asynchronous counter

b. binary ripple counter d. Johnson counter

46. This is a circular shift register with the complemented output of the last flip-flop connected to the

input of the first flip-flop.

a. universal register c. switch-tail ring counter

b. Johnson counter d. circular register counter

47. This is a type of counter that goes through a repeated sequence of N states. The sequence may

follow the binary count or may be any other arbitrary sequence.

a. add-by-N counter c. divide-by-N counter

b. subtract-by-N counter d. multiply-by-N counter

48. In this type of counter, clock pulses are applied to the inputs of all flip-flops. A common clock

triggers all flip-flops immediately

a. synchronous counter c. ring counter

b. ripple counter d. asynchronous counter

49. The master-slave is a pulse-triggered flip-flop and is indicated as such with a right angle symbol

called a ______________

a. dynamic input indicator c. postponed output indicator

b. static pulse indicator d. none of these

50. The functional relationships between the inputs, outputs, and flip-flop states of a sequential circuit

can be enumerated in a _______________

a. truth table c. logic function

b. excitation table d. none of these

“Knowledge is of no value unless you put it into practice.”

- Heber J. Grant

“Knowledge is of no value unless you put it into practice.”

- Heber J. Grant

You might also like

- Digital Electronics (Pc-Ee-402) MCQ With AnswersDocument11 pagesDigital Electronics (Pc-Ee-402) MCQ With AnswersSanjoy PathakNo ratings yet

- Logic Exam - Bank Questions - Assuit UniversityDocument10 pagesLogic Exam - Bank Questions - Assuit Universityعبدالرحمن العجانNo ratings yet

- DLD McqsDocument36 pagesDLD Mcqspunjabiangem100% (2)

- DEC - EXP-03Construction of MOSFET Logic GatesDocument15 pagesDEC - EXP-03Construction of MOSFET Logic GatesSifatNo ratings yet

- LOGIC - CIRCUITS Final Exam Q3 2009 - 2010 ANSWER KEY Ver 2003Document6 pagesLOGIC - CIRCUITS Final Exam Q3 2009 - 2010 ANSWER KEY Ver 2003Simon Gregory MabantaNo ratings yet

- LOGIC - CIRCUITS Final Exam Q4 2009 - 2010 ANSWER KEY PDFDocument6 pagesLOGIC - CIRCUITS Final Exam Q4 2009 - 2010 ANSWER KEY PDFNJ De GuzmanNo ratings yet

- LOGIC - CIRCUITS Final Exam Q2 2010 - 2011 Problems and Answer KeyDocument2 pagesLOGIC - CIRCUITS Final Exam Q2 2010 - 2011 Problems and Answer KeySimon Gregory Mabanta100% (1)

- Term1ComputerSc XI Set ADocument6 pagesTerm1ComputerSc XI Set ACall me kiraNo ratings yet

- Divine Word College of Calapan: Engineering and Architecture DepartmentDocument2 pagesDivine Word College of Calapan: Engineering and Architecture DepartmentGerald TiocsonNo ratings yet

- Exit Exam Questions Logic - Circuits - 1 q1 2010 - 2011 Answer KeyDocument3 pagesExit Exam Questions Logic - Circuits - 1 q1 2010 - 2011 Answer KeyKyle CatimbangNo ratings yet

- CPET21 ComputerSc Set1Document14 pagesCPET21 ComputerSc Set1R2k OfficialNo ratings yet

- Course Id 23311 Course Title - Digital LogicDocument3 pagesCourse Id 23311 Course Title - Digital LogicICIS CollegeNo ratings yet

- Slr-Eg - 9: Code NoDocument6 pagesSlr-Eg - 9: Code Noaksaltaf9137No ratings yet

- DEL Online Questions Unit I & IIDocument13 pagesDEL Online Questions Unit I & IIShanti GuruNo ratings yet

- Screenshot 2023-05-23Document6 pagesScreenshot 2023-05-23Nidhi NarayanNo ratings yet

- MCQ's DSP 201-300Document18 pagesMCQ's DSP 201-300Rohit NegiNo ratings yet

- Ugc Papers With AnsDocument171 pagesUgc Papers With Ansredhackerunknown07No ratings yet

- Digital Qbank LatestDocument16 pagesDigital Qbank LatestkhananuNo ratings yet

- Co 2019Document12 pagesCo 2019HARDIKSINH PARMARNo ratings yet

- Digital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Document4 pagesDigital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Vikash KumarNo ratings yet

- Ugc Net SolvedDocument39 pagesUgc Net SolvedRongeet SodhiNo ratings yet

- Deld McqsDocument25 pagesDeld McqsAniman XanderNo ratings yet

- Unit-1-2-3 Question Bank DEC 2131004Document2 pagesUnit-1-2-3 Question Bank DEC 2131004Amit KumarNo ratings yet

- Computer2010Document17 pagesComputer2010ViJaY HaLdErNo ratings yet

- Digital Electronics MCQDocument31 pagesDigital Electronics MCQSneha Singh100% (2)

- RRB Junior Engineer Electronics Mock Test QuestionsDocument31 pagesRRB Junior Engineer Electronics Mock Test QuestionsthirumalNo ratings yet

- HSST CsDocument12 pagesHSST CsBhavya SureshNo ratings yet

- FCP End Sem Exam July-2020Document10 pagesFCP End Sem Exam July-2020U20CH020 JERRY SVNITNo ratings yet

- CADocument11 pagesCAAnkita SondhiNo ratings yet

- MCQ DTMDocument7 pagesMCQ DTMOm PawarNo ratings yet

- Online Quiz 1Document9 pagesOnline Quiz 1AngelicaNo ratings yet

- Analog and Digital Electronics Question PaperDocument5 pagesAnalog and Digital Electronics Question PaperSubh DasNo ratings yet

- Final QuestionDocument5 pagesFinal QuestionsatishNo ratings yet

- Imp DlaDocument4 pagesImp DlaLaxmiNo ratings yet

- DLC MCQDocument61 pagesDLC MCQYuvaraj ShanNo ratings yet

- ISRO CS 2016-Watermark - pdf-80Document6 pagesISRO CS 2016-Watermark - pdf-80Govind VijayNo ratings yet

- Refresher - Electronics (Comp)Document7 pagesRefresher - Electronics (Comp)Creation YourNo ratings yet

- Singnal and SystemDocument67 pagesSingnal and Systemjohn cenaNo ratings yet

- CSD Module 1 Question Bank SolvedDocument16 pagesCSD Module 1 Question Bank SolvedSaket GoluNo ratings yet

- C 100 For I 1 To N Do For J 1 To N Do (Temp A (I) (J) + C A (I) (J) A (J) (I) A (J) (I) Temp - C) For I 1 To N Do For J 1 To N Do Output (A (I) (J) )Document5 pagesC 100 For I 1 To N Do For J 1 To N Do (Temp A (I) (J) + C A (I) (J) A (J) (I) A (J) (I) Temp - C) For I 1 To N Do For J 1 To N Do Output (A (I) (J) )Utkarsh ShuklaNo ratings yet

- KRL Institute of Technology, Kahuta: CIT-2 Year Subject: Digital & Industrial Electronics Multiple Choice QuestionsDocument7 pagesKRL Institute of Technology, Kahuta: CIT-2 Year Subject: Digital & Industrial Electronics Multiple Choice QuestionsHamza MustafaNo ratings yet

- MCA Lateral Exam: Key Concepts for C, C++, Data Structures, Algorithms & Computer NetworksDocument9 pagesMCA Lateral Exam: Key Concepts for C, C++, Data Structures, Algorithms & Computer NetworksDanny JNo ratings yet

- Question Papers and Answer Keys PG UpdatedDocument873 pagesQuestion Papers and Answer Keys PG Updateds_samitNo ratings yet

- UNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Document18 pagesUNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Deepak NaiduNo ratings yet

- Computer Graphics ++Document189 pagesComputer Graphics ++Harry JackNo ratings yet

- Gate CS 2005Document12 pagesGate CS 2005reqtechNo ratings yet

- QaDocument11 pagesQaAjith HeroNo ratings yet

- Digital Electronics Conversion and Logic ConceptsDocument2 pagesDigital Electronics Conversion and Logic ConceptssenthilkumarNo ratings yet

- Kec 302 Digital System DesignDocument2 pagesKec 302 Digital System DesignAditya KasaudhanNo ratings yet

- II Mid Bits For StudentsDocument9 pagesII Mid Bits For StudentsSurya MukeshNo ratings yet

- Bca 101Document4 pagesBca 101Avirup ShomeNo ratings yet

- Computer FundamentalsDocument7 pagesComputer FundamentalsLucasNo ratings yet

- Mid Term 15,16 AnswerDocument13 pagesMid Term 15,16 AnswerSofwan JuewekNo ratings yet

- Digital Electronics - MCQsDocument38 pagesDigital Electronics - MCQsAbhay ShuklaNo ratings yet

- Test I. Instructions: Read The Questions Carefully and Write The Letter of The Correct Answer On The SpaceDocument4 pagesTest I. Instructions: Read The Questions Carefully and Write The Letter of The Correct Answer On The SpaceTrending 2019No ratings yet

- M.O.G CSC 120 QuestionsDocument6 pagesM.O.G CSC 120 QuestionsAjayi EmmanuelNo ratings yet

- Gate Cse 2005Document22 pagesGate Cse 2005Aditya RaiNo ratings yet

- Bca Bca 101 Digital Electronics 2009Document4 pagesBca Bca 101 Digital Electronics 2009Tridib BhuniaNo ratings yet

- Jeppiaar Institute of Technology: Department OF Electronics and Communication EngineeringDocument35 pagesJeppiaar Institute of Technology: Department OF Electronics and Communication EngineeringPartha SarkarNo ratings yet

- Detailed Syllabus of ISRO Technical Assistant Electronics (ECE)Document6 pagesDetailed Syllabus of ISRO Technical Assistant Electronics (ECE)LoknathNo ratings yet

- Digital Circuits Combinational CircuitsDocument138 pagesDigital Circuits Combinational CircuitsSagar AgarwalNo ratings yet

- A Low-Power Delay Buffer Using Gated Driver TreeDocument8 pagesA Low-Power Delay Buffer Using Gated Driver TreeJudeesh JacobNo ratings yet

- Analog VLSI Test PaperDocument1 pageAnalog VLSI Test Paperwaibhav sonewaneNo ratings yet

- 27 Costas Loop ReceiverDocument3 pages27 Costas Loop Receiverkarthik reddyNo ratings yet

- L293D Motor Driver ICDocument4 pagesL293D Motor Driver ICAilapaka ManojNo ratings yet

- Nodal AnalysisDocument43 pagesNodal AnalysisSakaiking InhellNo ratings yet

- Cascode AmplifierDocument6 pagesCascode AmplifierGp Gonzales0% (1)

- Assignment 2Document5 pagesAssignment 2Kavinesh AnanthanNo ratings yet

- Week 9 - Timing ConstraintsDocument18 pagesWeek 9 - Timing Constraints서종현No ratings yet

- This Set of Digital Electronic1-Merged-merged-mergedDocument1,802 pagesThis Set of Digital Electronic1-Merged-merged-mergedMadhura PansareNo ratings yet

- 74LS573Document6 pages74LS573Sinué RamírezNo ratings yet

- Simulation LabDocument17 pagesSimulation LabARVINDNo ratings yet

- Dual D-type positive edge-triggered flip-flop low power SchottkyDocument3 pagesDual D-type positive edge-triggered flip-flop low power Schottkygd8uj123100% (1)

- Power transistor specifications and data sheetDocument1 pagePower transistor specifications and data sheetAngel Simo MoralesNo ratings yet

- Bipolar TransistorDocument9 pagesBipolar TransistorJitendra DubeyNo ratings yet

- ESE 568: Mixed Signal Design and Modeling Lecture Outline: Simplified For Hand AnalysisDocument13 pagesESE 568: Mixed Signal Design and Modeling Lecture Outline: Simplified For Hand AnalysisVarun SinghalNo ratings yet

- Basic GateDocument5 pagesBasic Gatemsjunaid02No ratings yet

- B1 Ece2002 50030 50290 50369Document4 pagesB1 Ece2002 50030 50290 50369NanduNo ratings yet

- Bridge amplifier circuit design and component layoutDocument2 pagesBridge amplifier circuit design and component layoutatomo333No ratings yet

- Ass 1Document2 pagesAss 1Sai Vishnu RNo ratings yet

- Logic Gates and Truth Tables ExplainedDocument6 pagesLogic Gates and Truth Tables ExplainedHarshal AkhouriNo ratings yet

- CE8301 SeriesDocument11 pagesCE8301 SeriesWilly NodaNo ratings yet

- Frequency Response of A CMOS Common-Source Amplifier: Experiment # 5Document10 pagesFrequency Response of A CMOS Common-Source Amplifier: Experiment # 5Md. Sadique SheikhNo ratings yet

- Electronics IIDocument13 pagesElectronics IIDr. Neha KondalNo ratings yet

- NetworkDocument184 pagesNetworkjohn cenaNo ratings yet

- Utc 2030Document14 pagesUtc 2030Jose M PeresNo ratings yet

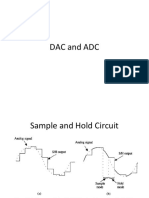

- ADCDACDocument180 pagesADCDACKireetiNo ratings yet