100% found this document useful (1 vote)

561 views57 pagesDigital Electronics Lab Manual

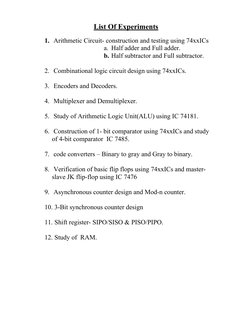

This document provides instructions and guidelines for students taking a Digital Electronics lab course. It outlines 12 experiments involving digital logic circuits that students will complete. The experiments include constructing half/full adders and subtractors, combinational logic circuits, encoders and decoders, multiplexers and demultiplexers, and various basic logic gates and flip-flops. The document provides details on building and testing circuits using a breadboard, as well as safety guidelines and expectations for laboratory notebooks.

Uploaded by

Computer Sc & BCA DepartmentCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOCX, PDF, TXT or read online on Scribd

100% found this document useful (1 vote)

561 views57 pagesDigital Electronics Lab Manual

This document provides instructions and guidelines for students taking a Digital Electronics lab course. It outlines 12 experiments involving digital logic circuits that students will complete. The experiments include constructing half/full adders and subtractors, combinational logic circuits, encoders and decoders, multiplexers and demultiplexers, and various basic logic gates and flip-flops. The document provides details on building and testing circuits using a breadboard, as well as safety guidelines and expectations for laboratory notebooks.

Uploaded by

Computer Sc & BCA DepartmentCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOCX, PDF, TXT or read online on Scribd

- The Laboratory Notebook: Details the procedures for maintaining a laboratory notebook necessary for recording electronic experiments.

- Introduction to Digital Electronics: Introduction to digital electronics experiments with guidelines for conducting lab sessions responsibly.

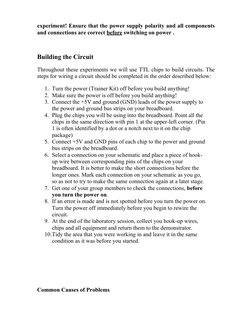

- The Breadboard: Explains the structure and usage of the breadboard, including safety instructions essential for practical electronics work.

- Common Causes of Problems: Lists common practical issues faced during experiments with suggested solutions for troubleshooting.

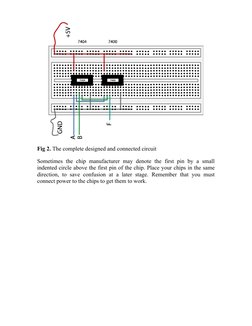

- Building the Circuit: Instructions for starting and completing electronic circuit construction, essential for correctly executing lab tasks.

- Logic Circuit Example: Provides a sample logic circuit using Boolean function implementation as a practical example for students.

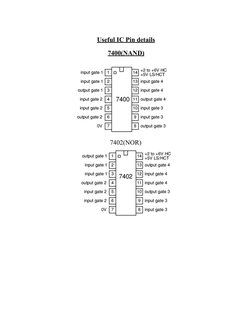

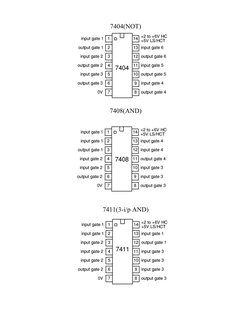

- Useful IC Pin Details: Illustrates pin configurations and functions for commonly used integrated circuits (ICs) like NAND, NOR gates.

- Experiment: Half/Full Adder & Half/Full Subtractor: Describes objectives and procedures to verify the operation of half and full adders/subtractors using basic gates.

- Experiment: Combinational Logic Design: Focuses on designing and verifying combinational logic circuits to solve typical logical conditions.

- Experiment: MUX/DEMUX: Procedures for understanding and applying multiplexers and demultiplexers in digital circuits.

- Experiment: Binary to Gray Code Conversion: Details conversion techniques between binary numbers and gray codes using digital logic gates.

- Experiment: Comparators: Covers comparison operations using logic gates and related integrated circuits like the 7485.

- Experiment: Random Access Memory: Guidelines for constructing and testing RAM circuits, including reading and writing processes.

- Experiment: Shift Registers: Demonstrates the functionality of various shift registers, extending their application in digital systems.

- Experiment: Arithmetic Logic Unit: Explores the arithmetic and logic operations handled by ALUs, using specific ICs like the 74181.

- Experiment: Asynchronous Counter Design: Outlines the design and implementation of 3-bit asynchronous counters, including Mod-N variations.

- Experiment: Synchronous Counter Design: Step-by-step instruction to create a 3-bit synchronous counter and verify its operation.

- Experiment: Flip-Flop: Describes the verification process for various types of flip-flops like RS, D, and JK using logic gates.

- Experiment: Encoder and Decoder: Procedures to understand and verify the functionality between encoders and decoders in digital systems.