Professional Documents

Culture Documents

G3R20MT17K

Uploaded by

PalmCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

G3R20MT17K

Uploaded by

PalmCopyright:

Available Formats

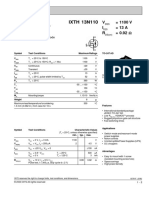

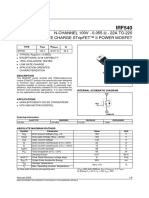

G3R20MT17K TM

1700 V 20 mΩ SiC MOSFET

Silicon Carbide MOSFET VDS = 1700 V

N-Channel Enhancement Mode RDS(ON)(Typ.) = 20 mΩ

ID (TC = 100°C) = 67 A

Features Package

• G3R™ Technology with +15 V Gate Drive D

• Softer RDS(ON) v/s Temperature Dependency

• LoRing™ - Electromagnetically Optimized Design G

• Smaller RG(INT) and Lower QG RoHS

• Low Device Capacitances (COSS, CRSS) KS S

• Superior Cost-Performance Index D = Drain

• Robust Body Diode with Low VF and Low QRR G = Gate

• Industry-Leading UIL & Short-Circuit Robustness TO-247-4 S = Source REACH

KS = Kelvin Source

Advantages Applications

• Compatible with Commercial Gate Drivers • EV Fast Charging

• Low Conduction Losses at all Temperatures • Solar Inverters

• Reduced Ringing • Industrial Motor Drives

• Faster and More Efficient Switching • Transportation

• Lesser Switching Spikes and Lower Losses • Industrial Power Supply

• Better Power Density and System Efficiency • Smart Grid and HVDC

• Ease of Paralleling without Thermal Runaway • Induction Heating and Welding

• Superior Robustness and System Reliability • Pulsed Power

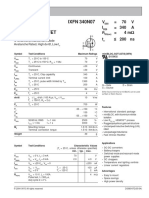

Absolute Maximum Ratings (At TC = 25°C Unless Otherwise Stated)

Parameter Symbol Conditions Values Unit Note

Drain-Source Voltage VDS(max) VGS = 0 V, ID = 100 µA 1700 V

Gate-Source Voltage (Dynamic) VGS(max) -10 / +20 V

Gate-Source Voltage (Static) VGS(op) Recommended Operation -5 / +15 V

TC = 25°C, VGS = -5 / +15 V 95

Continuous Forward Current ID TC = 100°C, VGS = -5 / +15 V 67 A Fig. 15

TC = 135°C, VGS = -5 / +15 V 49

Pulsed Drain Current ID(pulse) tP ≤ 3µs, D ≤ 1%, VGS = 15 V, Note 1 250 A Fig. 14

Power Dissipation PD Tc = 25°C 569 W Fig. 16

Non-Repetitive Avalanche Energy EAS L = 2.0 mH, IAS = 37.5 A 1410 mJ

Operating and Storage Temperature Tj , Tstg -55 to 175 °C

Thermal/Package Characteristics

Values

Parameter Symbol Conditions Unit Note

Min. Typ. Max.

Thermal Resistance, Junction - Case RthJC 0.20 0.26 °C/W Fig. 13

Weight WT 6.2 g

Mounting Torque TM Screws to Heatsink 1.1 Nm

Note 1: Pulse Width tP Limited by Tj(max)

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K.pdf Page 1 of 14

G3R20MT17K TM

1700 V 20 mΩ SiC MOSFET

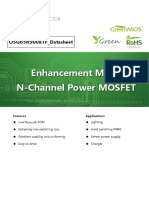

Electrical Characteristics (At TC = 25°C Unless Otherwise Stated)

Values

Parameter Symbol Conditions Unit Note

Min. Typ. Max.

Drain-Source Breakdown Voltage VDSS VGS = 0 V, ID = 100 µA 1700 V

Zero Gate Voltage Drain Current IDSS VDS = 1700 V, VGS = 0 V 1 µA

VDS = 0 V, VGS = 20 V 100

Gate Source Leakage Current IGSS nA

VDS = 0 V, VGS = -10 V -100

VDS = VGS, ID = 60.0 mA 1.8 2.70

Gate Threshold Voltage VGS(th) V Fig. 9

VDS = VGS, ID = 60.0 mA, Tj = 175°C 1.90

VDS = 10 V, ID = 75 A 37.9

Transconductance gfs S Fig. 4

VDS = 10 V, ID = 75 A, Tj = 175°C 39.0

VGS = 15 V, ID = 75 A 20 28

Drain-Source On-State Resistance RDS(ON) mΩ Fig. 5-8

VGS = 15 V, ID = 75 A, Tj = 175°C 45

Input Capacitance Ciss 7620

Output Capacitance Coss 205 pF Fig. 11

Reverse Transfer Capacitance Crss 36.4

Coss Stored Energy Eoss 136 µJ Fig. 12

VDS = 1000 V, VGS = 0 V

Coss Stored Charge Qoss f = 1 MHz, VAC = 25mV 410 nC

Effective Output Capacitance (Energy

Co(er) 272

Related)

pF Note 2

Effective Output Capacitance (Time

Co(tr) 410

Related)

Gate-Source Charge Qgs VDS = 1000 V, VGS = -5 / +15 V 77

Gate-Drain Charge Qgd ID = 75 A 90 nC Fig. 10

Total Gate Charge Qg Per IEC607478-4 256

Internal Gate Resistance RG(int) f = 1 MHz, VAC = 25 mV 1.8 Ω

Turn-On Switching Energy

EOn 892

(Body Diode) Tj = 25°C, VGS = -5/+15V, RG(ext) = 0.5 Ω, L

µJ Fig. 22,26

Turn-Off Switching Energy = 32.0 µH, ID = 75 A, VDD = 1200 V

EOff 490

(Body Diode)

Turn-On Delay Time td(on) 52

Rise Time tr VDD = 1200 V, VGS = -5/+15V 32

RG(ext) = 0.5 Ω, L = 32.0 µH, ID = 75 A ns Fig. 24

Turn-Off Delay Time td(off) Timing relative to VDS, Inductive load 38

Fall Time tf 24

*The chip technology was characterized up to 200 V/ns. The measured dV/dt was limited by measurement test setup and package.

Note 2: Co(er), a lumped capacitance that gives same stored energy as C OSS while V DS is rising from 0 to 1000V.

Co(tr), a lumped capacitance that gives same charging times as COSS while V DS is rising from 0 to 1000V.

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K.pdf Page 2 of 14

G3R20MT17K TM

1700 V 20 mΩ SiC MOSFET

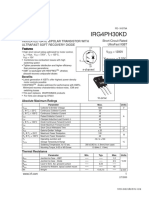

Reverse Diode Characteristics

Values

Parameter Symbol Conditions Unit Note

Min. Typ. Max.

VGS = -5 V, ISD = 37 A 4.4

Diode Forward Voltage VSD V Fig. 17-18

VGS = -5 V, ISD = 37 A, Tj = 175°C 4.2

Continuous Diode Forward Current IS VGS = -5 V, Tc = 100°C 58 A

Diode Pulse Current IS(pulse) VGS = -5 V, Note 1 232 A

Reverse Recovery Time trr 63 ns

VGS = -5 V, ISD = 75 A, VR = 1200 V

Reverse Recovery Charge Qrr 752 nC

dif/dt = 800 A/µs, Tj = 25°C

Peak Reverse Recovery Current Irrm 21 A

Reverse Recovery Time trr 108 ns

VGS = -5 V, ISD = 75 A, VR = 1200 V

Reverse Recovery Charge Qrr 2820 nC

dif/dt = 800 A/µs, Tj = 175°C

Peak Reverse Recovery Current Irrm 45 A

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K.pdf Page 3 of 14

G3R20MT17K TM

1700 V 20 mΩ SiC MOSFET

Figure 1: Output Characteristics (Tj = 25°C) Figure 2: Output Characteristics (Tj = 175°C)

ID = f(VDS, VGS); tP = 250 µs ID = f(VDS, VGS); tP = 250 µs

Figure 3: Output Characteristics (VGS = 15 V) Figure 4: Transfer Characteristics (VDS = 10 V)

ID = f(VDS, T);

j tP = 250 µs ID = f(VGS, T);

j tP = 100 µs

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K.pdf Page 4 of 14

G3R20MT17K TM

1700 V 20 mΩ SiC MOSFET

Figure 5: On-State Resistance v/s Temperature Figure 6: On-State Resistance v/s Drain Current

RDS(ON) = f(T,j VGS); tP = 250 µs; ID = 75 A RDS(ON) = f(T,I

j D); tP = 250 µs; VGS = 15 V

Figure 7: Normalized On-State Resistance v/s Temperature Figure 8: On-State Resistance v/s Gate Voltage

RDS(ON) = f(T);

j tP = 250 µs; ID = 75 A; VGS = 15 V RDS(ON) = f(T,V

j GS); tP = 250 µs; I D = 75 A

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K.pdf Page 5 of 14

G3R20MT17K TM

1700 V 20 mΩ SiC MOSFET

Figure 9: Threshold Voltage Characteristics Figure 10: Gate Charge Characteristics

VGS(th) = f(T);

j VDS = VGS; ID = 60.0 mA ID = 75 A; VDS = 1000 V; Tc = 25°C

Figure 11: Capacitance v/s Drain-Source Voltage Figure 12: Output Capacitor Stored Energy

f = 1 MHz; VAC = 25mV Eoss = f(VDS)

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K.pdf Page 6 of 14

G3R20MT17K TM

1700 V 20 mΩ SiC MOSFET

Figure 13: Transient Thermal Impedance Figure 14: Safe Operating Area (Tc = 25°C)

Zth,jc = f(tP,D); D = tP/T ID = f(VDS, tP); Tj ≤ 175°C; D = 0

Figure 15: Current De-rating Curve Figure 16: Power De-rating Curve

ID = f(TC); Tj ≤ 175°C PD = f(TC); Tj ≤ 175°C

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K.pdf Page 7 of 14

G3R20MT17K TM

1700 V 20 mΩ SiC MOSFET

Figure 17: Body Diode Characteristics (Tj = 25°C) Figure 18: Body Diode Characteristics (Tj = 175°C)

ID = f(VDS, VGS); tP = 250 µs ID = f(VDS, VGS); tP = 250 µs

Figure 19: Third Quadrant Characteristics (Tj = 25°C) Figure 20: Third Quadrant Characteristics (Tj = 175°C)

ID = f(VDS, VGS); tP = 250 µs ID = f(VDS, VGS); tP = 250 µs

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K.pdf Page 8 of 14

G3R20MT17K TM

1700 V 20 mΩ SiC MOSFET

Figure 21: Inductive Switching Energy v/s Drain Current Figure 22: Inductive Switching Energy v/s Drain Current

(VDD = 1000V) (VDD = 1200V)

Tj = 25°C; VGS = -5/+15V; RG(ext) = 0.5 Ω; L = 32.0µH Tj = 25°C; VGS = -5/+15V; RG(ext) = 0.5 Ω; L = 32.0µH

Figure 23: Inductive Switching Energy v/s RG(ext) Figure 24: Switching Time v/s RG(ext)

(VDD = 1200V) (VDD = 1200V)

Tj = 25°C; VGS = -5/+15V; IDS = 75 A; L = 32.0µH Tj = 25°C; VGS = -5/+15V; IDS = 75 A; L = 32.0µH

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K.pdf Page 9 of 14

G3R20MT17K TM

1700 V 20 mΩ SiC MOSFET

Figure 25: Inductive Switching Energy v/s Temperature Figure 26: dV/dt v/s RG(ext)

(VDD = 1200V) (VDD = 1200V)

Tj = 25°C; VGS = -5/+15V; RG(ext) = 0.5 Ω; IDS = 75 A; L = 32.0µH Tj = 25°C; VGS = -5/+15V; IDS = 75 A; L = 32.0µH

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K.pdf Page 10 of 14

G3R20MT17K TM

1700 V 20 mΩ SiC MOSFET

Gate Charge Circuit Gate Charge Waveform

VDS

VGS

Gate Voltage (VGS)

D.U.T RLoad

ID VDD

IG(cont)

QGS QGD

Gate Charge (QG)

Switching Time Circuit Switching Time Waveform

90%

Same device as the D.U.T.

LLoad

-5 V VGS 10%

VDS

10% 10%

VDS

VGS

VDD

D.U.T.

RG

90% 90%

ID td(on) td(off)

tr tf

ton toff

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K.pdf Page 11 of 14

G3R20MT17K TM

1700 V 20 mΩ SiC MOSFET

Switching Energy Circuit Switching Energy Waveform

EON = ∫ ID x VDS x dt EOFF = ∫ ID x VDS x dt

Same device as the D.U.T.

LLoad

-5 V Irr

VDS

VDS

VGS

VDD

D.U.T.

RG

ID

IDS

Reverse Recovery Circuit Reverse Recovery Waveform

D.U.T.

LLoad IF

-5 V

trr

IF

0 Level

VGS 90%

VDD

Same device

as the D.U.T. dIrr/dt in 10%

RG Irr

to 90% range

10%

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K.pdf Page 12 of 14

G3R20MT17K TM

1700 V 20 mΩ SiC MOSFET

Package Dimensions

TO-247-4 Package Outline

0.62(15.75) 0.19(4.83)

0.516(13.10)

0.635(16.13) 0.205(5.21)

0.557(14.15)

0.5(12.7)

0.216(5.49) 0.487(12.38)

0.236(6.0) 0.075(1.91)

0.25(6.35) 0.529(13.43)

0.085(2.16)

0.037(0.95)

0.049(1.25)

0.237(6.04)

0.248(6.30)

0.145(3.68)

0.2(5.10)

0.64(16.25)

0.695(17.65)

Ø 0.138(3.51)

0.118(3.0) Ø 0.144(3.65)

0.917(23.30)

0.929(23.60)

Ø 0.283(7.18) REF

0.093(2.35)

0.104(2.65)

0.09(2.29)

0.1(2.54)

0.156(3.97)

0.172(4.37)

0.681(17.31)

0.701(17.82)

0.1(2.54) BSC 0.021(0.55)

0.027(0.68)

0.2 (5.08) BSC 0.042(1.07) 0.094(2.39)

0.042(1.07) 0.063(1.60) 0.116(2.94)

0.052(1.33)

Recommended Solder Pad Layout Package View

Case(D)

Ø 0.088(2.24)

Ø 0.067(1.7)

0.1(2.54)

G

0.1(2.54) D

0.2(5.08)

S KS

NOTE

1. CONTROLLED DIMENSION IS INCH. DIMENSION IN BRACKET IS MILLIMETER.

2. DIMENSIONS DO NOT INCLUDE END FLASH, MOLD FLASH, MATERIAL PROTRUSIONS.

3. THE SOURCE AND KELVIN-SOURCE PINS ARE NOT INTERCHANGABLE. THEIR EXCHANGE MIGHT LEAD TO MALFUNCTION.

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K.pdf Page 13 of 14

G3R20MT17K TM

1700 V 20 mΩ SiC MOSFET

Compliance

RoHS Compliance

The levels of RoHS restricted materials in this product are below the maximum concentration values (also referred to as the threshold

limits) permitted for such substances, or are used in an exempted application, in accordance with EU Directive 2011/65/EC (RoHS 2), as

adopted by EU member states on January 2, 2013 and amended on March 31, 2015 by EU Directive 2015/863. RoHS Declarations for this

product can be obtained from your GeneSiC representative.

REACH Compliance

REACH substances of high concern (SVHCs) information is available for this product. Since the European Chemical Agency (ECHA) has

published notice of their intent to frequently revise the SVHC listing for the foreseeable future, please contact a GeneSiC representative to

insure you get the most up-to-date REACH SVHC Declaration. REACH banned substance information (REACH Article 67) is also available

upon request.

Disclaimer

GeneSiC Semiconductor, Inc. reserves right to make changes to the product specifications and data in this document without notice.

GeneSiC disclaims all and any warranty and liability arising out of use or application of any product. No license, express or implied to any

intellectual property rights is granted by this document.

Unless otherwise expressly indicated, GeneSiC products are not designed, tested or authorized for use in life-saving, medical, aircraft

navigation, communication, air traffic control and weapons systems, nor in applications where their failure may result in death, personal

injury and/or property damage.

Related Links

• SPICE Models: https://www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K_SPICE.zip

• PLECS Models: https://www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K_PLECS.zip

• CAD Models: https://www.genesicsemi.com/sic-mosfet/G3R20MT17K/G3R20MT17K_3D.zip

• Gate Driver Reference: https://www.genesicsemi.com/technical-support

• Evaluation Boards: https://www.genesicsemi.com/technical-support

• Reliability: https://www.genesicsemi.com/reliability

• Compliance: https://www.genesicsemi.com/compliance

• Quality Manual: https://www.genesicsemi.com/quality

Revision History

• Rev 21/May: Updated switching time and switching energy data

• Supersedes: Rev 20/Jun, Rev 20/Sep, Rev 21/Feb

www.genesicsemi.com/sic-mosfet/

Rev 21/May Published by GeneSiC Semiconductor, Inc.

Copyright© 2021 GeneSiC Semiconductor Inc. 43670 Trade Center Place Suite 155, Dulles, VA 20166; USA

All Rights Reserved. Page 14 of 14

You might also like

- Mosfet Power Transistor 64a 1200VDS G3R20MT12N-2449153Document15 pagesMosfet Power Transistor 64a 1200VDS G3R20MT12N-2449153Ramón MartinezNo ratings yet

- HCS65R320SDocument7 pagesHCS65R320SnareshNo ratings yet

- 70R900P MagnaChip PDFDocument10 pages70R900P MagnaChip PDFAjay KumarNo ratings yet

- 70V, 158A N-Channel Trench Process Power MOSFET: General Description CS48N18Document5 pages70V, 158A N-Channel Trench Process Power MOSFET: General Description CS48N18Valladares A JJNo ratings yet

- Infineon IMW120R140M1H DataSheet v02 - 01 ENDocument17 pagesInfineon IMW120R140M1H DataSheet v02 - 01 ENhope1678481280No ratings yet

- Infineon IRFP4229 DataSheet v01 - 01 ENDocument9 pagesInfineon IRFP4229 DataSheet v01 - 01 ENRoni Div MasterphpNo ratings yet

- MMD65R900Q MagnaChipDocument10 pagesMMD65R900Q MagnaChipSius TécnicaNo ratings yet

- Silicon Carbide Power MOSFET C3M MOSFET Technology: N-Channel Enhancement ModeDocument10 pagesSilicon Carbide Power MOSFET C3M MOSFET Technology: N-Channel Enhancement Modealllim88No ratings yet

- AP65SL190AI AdvancedPowerElectronicsDocument6 pagesAP65SL190AI AdvancedPowerElectronicsAkhmad Isnaeni RamdaniNo ratings yet

- HY3906Document11 pagesHY3906Daniel LescanoNo ratings yet

- FDP8443Document7 pagesFDP8443Semut criminalsNo ratings yet

- Standard Power MOSFET: IRFP 254 V 250 V I 23 A R 0.14Document2 pagesStandard Power MOSFET: IRFP 254 V 250 V I 23 A R 0.14Fran Javi Vila DiazNo ratings yet

- IXTH13N110Document3 pagesIXTH13N110Morteza JafarzadehNo ratings yet

- Datasheet 3Document8 pagesDatasheet 3RAMESH JUNJUNo ratings yet

- UF3N170400B7S Data SheetDocument10 pagesUF3N170400B7S Data SheetBruna MullaNo ratings yet

- Infineon IMZ120R030M1H DataSheet v02 - 02 ENDocument17 pagesInfineon IMZ120R030M1H DataSheet v02 - 02 ENKostas GekasNo ratings yet

- Pin Description Features: N-Channel Enhancement Mode MosfetDocument10 pagesPin Description Features: N-Channel Enhancement Mode MosfetBrahim SalahNo ratings yet

- Megamos Fet: Irfp 470 V 500 V I 24 A R 0.23Document2 pagesMegamos Fet: Irfp 470 V 500 V I 24 A R 0.23Plat RNo ratings yet

- Hiperfet Power Mosfets Isoplus247 Ixfr 70N15: (Electrically Isolated Backside)Document3 pagesHiperfet Power Mosfets Isoplus247 Ixfr 70N15: (Electrically Isolated Backside)William moreNo ratings yet

- Hy1707p HooyiDocument10 pagesHy1707p Hooyimarcos crNo ratings yet

- 60 N 12Document10 pages60 N 12Saul MuñozNo ratings yet

- K3478N HMSDocument9 pagesK3478N HMSOscar BarronNo ratings yet

- MMF60R360Q: 600V 0.36 N-Channel MOSFETDocument10 pagesMMF60R360Q: 600V 0.36 N-Channel MOSFETMichael Alejandro BastidasNo ratings yet

- Littelfuse Discrete MOSFETs N-Channel HiPerFETs IX-1856371Document7 pagesLittelfuse Discrete MOSFETs N-Channel HiPerFETs IX-1856371basheer almetwakelNo ratings yet

- RU6888 Mosfet: N-Channel Advanced Power MOSFETDocument12 pagesRU6888 Mosfet: N-Channel Advanced Power MOSFETamskroud brahimNo ratings yet

- Standard Power MOSFET: N-Channel Enhancement ModeDocument5 pagesStandard Power MOSFET: N-Channel Enhancement ModetvsamsungjpNo ratings yet

- IXFH40N50Q2Document5 pagesIXFH40N50Q2gustavo jesus JimenezNo ratings yet

- IRLR2905Z IRLU2905Z: Automotive MosfetDocument11 pagesIRLR2905Z IRLU2905Z: Automotive MosfetnaughtybigboyNo ratings yet

- Truesemi-TSD5N65M C382376Document10 pagesTruesemi-TSD5N65M C382376carlos riveraNo ratings yet

- MMIS60R900P: 600V 0.9 N-Channel MOSFETDocument10 pagesMMIS60R900P: 600V 0.9 N-Channel MOSFETAlejadro FierroNo ratings yet

- STP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetDocument8 pagesSTP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetCarlos A AvilaNo ratings yet

- UF3C065040K3S Data SheetDocument11 pagesUF3C065040K3S Data Sheetsultaniwahid240No ratings yet

- MME70R380P: 700V 0.38 N-Channel MOSFETDocument10 pagesMME70R380P: 700V 0.38 N-Channel MOSFETLeandro RoldanNo ratings yet

- Infineon IRL3705N DS v01 - 02 ENDocument9 pagesInfineon IRL3705N DS v01 - 02 ENFrancisco Mendoza BalderasNo ratings yet

- IRF540ZPBFDocument12 pagesIRF540ZPBFJose M PeresNo ratings yet

- Enhancement Mode N-Channel Power MOSFET: OSG65R900xTFDocument10 pagesEnhancement Mode N-Channel Power MOSFET: OSG65R900xTFCube7 Geronimo100% (1)

- Ixfh 12N100FDocument2 pagesIxfh 12N100FAnonymous lQyR2IWNo ratings yet

- CRJQ190N65GCFDocument9 pagesCRJQ190N65GCFVadim PopovichNo ratings yet

- STD 1703 LDocument10 pagesSTD 1703 LMatNo ratings yet

- Huf76633S3St - F085: N-Channel Logic Level Ultrafet Power MosfetDocument7 pagesHuf76633S3St - F085: N-Channel Logic Level Ultrafet Power MosfetJose cuelloNo ratings yet

- TSM60NB190CF A1612-1143360Document7 pagesTSM60NB190CF A1612-1143360abel sanchezNo ratings yet

- Fdd9407L - F085: N-Channel Logic Level Powertrench MosfetDocument7 pagesFdd9407L - F085: N-Channel Logic Level Powertrench Mosfetonis1 onis1No ratings yet

- Hy1906b Hooyi PDFDocument11 pagesHy1906b Hooyi PDFJose Antonio Ramos MuñosNo ratings yet

- P-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocument8 pagesP-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataAbel RodriguezNo ratings yet

- UltraFast IGBT with Soft Recovery Diode Optimized for Motor ControlDocument10 pagesUltraFast IGBT with Soft Recovery Diode Optimized for Motor ControlFerney Martinez RomeroNo ratings yet

- Coolmos Power Transistor: Features Product SummaryDocument10 pagesCoolmos Power Transistor: Features Product Summaryاحسن طاہرNo ratings yet

- IRFR4105Z IRFU4105Z: Automotive MosfetDocument11 pagesIRFR4105Z IRFU4105Z: Automotive MosfetRavi JagtianiNo ratings yet

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocument8 pagesN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataErroz RosadiNo ratings yet

- Ir53h420 Mosfet1Document9 pagesIr53h420 Mosfet1Gilson Mendes SilvaNo ratings yet

- AUIRLR3705Z: FeaturesDocument13 pagesAUIRLR3705Z: FeaturesGanNo ratings yet

- IRFB4227PBF Infineon Datasheet 9782845Document3 pagesIRFB4227PBF Infineon Datasheet 9782845IvanNo ratings yet

- 60R580P MagnaChipDocument10 pages60R580P MagnaChipAlfredo Valencia RodriguezNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument5 pagesAdvanced Power Electronics Corp.: DescriptionVladimir DoyminNo ratings yet

- APM6006NFPC-TUGDocument11 pagesAPM6006NFPC-TUGx6ricardo6xNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFRubenNo ratings yet

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectNo ratings yet

- Irf 540Document8 pagesIrf 540Tom TweedleNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- ITL9-1Document4 pagesITL9-1PalmNo ratings yet

- Service Experience 2023Document37 pagesService Experience 2023신영호No ratings yet

- Effects of Advanced Injection Timing On PerformancDocument6 pagesEffects of Advanced Injection Timing On PerformancPalmNo ratings yet

- F AlmabouadaDocument5 pagesF AlmabouadaPalmNo ratings yet

- 2SA1072Document2 pages2SA1072PalmNo ratings yet

- Us 4818916Document10 pagesUs 4818916PalmNo ratings yet

- RF PaperDocument7 pagesRF PaperPalmNo ratings yet

- PESC02 Sea Level Failuresof Power MOSFETsDocument7 pagesPESC02 Sea Level Failuresof Power MOSFETsPalmNo ratings yet

- AN3025Document2 pagesAN3025PalmNo ratings yet

- Ceramic RF Power CapacitorsDocument2 pagesCeramic RF Power CapacitorsPalmNo ratings yet

- Journal of Power and Energy Systems: Evolution and Future Trend of Large Frame Gas Turbine For Power GenerationDocument10 pagesJournal of Power and Energy Systems: Evolution and Future Trend of Large Frame Gas Turbine For Power GenerationPalm100% (1)

- PlasmaLight SS Neuro10Document1 pagePlasmaLight SS Neuro10PalmNo ratings yet

- Circuit Theory Solved Assignments - Semester Fall 2008Document28 pagesCircuit Theory Solved Assignments - Semester Fall 2008Muhammad Umair100% (3)

- Jquery Interview Questions and Answers For Experienced and FreshersDocument7 pagesJquery Interview Questions and Answers For Experienced and Freshersmikesoni SNo ratings yet

- 150 Watt Amplifier CircuitDocument10 pages150 Watt Amplifier CircuitNuty IonutNo ratings yet

- Poweredge r340 Spec SheetDocument2 pagesPoweredge r340 Spec SheetEdgar CentenoNo ratings yet

- Divya - Detection of Face Spoofs With Raspberry PiDocument34 pagesDivya - Detection of Face Spoofs With Raspberry PidivyaNo ratings yet

- Java AWT GUI ComponentsDocument15 pagesJava AWT GUI Components19BMA111 GOKULNo ratings yet

- Introduction To Classes and ObjectsDocument78 pagesIntroduction To Classes and ObjectsJohn Oliver JamangNo ratings yet

- AssignmentDocument6 pagesAssignmentsadasNo ratings yet

- TIP31A/31B/31C TIP32A/32B/32C: Complementary Silicon Power TransistorsDocument4 pagesTIP31A/31B/31C TIP32A/32B/32C: Complementary Silicon Power TransistorsIrfan ArifinNo ratings yet

- Quad Eia-422 Line Driver With Three-State Outputs: Semiconductor Technical DataDocument5 pagesQuad Eia-422 Line Driver With Three-State Outputs: Semiconductor Technical DataGabriel OliveiraNo ratings yet

- Learn Python in MinutesDocument17 pagesLearn Python in MinutesYuvrajNo ratings yet

- CSF213 OOP Handout 2023 24 Sem IDocument3 pagesCSF213 OOP Handout 2023 24 Sem ISeshasaiNo ratings yet

- Application Note 5336: Gate Drive Optocoupler Basic Design For IGBT / MOSFET Applicable To All Gate Drive OptocouplersDocument4 pagesApplication Note 5336: Gate Drive Optocoupler Basic Design For IGBT / MOSFET Applicable To All Gate Drive OptocouplerselecompinnNo ratings yet

- C12 Assignment (Predict The Output)Document7 pagesC12 Assignment (Predict The Output)bookworm_shashiNo ratings yet

- C Unit 3Document22 pagesC Unit 3suryareddyNo ratings yet

- Memory Management 2010Document103 pagesMemory Management 2010frozentoxicNo ratings yet

- CMOS VLSI DESIGN NOTES Made by Barun Dhiman From Various Books Like Kamran Neil E WasteDocument226 pagesCMOS VLSI DESIGN NOTES Made by Barun Dhiman From Various Books Like Kamran Neil E WasteBarun DhimanNo ratings yet

- Nespace 483kDocument21 pagesNespace 483kvu leNo ratings yet

- 821 2729Document132 pages821 2729kavinmca23No ratings yet

- CutShort Kishore Kumar Resume FXWHDocument4 pagesCutShort Kishore Kumar Resume FXWHdharshan rajNo ratings yet

- CT3 Answer KeyDocument16 pagesCT3 Answer KeyPIYUSH GOPAL (RA2011027010124)No ratings yet

- # 2) Plot Signal With Respect To The Time.: # ImportsDocument6 pages# 2) Plot Signal With Respect To The Time.: # Importsतरुण सिंह यदुवंशीNo ratings yet

- Compalarm CatalogDocument4 pagesCompalarm CatalogXuân Thuỷ PhạmNo ratings yet

- Ec 1003Document23 pagesEc 1003Salam Surjit SinghNo ratings yet

- COmputer LabDocument9 pagesCOmputer LabpnkjinamdarNo ratings yet

- SAP and IoTDocument37 pagesSAP and IoTwthiendia100% (1)

- Image Preprocessing and Feature Extraction in CNNsDocument10 pagesImage Preprocessing and Feature Extraction in CNNsALNATRON GROUPSNo ratings yet

- Tle CSS Module 6 - Testing Electronic ComponentsDocument27 pagesTle CSS Module 6 - Testing Electronic ComponentsCrauxz de Trax100% (1)

- Lab Worksheet # 7Document5 pagesLab Worksheet # 7MUNEEB SHAHNo ratings yet

- MDR 2 Quick Start Guide 4189340624 UkDocument16 pagesMDR 2 Quick Start Guide 4189340624 UkGürkan ÇINARNo ratings yet