Professional Documents

Culture Documents

TD 04 VHDL Fpga en

Uploaded by

bendjeddou ammarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

TD 04 VHDL Fpga en

Uploaded by

bendjeddou ammarCopyright:

Available Formats

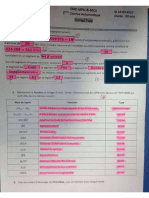

M1 instrumentation University of Skikda 12/03/2023

Tutorial session: Advanced digital electronics: VHDL – FPGA

4th series: VHDL (concurrent instructions)

Give the VHDL description of the following electronic circuits:

1) Half-adder. 5) Comparator for 8-bit numbers.

2) Full-adder. 6) 4:2 encoder.

3) 4-to-1 multiplexer. 7) 4:2 priority encoder.

4) 1-to-4 demultiplexer. 8) 2:4 decoder with enable input.

Sol1) Half-adder

Truth table:

A B C (carry) S

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 0

Logic function of each output:

S = A ∙ 𝐵̅ + 𝐴̅ ∙ B = A xor B = A ⊕ B

C = A∙B

Logic circuit:

VHDL description:

Dr. A. Ganouche page 1 of 9

Sol2) Full-adder

Truth table:

Cin B A Cout S

0 0 0 0 0

0 0 1 0 1

0 1 0 0 1

0 1 1 1 0

1 0 0 0 1

1 0 1 1 0

1 1 0 1 0

1 1 1 1 1

Logic function of each output:

S = A⋅B̅ ⋅ ̅̅̅̅̅

𝐶𝑖𝑛 + A ̅ ⋅ B ⋅ ̅̅̅̅

Cin + A̅⋅B ̅ ⋅ Cin + A ⋅ B ⋅ Cin = A ⊕ B ⊕ Cin

̅̅̅̅ + A ⋅ B

Cout = A ⋅ B ⋅ Cin ̅ ⋅ Cin + A

̅ ⋅ B ⋅ Cin + A ⋅ B ⋅ Cin = A ⋅ B + A ⋅ Cin + B ⋅ Cin

Logic circuit:

VHDL description:

Ripple-Carry Adder:

Dr. A. Ganouche page 2 of 9

Example:

Sol3) 4-to-1 multiplexer

Schematic:

Truth table:

S1 S0 Output

0 0 A

0 1 B

1 0 C

1 1 D

Logic function:

𝑜𝑢𝑡𝑝𝑢𝑡 = ̅̅̅

𝑆1 ∙ ̅̅̅

𝑆0 ∙ 𝐴 + ̅̅̅

𝑆1 ∙ 𝑆0 ∙ 𝐵 + 𝑆1 ∙ ̅̅̅

𝑆0 ∙ 𝐶 + 𝑆1 ∙ 𝑆0 ∙ 𝐷

VHDL description 01:

Dr. A. Ganouche page 3 of 9

VHDL description 02:

Sol4) 1-to-4 demultiplexer

Schematic:

Truth table:

S1 S0 A B C D

0 0 i 0 0 0

0 1 0 i 0 0

1 0 0 0 i 0

1 1 0 0 0 i

Logic function:

̅̅̅ ∙ 𝑆0

𝐴 = 𝑆1 ̅̅̅ ∙ 𝑖

̅̅̅

𝐵 = 𝑆1 ∙ 𝑆0 ∙ 𝑖

̅̅̅ ∙ 𝑖

𝐶 = 𝑆1 ∙ 𝑆0

𝐷 = 𝑆1 ∙ 𝑆0 ∙ 𝑖

Dr. A. Ganouche page 4 of 9

VHDL description:

Sol5) Comparator for 8-bit numbers

Truth table:

inputs outputs

A, B S (superior) E (equal) I (inferior)

A>B 1 0 0

A=B 0 1 0

A<B 0 0 1

VHDL description:

Dr. A. Ganouche page 5 of 9

Sol6) 4:2 encoder

Truth table:

D3 D2 D1 D0 Y1 Y0

0 0 0 1 0 0

0 0 1 0 0 1

0 1 0 0 1 0

1 0 0 0 1 1

other cases x x

The symbol x means the value of the output is 'don't care' otherwise.

Logic function of each output (simplified by Karnaugh map):

Y0 = D1 + D3

Y1 = D2 + D3

Schematic:

VHDL description (conditional assignment):

Dr. A. Ganouche page 6 of 9

VHDL description (selective assignment):

Sol7) 4:2 priority encoder

Truth table:

E3 E2 E1 E0 S1 S0

1 x x x 1 1

0 1 x x 1 0

0 0 1 x 0 1

0 0 0 1 0 0

Other cases x x

VHDL description (conditional assignment):

Dr. A. Ganouche page 7 of 9

VHDL description (selective assignment):

Sol8) 2:4 decoder with an active-high enable input

Schematic:

Truth table:

D1 D0 EN Y3 Y2 Y1 Y0

x x 0 0 0 0 0

0 0 1 0 0 0 1

0 1 1 0 0 1 0

1 0 1 0 1 0 0

1 1 1 1 0 0 0

Logic function of each output:

𝑌0 = ̅̅̅̅

𝐷1 ∙ ̅̅̅̅

𝐷0 ∙ 𝐸𝑁

̅̅̅̅ ∙ 𝐷0 ∙ 𝐸𝑁

𝑌1 = 𝐷1

𝑌2 = 𝐷1 ∙ ̅̅̅̅

𝐷0 ∙ 𝐸𝑁

𝑌3 = 𝐷1 ∙ 𝐷0 ∙ 𝐸𝑁

Dr. A. Ganouche page 8 of 9

VHDL description:

Timing diagram (ModelSim):

Dr. A. Ganouche page 9 of 9

You might also like

- 1034 Chap 2Document48 pages1034 Chap 2kwaikunNo ratings yet

- DD Assignment-2 SolutionDocument10 pagesDD Assignment-2 Solutionsarim rizviNo ratings yet

- Combinational Logic - I: COMP541Document41 pagesCombinational Logic - I: COMP541danya314No ratings yet

- E91 IntroDocument25 pagesE91 IntroAlekso GjakovskiNo ratings yet

- EE101 - Quiz6 2Document4 pagesEE101 - Quiz6 2Just EntertainmentNo ratings yet

- Mitu SikaDocument11 pagesMitu SikaNishat FarjanaNo ratings yet

- Chapter 1-1Document25 pagesChapter 1-1AynalemNo ratings yet

- Microprocessor Exit Exam Reviewer: B. CMC - Complement Carry C. CLD - Clear Direction FlagDocument20 pagesMicroprocessor Exit Exam Reviewer: B. CMC - Complement Carry C. CLD - Clear Direction Flagpclr07No ratings yet

- Solution PDFDocument5 pagesSolution PDFCedric SunNo ratings yet

- L2-CA-Background and MotivationDocument86 pagesL2-CA-Background and MotivationAnubhav ShrivastavaNo ratings yet

- Chapter-8Document23 pagesChapter-8hadangquang1408No ratings yet

- Chapter Two: Logic Gates: August 2020Document22 pagesChapter Two: Logic Gates: August 2020EslamNo ratings yet

- Chapter 2 Basic GatesDocument22 pagesChapter 2 Basic GatesRoyal Ritesh SharmaNo ratings yet

- Logic Gates and Boolean Algebra GuideDocument8 pagesLogic Gates and Boolean Algebra GuideMarc Liam LuNo ratings yet

- QbcsaDocument7 pagesQbcsaMohammad ImthiyazNo ratings yet

- Vlsi - Lab (1) - 1-39Document39 pagesVlsi - Lab (1) - 1-39Angel AlphaNo ratings yet

- FFTDocument28 pagesFFTFan Wang100% (2)

- 06 - Secure Two-Party ComputationDocument56 pages06 - Secure Two-Party ComputationDaudet Polycarpe TiomelaNo ratings yet

- midex2023-solutionsDocument8 pagesmidex2023-solutionsauguz2702No ratings yet

- Chapter 6Document16 pagesChapter 6Gébrè SîllãsíêNo ratings yet

- Section TwoDocument14 pagesSection Twogilbertkudi7No ratings yet

- Dldlab6 justPreLabDocument10 pagesDldlab6 justPreLabArfaat SanitaryNo ratings yet

- Example 1: Simplify The Following Boolean Expression. Using Boolean Algebra Postulates andDocument10 pagesExample 1: Simplify The Following Boolean Expression. Using Boolean Algebra Postulates andMohamed ZaideNo ratings yet

- ExamenDocument4 pagesExamenCristian ToapantaNo ratings yet

- Demorgan's Theorem Logic EquationsDocument6 pagesDemorgan's Theorem Logic EquationsAmandeep SinghNo ratings yet

- Lab Report on Microelectronics and VLSI Design LabDocument32 pagesLab Report on Microelectronics and VLSI Design LabRitwik KumarNo ratings yet

- DSD 1Document8 pagesDSD 1Oday RidhaNo ratings yet

- EE477 Homework Solutions Transmission Gate CircuitsDocument12 pagesEE477 Homework Solutions Transmission Gate Circuitstooba mukhtarNo ratings yet

- Past Paper 10015 21 - SDocument32 pagesPast Paper 10015 21 - SYang ZhouNo ratings yet

- LESSON9.4 ElectronicsDocument27 pagesLESSON9.4 ElectronicsThiyaku MaruthaNo ratings yet

- Ee200 Digital Logic Circuit Design: Exclusive-Or FunctionDocument8 pagesEe200 Digital Logic Circuit Design: Exclusive-Or Functionneels4uNo ratings yet

- Computer ArchitectDocument19 pagesComputer Architect10422110No ratings yet

- The Following Paper Is The Collective Efforts of The Following StudentsDocument8 pagesThe Following Paper Is The Collective Efforts of The Following StudentsAhmed Mohamed EwisNo ratings yet

- Lab 9 Encoders And DecodersDocument7 pagesLab 9 Encoders And Decoderssafdarmunir070No ratings yet

- Artificial IntelligenceDocument26 pagesArtificial Intelligencedemissie ejoNo ratings yet

- Philadelphia University Final Exam Logic CircuitsDocument7 pagesPhiladelphia University Final Exam Logic Circuitsnada abdelrahmanNo ratings yet

- 8-to-3 Encoder and 3-to-8 Decoder CircuitDocument13 pages8-to-3 Encoder and 3-to-8 Decoder CircuitEden HamamNo ratings yet

- UCSB ECE 152a Course ReaderDocument19 pagesUCSB ECE 152a Course Readermuhd220No ratings yet

- Lecture_2-8Document19 pagesLecture_2-8contact.swati.4No ratings yet

- EE421/621 Digital CircuitsDocument71 pagesEE421/621 Digital CircuitsprachibhideNo ratings yet

- Chapter 2 - Combinational Logic Circuits: Logic and Computer Design FundamentalsDocument27 pagesChapter 2 - Combinational Logic Circuits: Logic and Computer Design FundamentalsNurbek NussipbekovNo ratings yet

- Lab 1 Digital Logic Gates and Boolean FunctionsDocument7 pagesLab 1 Digital Logic Gates and Boolean FunctionsIfthakharul Alam Shuvo100% (1)

- DLD - LR1Document7 pagesDLD - LR1Shopnil KarmakarNo ratings yet

- COD Ch. 3 Arithmetic For ComputersDocument72 pagesCOD Ch. 3 Arithmetic For ComputersMohammad Abdul RafehNo ratings yet

- Verification of Logic Gates LabDocument11 pagesVerification of Logic Gates LabJeromeNo ratings yet

- 04 Adder MUX DMUX 2019Document31 pages04 Adder MUX DMUX 2019Ashutosh DasNo ratings yet

- Digital Logic - Computer ArchitectureDocument41 pagesDigital Logic - Computer ArchitectureManvir SinghNo ratings yet

- 241 CSM-4-Digital Logic-Lecture 10Document51 pages241 CSM-4-Digital Logic-Lecture 10ahmedNo ratings yet

- 4b (Digital System) Logic Gates _ Boolean ExpressionDocument36 pages4b (Digital System) Logic Gates _ Boolean ExpressionSyahmi AkmalNo ratings yet

- Activity 1.1.6 Component Identification: Digital: Combinational LogicDocument7 pagesActivity 1.1.6 Component Identification: Digital: Combinational LogicLuke PierNo ratings yet

- II Mid Bits For StudentsDocument9 pagesII Mid Bits For StudentsSurya MukeshNo ratings yet

- DARE1B22 P1901003 LohJiaHung PbilreportDocument5 pagesDARE1B22 P1901003 LohJiaHung PbilreportLoh Jia HungNo ratings yet

- Docsity Practice Exam With Solutions Introduction To Digital System Design Ece 27000Document7 pagesDocsity Practice Exam With Solutions Introduction To Digital System Design Ece 27000Quang ThắngNo ratings yet

- DD Practicals Master ManualDocument58 pagesDD Practicals Master Manualraghu_chandra_3No ratings yet

- Chapter #3Document42 pagesChapter #3علوم حاسبNo ratings yet

- 2022 S1 IT1020 Lecture 06Document47 pages2022 S1 IT1020 Lecture 06gepoveNo ratings yet

- General Problem SheetDocument10 pagesGeneral Problem SheetshivaNo ratings yet

- Computer Architecture: Introduction To CA Role of CA in Designs Performance Issues Now Review of Some DLD ConceptsDocument52 pagesComputer Architecture: Introduction To CA Role of CA in Designs Performance Issues Now Review of Some DLD ConceptsSaeed RehmanNo ratings yet

- n.TextMarkDocument5 pagesn.TextMarkbendjeddou ammarNo ratings yet

- o.TextMarkDocument3 pageso.TextMarkbendjeddou ammarNo ratings yet

- o.TextMarkDocument2 pageso.TextMarkbendjeddou ammarNo ratings yet

- n.TextMarkDocument2 pagesn.TextMarkbendjeddou ammarNo ratings yet

- Patai S., Rappoport Z. (Eds.) - The Chemistry of Organic Selenium and Tellurium Compounds. v.1Document939 pagesPatai S., Rappoport Z. (Eds.) - The Chemistry of Organic Selenium and Tellurium Compounds. v.1Shubham Shahu100% (1)

- Logic Design With MSI Circuits: 1. Binary Adder - SubtractorDocument10 pagesLogic Design With MSI Circuits: 1. Binary Adder - SubtractorBalaji PalanisamyNo ratings yet

- ECE 240 - Electrical Engineering Fundamentals PSPICE Tutorial 10: Frequency Response of CircuitsDocument3 pagesECE 240 - Electrical Engineering Fundamentals PSPICE Tutorial 10: Frequency Response of Circuitstareq omarNo ratings yet

- Canon Ir c3200 c3220 Series SCHDocument52 pagesCanon Ir c3200 c3220 Series SCHBeetlebumNo ratings yet

- Lecture 10: Power-Flow Studies: Instructor: Dr. Gleb V. Tcheslavski Contact: Office HoursDocument28 pagesLecture 10: Power-Flow Studies: Instructor: Dr. Gleb V. Tcheslavski Contact: Office HoursAn00pgadzillaNo ratings yet

- Estacion ManualDocument2 pagesEstacion ManualvicgarofaloNo ratings yet

- Operation Manual For Vacuklav 24Document45 pagesOperation Manual For Vacuklav 24Fernando JamesNo ratings yet

- Ficha Técnica Panel POWER START 0500 PDFDocument4 pagesFicha Técnica Panel POWER START 0500 PDFSeba CarrielNo ratings yet

- Fenton FT 2.2 Series 6 10kvaDocument2 pagesFenton FT 2.2 Series 6 10kvajuan lopezNo ratings yet

- Pure Sine Inverter EU Instructions 01Document8 pagesPure Sine Inverter EU Instructions 01Oleksandr PolishchukNo ratings yet

- IStroboSoft Inapp ContentDocument11 pagesIStroboSoft Inapp Content15101980No ratings yet

- Pre Lab1Document7 pagesPre Lab1Fakhir ShahNo ratings yet

- Codan Tactical - Antenna ComparisionDocument6 pagesCodan Tactical - Antenna ComparisionBernardo Marín BustosNo ratings yet

- Frequency PIDDocument6 pagesFrequency PIDAlejandroHerreraGurideChileNo ratings yet

- PF ArcDocument1 pagePF Arcrafik1995No ratings yet

- AsianBrands - SamsungSIADocument16 pagesAsianBrands - SamsungSIAJulia KohNo ratings yet

- DXM100-Sx Wireless Modbus Slave: Instruction ManualDocument43 pagesDXM100-Sx Wireless Modbus Slave: Instruction ManualJEYSONNo ratings yet

- Unit-1 DC CircuitsDocument183 pagesUnit-1 DC CircuitsChannabasappa KudarihalNo ratings yet

- 4 - Questions On PlugsDocument10 pages4 - Questions On PlugsJohn ChiltonNo ratings yet

- Samsung Universal Gingerbread Root & Unroot 2.3.3-2.3.7Document27 pagesSamsung Universal Gingerbread Root & Unroot 2.3.3-2.3.7ricad1234No ratings yet

- G006 - H135-155XL (G006)Document456 pagesG006 - H135-155XL (G006)Bruno Leocadio100% (5)

- EST3 Installation and Service ManualDocument386 pagesEST3 Installation and Service ManualБахтияр ЮмачиковNo ratings yet

- Hfe - Panasonic - Sa-Ht520 - Service - en MODULO DVDDocument104 pagesHfe - Panasonic - Sa-Ht520 - Service - en MODULO DVDAirkid Discomovil JesusNo ratings yet

- 4-Cylinder Engine EMS ExplainedDocument27 pages4-Cylinder Engine EMS ExplainedGabriel BalcazarNo ratings yet

- Computation of Steady State Error of Various Types Control SystemsDocument6 pagesComputation of Steady State Error of Various Types Control SystemsMohamed SamNo ratings yet

- Synopsis RfidDocument5 pagesSynopsis Rfidsaini_sahilNo ratings yet

- 191 Version 4 TC14 Technical ManualDocument42 pages191 Version 4 TC14 Technical ManualBrahim Chergui100% (2)

- Counselling Students Details Backlogs, Attendance% (23.08.2014)Document4 pagesCounselling Students Details Backlogs, Attendance% (23.08.2014)Sobhan DasariNo ratings yet

- DX DiagDocument13 pagesDX DiagAnimesh BhattaraiNo ratings yet

- Diagnostic Card Manual EngDocument23 pagesDiagnostic Card Manual EngRalph GuillouNo ratings yet