Professional Documents

Culture Documents

ICISC Coimbatore (2019)

Uploaded by

Dr. D. V. KamathOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ICISC Coimbatore (2019)

Uploaded by

Dr. D. V. KamathCopyright:

Available Formats

International Conference on Inventive Systems and Control (ICISC 2019)

IEEE Xplore Part Number: CFP19J06-ART; ISBN: 978-1-5386-3950-4

Implementation of Low Voltage Floating Gate

MOSFET based Current Mirror Circuits using 180nm

technology

Ansuman Mishra1 M Vineeth Bhat2

M.Tech (Microelectronics) M.Tech (Microelectronics)

E-mail: anshumn.305@gmail.com E-mail: vineethmbhat@gmail.com

Prasad Krishna Pai3 D V Kamath4‡

M.Tech (Microelectronics) Professor

E-mail: prasadk.pai21@gmail.com E-mail: dv.kamath@manipal.edu

1,2,3,4

Department of Electronics and Communication Engineering, Manipal Institute of Technology, Manipal Academy of

Higher Education, Manipal, India.

‡ Corresponding Author

Abstract— The paper discusses implementation of low voltage The structure of Floating-Gate MOSFET (FGMOS) is similar

(LV) basic current mirror (CM) and cascode current mirror to a conventional MOSFET except that FGMOS has two gates

(CCM) circuits using Floating Gate MOSFET (FGMOS) devices. i.e. control gate(s) and floating gate (FG). The FGMOS is

The performance parameters such as output resistance, minimum fabricated using a standard double-polysilicon CMOS process,

output voltage requirement and power dissipation are compared

where the first polysilicon layer forms the floating gate (FG)

for basic CM and double CCM circuits. The current mirror

circuits are implemented with 180 nm technology using Cadence over the channel and the second polysilicon layer forms the

Virtuoso and simulated with Spectre RF. The simulation results multiple-input control gates (MIG) over the FG. The secondary

are in good agreement with theory. The FGMOS based basic CM gates or inputs are electrically isolated from FG and are only

and double CCM circuits exhibited 52.4% and 40% power capacitive connected to FG [5]. The FG inserted between the

reduction as compared to gate driven current mirror circuits. transistor channel and MIG provides indirect control over the

operation of MOSFET.

Keywords— Floating Gate MOSFET, Current mirror,

Cascode Current mirror.

I. INTRODUCTION

In analog circuits, low voltage and low power operations are

main issues of concern due to increasing demand for portable

electronic applications. Current mirror is one of the most (a)

frequently used analog circuit where power utilization is

influenced by supply voltage. Hence it is a challenging task to

design low voltage (LV), low power (LP) and high performance

current mirror circuits.

Floating gate transistors provide an optimal way of tuning the

threshold voltage of MOSFET by applying appropriate bias

voltage [1]. The main advantage of using floating gate transistor

is to decrease the headroom voltages. However, use of floating

gate transistors has some disadvantages like increased area

requirement and reduced gain bandwidth parameter. (b)

II. FLOATING GATE MOSFET Fig. 1 The n-input n-channel FGMOS transistor (a) Symbol, (b)

Equivalent circuit model

The fabrication trend followed in modern day VLSI is to create Let Vi (for i =1, 2,... N) are the control input voltages. The

smaller and faster transistors. However, reducing size may lead effective input capacitance Ci,eff associated with these inputs is

to dielectric breakdown. This issue can be reduced by operating given in (1a) as the summation of input capacitances between

the transistor with low voltage power supply [2]-[6]. control gates and floating gate. The total capacitance 𝐶𝑇 of the

floating-gate is given by

978-1-5386-3950-4/19/$31.00 ©2019 IEEE 268

International Conference on Inventive Systems and Control (ICISC 2019)

IEEE Xplore Part Number: CFP19J06-ART; ISBN: 978-1-5386-3950-4

Ci,eff = ∑ Ci = C1 + C2 + . . +CN (1a)

i=1

N

CT = ∑ Ci + CFGD + CFGS + CFGB (1b)

i=1

where CFGD, CFGS and CFGB are the parasitic capacitance of

floating gate with drain, source and bulk respectively. (a)

The voltage on its floating gate (𝑉𝐹𝐺 ) is given by

N

Ci CFGD CFGS CFGB QFG

VFG = ∑ ( VGi ) + V + V + V + (2a)

CT CT DS CT SS CT BS CT

i=1

where

Q FG is charge trapped in FG during fabrication

VDS is drain-source voltage

VSS is source voltage (b)

VBS is bulk-source voltage Fig. 2 Two-input FGMOS with control gate voltages (a) Equivalent

From (2a) it follows that the voltage on floating gate is linear circuit model (b) simulation model

sum of all input voltages (drain-source voltage, source voltage The presence of multiple gates provides ability to control and

and bulk-source voltage) weighted by capacitive scaling reduce the threshold voltage of the MOSFET [7] which enable

factors. circuits to work with low supply voltage and with lesser power.

As Ci ≫ CFGD , CFGS , CFGB VFG would only depend on the

voltages at the control inputs as The performance of the floating gate is affected by process

N variations as some charges may get locked during fabrication

Ci leading to dc offset [7]. The amount of charges on FG can be

VFG = ∑ ( VGi ) (2b)

CT

i=1

modified by electron tunneling and hot electron injection.

However, 𝑄𝐹𝐺 can be eliminated by the method proposed [8].

In case of a two input FG-MOSFET in Fig. 2(a), a bias voltage

Vbias is applied to one of the control gates through C1 and the III. FGMOS BASED CURRENT MIRROR (CM)

input signal is applied to second gate through C2 . Assuming

zero initial voltages and neglecting parasitic capacitances of Current mirror circuits are one of the most fundamental blocks

FG in comparison with C1 and C2 , the floating gate voltage is in analog circuit design. The current mirror circuit copies the

given by current flowing in one active device to another, keeping the

C1 C2 output current constant regardless of load variations [9].

VFG = V + V

CT bias CT in (2c) Important areas of applications for current mirror circuits are

Assuming (C1 + C2 ) ≫ CFGD , CFGS , CFGB , the expression for current biasing, current amplification and current copyng. The

drain current for n-channel FGMOS in saturation region is desirable characteristics of current mirror circuits are high

shown to be output resistance, minimum output voltage and high voltage

β C2 C1 2 swing [9]. The current mirror circuits are designed using

IDS = {( Vin + Vbias ) − Vth } (3a) FGMOS, in order to operate with reduced supply voltage [2]-

2 CT CT

[6].

The equation (3a) can be written as

2 A. FGMOS based basic Current Mirror (CM)

β C2 2 CT C1

IDS = ( ) {Vin − (Vth ( ) − Vbias ( ))} (3b) The configuration of FGMOS based CM is same as that of

2 CT C2 C2

conventional gate driven CM except the use of two input

From (3b) the effective threshold voltage for the FGMOS is FGMOS. The circuit of basic current mirror using FGMOS is

shown as shown in Fig. 3.

CT C1

Vth,eff = Vth ( ) − Vbias ( ) (3c)

C2 C2

Alternately Vth,eff is expressed as

C1

Vth,eff = Vth + (V − Vbias ) (3d)

C2 th

From (3c)-(3d) it is evident that Vth,eff can be made smaller than

Vth by appropriate selection of C1 , C2 and dc bias voltage Vbias .

As the simulation tool does not support floating gate node,

resistances are placed in parallel to each capacitors 𝐶1 and 𝐶2 in

the simulation model of Fig. 2 (b) to provide the dc path.

(a)

978-1-5386-3950-4/19/$31.00 ©2019 IEEE 269

International Conference on Inventive Systems and Control (ICISC 2019)

IEEE Xplore Part Number: CFP19J06-ART; ISBN: 978-1-5386-3950-4

(b)

Fig. 3 FGMOS based basic current mirror (a) schematic circuit (b)

equivalent circuit

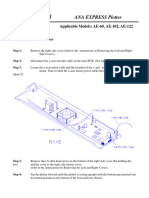

The two input FGMOS transistors M1 and M2 form the current (b)

mirror. In the two input FGMOS one gate is used as Fig. 4 FGMOS based double cascode current mirror (a) schematic

conventional input terminal and the second gate is applied with circuit (b) equivalent circuit

a DC biasing voltage Vbias which is used to lower the threshold

voltage there by reducing Vo,min of the current mirror. The IV. IMPLEMENTATION AND RESULTS

resistances R1a , R1b and capacitances C1a , C1b are part of the

macro model of FGMOS. The output resistance of the basic

The basic and double cascode current mirror circuits are

current mirror in Fig. 3 is given as

implemented in Cadence design environment for 180 nm

R out = rds2 (4) technology. The design parameters used for the implementation

of current mirror circuits are given in Table I.

B. FGMOS based double Cascode Current Mirror (CCM)

Table I Design parameters used for FGMOS based basic CM and

In general, CCM require higher voltage headroom as double CCM implementation

compared to a simple CM, but provides higher output

impedance. The FGMOS based low voltage CCM is shown in Parameters Basic CM Double CCM

Fig. 4. All the MOS devices are two input FGMOS. The current Vdd +0.4 V +0.4 V

mirrors M1-M2 and M3-M4 are stacked to form a double CCM.

All the MOS devices are operated in saturation region. Vss -0.4 V -0.4 V

The output resistance of FGMOS based double cascode current Iref 10 µA 10 µA

mirror is given as

(5a) (W⁄L)1,2 2 µm/180nm 2 µm/180 nm

R out = rds4 {1 + (g m4 + g mb4 ) ∗ rds2 } + rds2

(W⁄L)3,4 - 2 µm/ 180 nm

R out ≅ g m ∗ rds 2 (5b)

The R out is g m ∗ rds times more than the basic current mirror. R1a , R 2a 1 MΩ 1 MΩ

C1a , C2a 1 pF 1 pF

R1b , R 2b 1 kΩ 1 kΩ

C1b, C2b 4 pF 4 pF

R 3a , R 4a - 1 MΩ

C3a , C4a - 1 pF

R 3b , R 4b - 1 kΩ

C3b , C4b - 4 pF

(a)

CM-Current Mirror, CCM-Cascode Current Mirror

978-1-5386-3950-4/19/$31.00 ©2019 IEEE 270

International Conference on Inventive Systems and Control (ICISC 2019)

IEEE Xplore Part Number: CFP19J06-ART; ISBN: 978-1-5386-3950-4

From (3d) it is evident that Vth can be lowered by choosing V. CONCLUSION

appropriate values of C1 and C2 . A plot showing the variation

of Vth with respect to the bias voltage for FGMOS based CM The two types of current mirror circuits namely basic CM and

obtained from dc simulation is given in Fig. 5. double CCM circuits have been implemented using FGMOS in

Cadence design environment and the simulation results have

The plots of Iout versus Vout for FGMOS based basic current been analyzed and compared with gate driven current mirror

mirror and double cascode current mirror for different values of circuits. The power reduction of 40% and 52.4 % are observed

Vbias are respectively given in Fig. 6 an Fig. 7. The increase in for double CCM and basic CM when FGMOS is used. It is

Vbias reduces the threshold voltage and the transistors will be in evident from the simulation results that FGMOS based current

saturation for a reduced output voltages. The comparison of basic mirror circuits exhibit reduced Vomin requirement and thus

CM and double CCM circuits with FGMOS and without FGMOS for suited for low voltage and low power applications.

different performance parameters are given in Table II and Table III

respectively.

REFERENCES

Table II Comparison of simulated results for basic current mirror with

FGMOS and without FGMOS

[1] J. Ramirez-Angulo, S. C. Choi, and G. Gonzalez-Altamirano, “Low-

Voltage Circuits Building Blocks Using Multiple-Input Floating-Gate

Parameter Basic CM without Basic CM with Transistors,” IEEE Transactions on Circuits and Systems I: Fundamental

FGMOS FGMOS Theory and Applications, vol. 42, no. 11, pp. 971-974, Nov. 1995.

Process Technology 180 180 [2] Susheel Sharma, S. S. Rajput, L. K. Mangotra and S. S. Jamuar, “FGMOS

(nm) based wide range lowvoltage current mirror and its application”, Asia-

Vdd +1 V +0.4 V Pacific Conference on Circuits & Systems, vol. 2, pp. 331-334, Oct. 2002.

[3] Parshotam S. Manhas, Susheel Sharma, K. Pal, L.K.Mangotra & K.S.

Vss -1 V -0.4 V Jamwal, “High performance FGMOS-based low volage current mirror,”

Indian Journal of Pure & Applied Physics, vol. 46, pp. 355-358, May

Vomin (V) 0.5 V 0.2 V 2008.

[4] Abhinav Anand, Sushanta K. Mandal, Anindita Dash, B. Shivalal Patro,

R out (Ω) 0.133 MΩ 1.66 MΩ “FGMOS based low-voltage low-power high output impedance regulated

Power (µW) 55.3 µW 26.3 µW cascode current mirror,” International Journal of VLSI Design &

Communication Systems (VLSICS), vol. 4, no.2, pp. 39, Apr. 2013.

[5] Samir B. Joshi, J.C.Prajapati, B.H.Soni,"Analysis and Study of FGMOS

Based Current Mirror Circuit Using 0.35μm Technology,” International

Table III Comparison of simulated results for double cascode current Journal of Engineering and Innovative Technology (IJEIT), vol. 2, no. 10,

pp. 163-167, Apr. 2013.

mirror with FGMOS and without FGMOS

[6] Nurulain, D., Musa, F.A.S., Isa, M.M., Ahmad, N. and Kasjoo, S.R.,

“Low voltage low power FGMOS based current mirror,” In EPJ Web of

Parameter Double CCM Double CCM with Conferences, vol. 162, p. 01048, 2017.

without FGMOS FGMOS [7] Rockey Gupta, Susheel Sharma, “Quasi-floating gate MOSFET based

Process 180 180 low voltage current mirror,” Microelectronics Journal, vol. 43, no. 7, pp.

Technology (nm) 439-443, Apr. 2012.

Vdd +1 V +0.4 V [8] E. Rodriguez-Villegas and H. Barnes, “Solution to trapped charge in

FGMOS transistors,” IEE Electronic Letters, vol. 39, no. 19, Sept. 2003.

Vss -1 V -0.4 V

[9] Hitesh, Anuj Goel, “Advancement in Current Mirror Technique,”

Vomin (V) 0.6 V 0.3 V International Journal of Advance Research in Computer Science &

Software Engineering, vol. 2, no. 1, Jan. 2012.

R out (Ω) 2 MΩ 3.33 MΩ

Power (µW) 66.4 µW 39.48 µW

The power consumed in gate driven and FGMOS based basic

CM are respectively 55.3 µW and 26.3 µW respectively. The

power consumed in gate driven and FGMOS based double

CCM are found to be respectively 66.4 µW and 39.48 µW

respectively.

978-1-5386-3950-4/19/$31.00 ©2019 IEEE 271

International Conference on Inventive Systems and Control (ICISC 2019)

IEEE Xplore Part Number: CFP19J06-ART; ISBN: 978-1-5386-3950-4

Fig. 5 Plot showing variation of Vth,eff versus bias voltage for FGMOS based basic current mirror

Fig. 6 Plot of Iout versus 𝑉𝑜𝑢𝑡 for FGMOS based basic current mirror

Fig. 7 Plot of Iout versus Vout for FGMOS based cascode current mirror

978-1-5386-3950-4/19/$31.00 ©2019 IEEE 272

You might also like

- Quasi-Floating Gate Based High Precision Current Mirror: D. Rajesh, Dr. N. Raj, Dr. P. John PaulDocument12 pagesQuasi-Floating Gate Based High Precision Current Mirror: D. Rajesh, Dr. N. Raj, Dr. P. John PaulPeter HeinNo ratings yet

- Voltage - Current Converter For A Memory Current Cell Using Floating Gate TransistorsDocument6 pagesVoltage - Current Converter For A Memory Current Cell Using Floating Gate TransistorsAram ShishmanyanNo ratings yet

- Low-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationDocument4 pagesLow-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationwhamcNo ratings yet

- Ponencia - Filter - BodyDriven Gonzalez CarvajalDocument4 pagesPonencia - Filter - BodyDriven Gonzalez CarvajalFernando JarixNo ratings yet

- V3i513 PDFDocument6 pagesV3i513 PDFIJCERT PUBLICATIONSNo ratings yet

- Effect of Gate-Source Bias Voltage and Gate-Drain Leakage Current On The Short-Circuit Performance of FTO-type SiC Power MOSFETsDocument4 pagesEffect of Gate-Source Bias Voltage and Gate-Drain Leakage Current On The Short-Circuit Performance of FTO-type SiC Power MOSFETs刘锦成No ratings yet

- Ref 26 Fully Coupled 3-D Device Simulation of Negative Capacitance FinFETs For Sub 10 NM IntegrationDocument4 pagesRef 26 Fully Coupled 3-D Device Simulation of Negative Capacitance FinFETs For Sub 10 NM IntegrationM. Ashikuzzaman KowshikNo ratings yet

- A New Approach Ultra Low Voltage CMOS Logic Circuits AnalysisDocument5 pagesA New Approach Ultra Low Voltage CMOS Logic Circuits AnalysisijsretNo ratings yet

- Study of Very Fast Transient Overvoltages and Mitigation Techniques of A Gas Insulated SubstationDocument6 pagesStudy of Very Fast Transient Overvoltages and Mitigation Techniques of A Gas Insulated SubstationThyago De Moura JorgeNo ratings yet

- A 93.7% Peak Efficiency DC-DC Buck Converter With All-Pass Network Based Passive Level Shifter in 55 NM CMOSDocument4 pagesA 93.7% Peak Efficiency DC-DC Buck Converter With All-Pass Network Based Passive Level Shifter in 55 NM CMOSRaghvendra DeshpandeNo ratings yet

- IGBT & Sic MosfetDocument7 pagesIGBT & Sic MosfetNgọc Hưng TạNo ratings yet

- UPFC Using Multiconverter Operated by Phase-Shifted Triangle Carrier SPWM StrategyDocument6 pagesUPFC Using Multiconverter Operated by Phase-Shifted Triangle Carrier SPWM StrategyjaiminNo ratings yet

- 10 1109@pesgre45664 2020 9070632Document6 pages10 1109@pesgre45664 2020 9070632Mahmood PashiNo ratings yet

- International Journal of Electronics and Communications (AEÜ)Document12 pagesInternational Journal of Electronics and Communications (AEÜ)RajeeNo ratings yet

- Modern Power Semiconductor Devices (A Review) : Meenakshi Mataray, APDocument4 pagesModern Power Semiconductor Devices (A Review) : Meenakshi Mataray, APGauravKumarNo ratings yet

- Presented by Animesh Karmaker Roll: 1103115 Eee, KuetDocument15 pagesPresented by Animesh Karmaker Roll: 1103115 Eee, KuetNilNo ratings yet

- Prospects of IGCT Technology: High Power SemiconductorsDocument3 pagesProspects of IGCT Technology: High Power SemiconductorspjacqmaeNo ratings yet

- 0.5 V Bulk-Driven Analog Building BlocksDocument10 pages0.5 V Bulk-Driven Analog Building BlocksnamNo ratings yet

- CMOS Implemented VDTA Based Colpitt OscillatorDocument4 pagesCMOS Implemented VDTA Based Colpitt OscillatorijsretNo ratings yet

- Singh 2018Document5 pagesSingh 2018Tshering Sangmoo SherpaNo ratings yet

- A New Current Source Converter Using SCGTDocument7 pagesA New Current Source Converter Using SCGTroggery pieroNo ratings yet

- 84 - Insulated Gate Bipolar Transistors (Igbts)Document2 pages84 - Insulated Gate Bipolar Transistors (Igbts)Guillermo DelgadoNo ratings yet

- Microelectronics Journal: Habib Rastegar, Jee-Youl RyuDocument8 pagesMicroelectronics Journal: Habib Rastegar, Jee-Youl RyuRAJAMOHANNo ratings yet

- DCDL - Noise and JitterDocument4 pagesDCDL - Noise and JitterDavidNo ratings yet

- Four Novel PWM Shoot-Through Control Methods For Impedance Source DC-DC ConvertersDocument10 pagesFour Novel PWM Shoot-Through Control Methods For Impedance Source DC-DC ConvertersUtkarsh PrakashNo ratings yet

- Fusing IGBT-based Inverters: Abstract. The Number of Applications Based OnDocument9 pagesFusing IGBT-based Inverters: Abstract. The Number of Applications Based OnMohammed Al gobariNo ratings yet

- Application Note: Extremely Compact, Isolated Gate Driver Power Supply For Sic-Mosfet (6 - 10 W)Document5 pagesApplication Note: Extremely Compact, Isolated Gate Driver Power Supply For Sic-Mosfet (6 - 10 W)Wesley de PaulaNo ratings yet

- Comparator Kick Back Noise PaperDocument8 pagesComparator Kick Back Noise Papergr8minds4allNo ratings yet

- Frequency Dependent Negative Resistance Implementation - Theingjit Et AlDocument4 pagesFrequency Dependent Negative Resistance Implementation - Theingjit Et AlJohn Bofarull GuixNo ratings yet

- Comparision of Floating Gate & Pseudo Floating Gate TechniquesDocument3 pagesComparision of Floating Gate & Pseudo Floating Gate TechniquesInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- IGCT Technology Baseline and Future Opportunities: Peter Steimer, Oscar Apeldoorn, Eric Carroll, Andreas NagelDocument6 pagesIGCT Technology Baseline and Future Opportunities: Peter Steimer, Oscar Apeldoorn, Eric Carroll, Andreas NagelculwavesNo ratings yet

- 10 GyratorDocument14 pages10 GyratorPako AlbNo ratings yet

- Leakage Minimization Technique For Nanoscale Cmos Vlsi: Ecause of TheDocument9 pagesLeakage Minimization Technique For Nanoscale Cmos Vlsi: Ecause of TheSdNo ratings yet

- A 0.18 M CMOS DDCCII For Portable LV-LP Filters: Vincenzo STORNELLI, Giuseppe FERRIDocument6 pagesA 0.18 M CMOS DDCCII For Portable LV-LP Filters: Vincenzo STORNELLI, Giuseppe FERRIHamid BoualiNo ratings yet

- Electronics: A Low-Power CMOS Bandgap Voltage Reference For Supply Voltages Down To 0.5 VDocument16 pagesElectronics: A Low-Power CMOS Bandgap Voltage Reference For Supply Voltages Down To 0.5 VleonnyNo ratings yet

- An Innovative Ultra Low Voltage Sub-32nm SRAM Voltage Sense Amplifier in DG-SOI TechnologyDocument4 pagesAn Innovative Ultra Low Voltage Sub-32nm SRAM Voltage Sense Amplifier in DG-SOI Technologyapi-19668941No ratings yet

- Tunneling Leakage Current of Gate-All-AroundDocument3 pagesTunneling Leakage Current of Gate-All-AroundMahdi KarimiNo ratings yet

- Non-Conventional Low Power Circuit Design TechniquesDocument9 pagesNon-Conventional Low Power Circuit Design Techniquesijire publicationNo ratings yet

- Design and Simulation of A Two Stage OPAMPDocument4 pagesDesign and Simulation of A Two Stage OPAMPAbd TashNo ratings yet

- Estimation of Junction Temperature and Power Loss of IGBT Used in VVVF Inverter Using Numerical Solution From Data Sheet ParameterDocument6 pagesEstimation of Junction Temperature and Power Loss of IGBT Used in VVVF Inverter Using Numerical Solution From Data Sheet Parameterzeevko1249No ratings yet

- CMOS ' Design RulesDocument2 pagesCMOS ' Design RulesSanket PatilNo ratings yet

- 2 Majd2018Document6 pages2 Majd2018OmarFaruqeNo ratings yet

- Avc - M.tech. Sem II - Hw-I Feb. 2018Document2 pagesAvc - M.tech. Sem II - Hw-I Feb. 2018Agnibha DasguptaNo ratings yet

- An Overview of Normally-Off Gan-Based High Electron Mobility TransistorsDocument18 pagesAn Overview of Normally-Off Gan-Based High Electron Mobility Transistorsvamshi krishnaNo ratings yet

- A Low Voltage High Performance OTA in 0.18 Micron With High LinearityDocument10 pagesA Low Voltage High Performance OTA in 0.18 Micron With High LinearitymohsenparsauniNo ratings yet

- An Ultra-Low Voltage High Gain Operational TranscoDocument5 pagesAn Ultra-Low Voltage High Gain Operational TranscoKarima Ben salahNo ratings yet

- A Dspic Based Efficient Single-Stage Grid-Connected Photovoltaic SystemDocument4 pagesA Dspic Based Efficient Single-Stage Grid-Connected Photovoltaic SystemAsim DattaNo ratings yet

- Linearity and Intermodulation Distortion PPR, 2012Document6 pagesLinearity and Intermodulation Distortion PPR, 2012sharmasamriti27No ratings yet

- Ultra-Low-Power 2.4 GHZ Colpitts Oscillator Based On Double Feedback TechniqueDocument4 pagesUltra-Low-Power 2.4 GHZ Colpitts Oscillator Based On Double Feedback TechniqueCamila DamascenoNo ratings yet

- Domino Logic CircuitsDocument4 pagesDomino Logic CircuitsSahil BansalNo ratings yet

- Analog/Digital Circuit Design in Sige For Space ApplicationsDocument6 pagesAnalog/Digital Circuit Design in Sige For Space ApplicationsNguyễn ThaoNo ratings yet

- Lam 2013Document4 pagesLam 2013usha pawanNo ratings yet

- Wide Frequency Range Voltage Controlled Ring Oscillators Based On Transmission GatesDocument4 pagesWide Frequency Range Voltage Controlled Ring Oscillators Based On Transmission GatesRam MNo ratings yet

- 2012 IEEE 0.6 V Class-AB CMOS Voltage Followe With Bulk-Driven Quasi Floating Gate Super Source FollowerDocument4 pages2012 IEEE 0.6 V Class-AB CMOS Voltage Followe With Bulk-Driven Quasi Floating Gate Super Source FollowerMuhammad Sohail Asst. ProfessorNo ratings yet

- IGBT in SeriesDocument8 pagesIGBT in SeriesvasiliyNo ratings yet

- A PV Module-Integrated Inverter Using A Ćuk Converter in DCM With Island Detection SchemeDocument6 pagesA PV Module-Integrated Inverter Using A Ćuk Converter in DCM With Island Detection Schemegrasia77No ratings yet

- New 1600V BIMOSFET TransistorsDocument10 pagesNew 1600V BIMOSFET TransistorsCristian BandilaNo ratings yet

- PDF 23Document7 pagesPDF 23Jimmy MachariaNo ratings yet

- 10 3390@en12142663Document20 pages10 3390@en12142663Avnika Jahan MariaNo ratings yet

- Wiley Disp Filter FinalDocument20 pagesWiley Disp Filter FinalDr. D. V. KamathNo ratings yet

- 1-S2.0-S1434841120327801-Main (1) Multiple-Input DTMOS OTADocument30 pages1-S2.0-S1434841120327801-Main (1) Multiple-Input DTMOS OTADr. D. V. KamathNo ratings yet

- Vikas Venkat Sigatapu - ECEDocument8 pagesVikas Venkat Sigatapu - ECEDr. D. V. KamathNo ratings yet

- Analysis and Modelling of CMOS GM-C Filters Through Machine LearningDocument11 pagesAnalysis and Modelling of CMOS GM-C Filters Through Machine LearningDr. D. V. KamathNo ratings yet

- A - 170907512 Siddharth Prashant KawishwarDocument13 pagesA - 170907512 Siddharth Prashant KawishwarDr. D. V. KamathNo ratings yet

- Iceca2019Document6 pagesIceca2019Dr. D. V. KamathNo ratings yet

- IEEE@HyderabadTENCON (2008) PDFDocument6 pagesIEEE@HyderabadTENCON (2008) PDFDr. D. V. KamathNo ratings yet

- Planos Electrónicos Monitor Fetal Corometrics Modelo 170 SeriesDocument88 pagesPlanos Electrónicos Monitor Fetal Corometrics Modelo 170 Seriesviviana vargasNo ratings yet

- Information Systems 363 Stair Chapter 3 11th EditionDocument55 pagesInformation Systems 363 Stair Chapter 3 11th EditionVictoria NguyenNo ratings yet

- Edwin Bohr Electronics 2015 Ecatalog1Document67 pagesEdwin Bohr Electronics 2015 Ecatalog1Ba MamadouNo ratings yet

- RepymotDocument4 pagesRepymotEngin UzunNo ratings yet

- Specification For 460 Volt MCCDocument4 pagesSpecification For 460 Volt MCCMrNo ratings yet

- Guide Manual: Analogue Fire Detection Control Panels Installation GuideDocument96 pagesGuide Manual: Analogue Fire Detection Control Panels Installation GuideMilorad PantelinacNo ratings yet

- 014 - Pressure Checking and Setting - 8 - 06-3746300enDocument26 pages014 - Pressure Checking and Setting - 8 - 06-3746300enhectorNo ratings yet

- Spec CheckDocument2 pagesSpec CheckNugroho SetioajiNo ratings yet

- TCM FB 1.8-3.5 Ton BrochureDocument7 pagesTCM FB 1.8-3.5 Ton BrochureAndy100% (1)

- Diagnostic Active CodeDocument4 pagesDiagnostic Active CodeJorge Dimitri SalNo ratings yet

- To11c5 e 00 PDFDocument526 pagesTo11c5 e 00 PDFGradimir MilanovicNo ratings yet

- Tren de Potencia d10t2Document9 pagesTren de Potencia d10t2Claudio MuñozNo ratings yet

- Topic: Identify The Front and Rear Panel Controls and Ports On A PC, Cases, Cooling, Cables and ConnectorsDocument29 pagesTopic: Identify The Front and Rear Panel Controls and Ports On A PC, Cases, Cooling, Cables and ConnectorsKkr0% (1)

- 1Document1 page1ngokhanhtNo ratings yet

- P38 EAS Service BulletinsDocument32 pagesP38 EAS Service BulletinsGerard Katchouni100% (4)

- Service Manual PDFDocument428 pagesService Manual PDFAprajita Kayastha100% (2)

- Door Inverter NSFC01-02Document39 pagesDoor Inverter NSFC01-02HƯNG NGUYỄN THANHNo ratings yet

- Yamaha Part ListDocument24 pagesYamaha Part Listjganguy2004No ratings yet

- Motor Hidrostatico SauerDocument80 pagesMotor Hidrostatico SauerAlexis Peña100% (1)

- Sony DCR Hc40Document68 pagesSony DCR Hc40Fabi PXNo ratings yet

- HPR-2Document12 pagesHPR-2v2nssysy6fNo ratings yet

- Puma 8.1 B Kit QL 8Document1 pagePuma 8.1 B Kit QL 8SaraMeineckeNo ratings yet

- Digital Motor Protection RelayDocument16 pagesDigital Motor Protection RelaySukant Kumar MohantyNo ratings yet

- Watson Marlow 3000 Series Peristaltic Pump ReportDocument2 pagesWatson Marlow 3000 Series Peristaltic Pump ReportAbilash muraliNo ratings yet

- Rheem Rged Series InstMan (EN)Document56 pagesRheem Rged Series InstMan (EN)Gisell ZapataNo ratings yet

- High Density Mono Perc Module: CS1H-325 - 330 - 335 - 340MSDocument2 pagesHigh Density Mono Perc Module: CS1H-325 - 330 - 335 - 340MSMicu RãzvanNo ratings yet

- CD13001 TRANSISTOR Datasheet PDFDocument3 pagesCD13001 TRANSISTOR Datasheet PDFmikcomiNo ratings yet

- Tactical Missile Guidance and Control: NotesDocument10 pagesTactical Missile Guidance and Control: NoteschtNo ratings yet

- Comp JKSSB Fundamentals of ComputerDocument25 pagesComp JKSSB Fundamentals of Computerreena deviNo ratings yet

- VAR Catalogue UkDocument72 pagesVAR Catalogue Ukgeisbrian1No ratings yet