Professional Documents

Culture Documents

VL Assignment 4 SP 24 FT V1

Uploaded by

Amit Halder0 ratings0% found this document useful (0 votes)

4 views1 pageCopyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

4 views1 pageVL Assignment 4 SP 24 FT V1

Uploaded by

Amit HalderCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

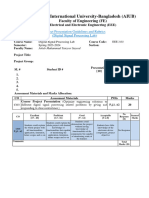

American International University- Bangladesh (AIUB)

Faculty of Engineering

Course Name: VLSI Circuit Design Course Code: EEE 4217

Semester: Spring 2023-24 Term: Final

Total Marks: 20 Submission Date: 4-05-2024

Instructor Name: Nigar Sultana Assignment: 04

Course Outcome Mapping with Questions

Obtained

Item COs POIs K P A Marks

Marks

A4 CO4 P.b.2.C4 K2 20

Total: 20

Student Information:

Student Name: Student ID:

Section: Department:

Marking Rubrics (to be filled by Faculty):

Excellent Proficient Good Acceptable Unacceptable No Response

[10] [8-9] [6-7] [4-5] [1-3] [0]

Detailed unique

No

response Response with no Partial problem is Unable to clarify

Response shows Response/(Copie Secured

Problem # explaining the apparent errors solved; response the understanding

understanding of d/identical Marks

concept properly and the answer is indicates part of of the problem and

the problem, but submissions will

and answer is correct, but the problem was method of the

the final answer be graded as 0

correct with all explanation is not not understood problem solving

may not be correct for all parties

works clearly adequate/unique. clearly. was not correct

concerned)

shown.

1

Comments Total marks (20)

1. Prepare the physical layout of a 3-input NAND gate.

(i) Show the schematic and the physical layout. Label drain and source terminals on both the diagrams.

(ii) Compute the area of the active area (in terms of λ), considering minimum length/width of polysilicon,

diffusion and metal layers are 2λ/2λ, 4λ/3λ and 3λ/3λ.

N-Diffusion P-Diffusion Polysilicon Metal1 Metal2 Via

(NMOS drain/source) (PMOS drain/source)

Consider A, B, C as inputs and Y as output.

Assuming 1λ spacing is needed between polysilicon and metal layers as well as metal1 and metal2 layers.

Note that lengths are horizontal dimension and widths are vertical dimension. [20]

You might also like

- Navneet 12th English Practice PapersDocument45 pagesNavneet 12th English Practice PapersGhanshyam Pawar92% (12)

- Fundamentals of Mixed Signals and Sensors Learning Module 1 FINAL by CORVERADocument47 pagesFundamentals of Mixed Signals and Sensors Learning Module 1 FINAL by CORVERAAdrianne Bastasa100% (5)

- Saifurs Synonym Antonym PDFDocument376 pagesSaifurs Synonym Antonym PDFAmit HalderNo ratings yet

- Assignment Mec50Document10 pagesAssignment Mec50Haziq KhaliquzzamanNo ratings yet

- CBSE Project Physics - Dry Battery ChargerDocument11 pagesCBSE Project Physics - Dry Battery ChargerTanish72% (18)

- Module in Analytic Geometry and Conic SectionCalculus1Document64 pagesModule in Analytic Geometry and Conic SectionCalculus1JESSA GRACENo ratings yet

- J STD 020CDocument20 pagesJ STD 020CJim JiangNo ratings yet

- 02-2 Excitation CourseDocument31 pages02-2 Excitation CourseFulki Kautsar S100% (1)

- DLC - Sec-R - ID-22-49373-3 1Document7 pagesDLC - Sec-R - ID-22-49373-3 1khandakersiam.skNo ratings yet

- DLC R 23-50984-1Document9 pagesDLC R 23-50984-1khandakersiam.skNo ratings yet

- Introducton of Circuit AssignmentDocument8 pagesIntroducton of Circuit AssignmentYasa Islam JunayetNo ratings yet

- American International University-Bangladesh (AIUB) Faculty of EngineeringDocument2 pagesAmerican International University-Bangladesh (AIUB) Faculty of Engineeringsowdaga mustafizur rahman0% (1)

- Assignment - 1 - OBE - ED Summer 2020 - 21Document2 pagesAssignment - 1 - OBE - ED Summer 2020 - 21Arifin HussainNo ratings yet

- Assignment - 1 - Final OBE - ED Spring 2020 - 21Document8 pagesAssignment - 1 - Final OBE - ED Spring 2020 - 21Rohan RashidNo ratings yet

- Final AssignmentDocument3 pagesFinal AssignmentA. AbirNo ratings yet

- Universiti Teknologi Mara Assignment 1 Course: Numerical Methods With Applications Course Code: MEC500 Deadline: Week 7 Mode: Individual AssignmentDocument5 pagesUniversiti Teknologi Mara Assignment 1 Course: Numerical Methods With Applications Course Code: MEC500 Deadline: Week 7 Mode: Individual AssignmentFadhli HashimNo ratings yet

- OBE Assignment ED Fall 2022 23 MidDocument2 pagesOBE Assignment ED Fall 2022 23 MidPritam ChakrabortyNo ratings yet

- Rubrics Index F.Y.B.tech.,SEM II, 2021 2022Document1 pageRubrics Index F.Y.B.tech.,SEM II, 2021 2022shubham nikatNo ratings yet

- OBE Assignment - MD Abu Hanif - 18-38397-2Document17 pagesOBE Assignment - MD Abu Hanif - 18-38397-2Abu hanif RobinNo ratings yet

- Course Plan: Engg - Mathematics I & MAT 1151 I&Document5 pagesCourse Plan: Engg - Mathematics I & MAT 1151 I&Crimson BladeNo ratings yet

- 2020 Specimen Paper 2 Mark SchemeDocument10 pages2020 Specimen Paper 2 Mark SchemeTOMMY-GUNNNo ratings yet

- Course Plan: Enter Name of The FacultyDocument5 pagesCourse Plan: Enter Name of The FacultyPavan KnvsNo ratings yet

- Maths 4 Course PlanDocument5 pagesMaths 4 Course PlanShryNo ratings yet

- Vidyavardhaka College of Engineering, Mysore - 570 002: First ModuleDocument1 pageVidyavardhaka College of Engineering, Mysore - 570 002: First ModuleMansi ANo ratings yet

- Week 4 Course OutcomesDocument4 pagesWeek 4 Course Outcomesjagadeesh.kantamsettiNo ratings yet

- Emop - Obe Assignment - F - Nahin Akhtar - 17-34113-1Document14 pagesEmop - Obe Assignment - F - Nahin Akhtar - 17-34113-1Na HinNo ratings yet

- EPOM F OBE ASSIGNMENT Shuvro Sankar Sen 18-37524-1Document7 pagesEPOM F OBE ASSIGNMENT Shuvro Sankar Sen 18-37524-1Shuvro Sankar SenNo ratings yet

- 1920 - Mock - S6MA (M2) - v1 (Q&A BK)Document28 pages1920 - Mock - S6MA (M2) - v1 (Q&A BK)pgpcj68rsqNo ratings yet

- Technological Institute of The PhilippinesDocument11 pagesTechnological Institute of The Philippinesalyssa babylaiNo ratings yet

- Assignment Ecw341Document11 pagesAssignment Ecw341A'ziemullah UmarNo ratings yet

- Dap An Vong 2 FinalDocument2 pagesDap An Vong 2 FinalTú NgânNo ratings yet

- u+v=u.v, ∀ u,v ε R αu = u, ∀ u ε R, α ε R,Document2 pagesu+v=u.v, ∀ u,v ε R αu = u, ∀ u ε R, α ε R,Tanos 46No ratings yet

- Assignment 2 Oct2021 - SmarDocument5 pagesAssignment 2 Oct2021 - SmarCt NhalizaNo ratings yet

- DSE 2155 DS Course Plan August 2022Document5 pagesDSE 2155 DS Course Plan August 2022Aditya PatelNo ratings yet

- EDTC Assignement 1Document1 pageEDTC Assignement 1tf9wgz2ysdNo ratings yet

- Course Plan: at The End of This Course, The Student Should Be Able ToDocument5 pagesCourse Plan: at The End of This Course, The Student Should Be Able TosuriNo ratings yet

- Student Declaration: - , I Will NotDocument7 pagesStudent Declaration: - , I Will NotMuhammad AhMadNo ratings yet

- Assingment SCOMP Ninja L1D3Document7 pagesAssingment SCOMP Ninja L1D3MUHAMMAD AKMAL BIN ZAHARI A21HP0076No ratings yet

- Cambridge IGCSE™: English As A Second Language (Speaking Endorsement) 0510/22 March 2020Document10 pagesCambridge IGCSE™: English As A Second Language (Speaking Endorsement) 0510/22 March 2020Prince YugNo ratings yet

- Universiti Kuala Lumpur: Malaysian Institute of Information TechnologyDocument4 pagesUniversiti Kuala Lumpur: Malaysian Institute of Information TechnologyHT Fyahya YahyaNo ratings yet

- Paper Pattern All Subjects X 2025Document7 pagesPaper Pattern All Subjects X 2025Dipti GargNo ratings yet

- Hmef5053 - Measurement and Evaluation in EducationDocument7 pagesHmef5053 - Measurement and Evaluation in EducationCikgu WanNo ratings yet

- Course Plan Maths Iii 2022Document5 pagesCourse Plan Maths Iii 2022abhiyendraNo ratings yet

- TGDA Salman AL-FarisiDocument8 pagesTGDA Salman AL-FarisiSalman Al-FarisiNo ratings yet

- Course Plan: Data Structures and Algorithms & ECE 4070 &Document5 pagesCourse Plan: Data Structures and Algorithms & ECE 4070 &Eswar RajeshNo ratings yet

- Testing & Evaluation (Test Construction)Document68 pagesTesting & Evaluation (Test Construction)基岡No ratings yet

- Assignment HBET2103 Grammar in Esl January 2023 Semester - Specific InstructionsDocument7 pagesAssignment HBET2103 Grammar in Esl January 2023 Semester - Specific InstructionsAtiq MydNo ratings yet

- Mathematical Methods 2020 Unit 2 Trial Exam 2Document18 pagesMathematical Methods 2020 Unit 2 Trial Exam 2uyenkhuu06No ratings yet

- NYC Sample Final and AnswersDocument14 pagesNYC Sample Final and AnswersAlexander PughNo ratings yet

- Universiti Teknologi Mara Assignment Course: Numerical Methods With Applications Course Code: MEC500 Deadline: ModeDocument12 pagesUniversiti Teknologi Mara Assignment Course: Numerical Methods With Applications Course Code: MEC500 Deadline: ModeSyara RosmanNo ratings yet

- Course Outline MAT 250.9 Spring 2022Document4 pagesCourse Outline MAT 250.9 Spring 2022Jubayer HussainNo ratings yet

- Assessmen Format Law299 March 2021 (Student)Document3 pagesAssessmen Format Law299 March 2021 (Student)Zasfira NafisahNo ratings yet

- Question Paper Design: Subject: Data Entry Operations Marks: 40 Class: Senior Secondary Duration: 2 HoursDocument2 pagesQuestion Paper Design: Subject: Data Entry Operations Marks: 40 Class: Senior Secondary Duration: 2 HoursRadhika J UdeshiNo ratings yet

- Maths Model QP 2018-19Document15 pagesMaths Model QP 2018-19GDNo ratings yet

- Computing 2Document8 pagesComputing 2Harley CleshaNo ratings yet

- Achievement Test Analysis - Class VI - Sonal JainDocument10 pagesAchievement Test Analysis - Class VI - Sonal JainabhayNo ratings yet

- DSP - Lab - Project - Spring 23 - 24Document2 pagesDSP - Lab - Project - Spring 23 - 24Sadman HossainNo ratings yet

- Teaching and Learning in Engineering (TALE) - Unit 6 - Week 4 Course OutcomesDocument4 pagesTeaching and Learning in Engineering (TALE) - Unit 6 - Week 4 Course OutcomesngguptaNo ratings yet

- Class VIII ResonanceDocument13 pagesClass VIII Resonancebiren71No ratings yet

- CP CD PDFDocument5 pagesCP CD PDFCr FanNo ratings yet

- NOTA Teknik Menjawab KimiaDocument18 pagesNOTA Teknik Menjawab KimiaSHARIN HANUM AB RAHMANNo ratings yet

- June 2004MS p2Document21 pagesJune 2004MS p2Hany El-GezawyNo ratings yet

- MGMT3000 2020 S2 Final ExamDocument4 pagesMGMT3000 2020 S2 Final ExamhaohtsNo ratings yet

- VL Assignment 3 SP 24 FT V1Document1 pageVL Assignment 3 SP 24 FT V1Amit HalderNo ratings yet

- World University of Bangladesh: (Answer Any 4 (Four) Questions From The Following 5 (Five) Questions)Document1 pageWorld University of Bangladesh: (Answer Any 4 (Four) Questions From The Following 5 (Five) Questions)Amit HalderNo ratings yet

- 67A Final QuestionDocument1 page67A Final QuestionAmit HalderNo ratings yet

- Jacobian MatrixDocument1 pageJacobian MatrixAmit HalderNo ratings yet

- Jacob NadiaDocument1 pageJacob NadiaAmit HalderNo ratings yet

- Sameya Priom: Heritage, Flat # 4B, House # 18/a, Road #-03, Banani DOHS, Dhaka Cantonment, Dhaka. 01730002097Document5 pagesSameya Priom: Heritage, Flat # 4B, House # 18/a, Road #-03, Banani DOHS, Dhaka Cantonment, Dhaka. 01730002097Amit HalderNo ratings yet

- BCS MathDocument32 pagesBCS MathAmit HalderNo ratings yet

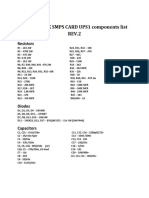

- Modified CRYSTAL 40ZX SMPS & DC To DC Conv Comp ListDocument3 pagesModified CRYSTAL 40ZX SMPS & DC To DC Conv Comp ListArokiaraj Raj100% (1)

- IR Dan NMR Spectrum ParacetamolDocument12 pagesIR Dan NMR Spectrum ParacetamolHey It's Me DaisyNo ratings yet

- NTPCDocument4 pagesNTPCSriram VenkatachariNo ratings yet

- Logic Gate, Types With Symbols, Truth Tables EtcDocument6 pagesLogic Gate, Types With Symbols, Truth Tables EtcChidinma Glory EjikeNo ratings yet

- Pvi 55Document8 pagesPvi 55dnyfvxNo ratings yet

- Presented by : PHYSICS THEORY (232/1&2)Document41 pagesPresented by : PHYSICS THEORY (232/1&2)Bonface KenaniNo ratings yet

- Unit 2 Converters (Half Controlled)Document52 pagesUnit 2 Converters (Half Controlled)Tenzin JamtshoNo ratings yet

- 7TS16 Annunciation Relay: Function OverviewDocument2 pages7TS16 Annunciation Relay: Function OverviewVictor Manuel BonettoNo ratings yet

- Infrared and Thermal SensorsDocument12 pagesInfrared and Thermal SensorsClay Mark SarteNo ratings yet

- Complementary Silicon Power Transistors: BD241BFP BD242BFPDocument4 pagesComplementary Silicon Power Transistors: BD241BFP BD242BFPLeonel PedronNo ratings yet

- EV Charging: Power Electronics at The PumpDocument3 pagesEV Charging: Power Electronics at The PumpluongktdtNo ratings yet

- Reverse Polarity Protection CircuitDocument8 pagesReverse Polarity Protection CircuittongaiNo ratings yet

- Synthesis of Inorganic Solids Using MicrowavesDocument14 pagesSynthesis of Inorganic Solids Using MicrowavesMuaathe IbrahimNo ratings yet

- AMD Ryzen™ 5 2400G With Radeon™ RX Vega 11 Graphics - AMDDocument8 pagesAMD Ryzen™ 5 2400G With Radeon™ RX Vega 11 Graphics - AMDSiva NeshNo ratings yet

- Euler S Path and Stick DiagramDocument12 pagesEuler S Path and Stick Diagramdsweetalker50% (2)

- Teshmont BrochureDocument30 pagesTeshmont BrochureMurugan100% (1)

- Ujt Circuits - Power ElectronicsDocument7 pagesUjt Circuits - Power ElectronicsMoh OkoeNo ratings yet

- 6-SiFive Promotes RISC-V 20190905Document29 pages6-SiFive Promotes RISC-V 20190905nauman wazirNo ratings yet

- Lab ReportDocument7 pagesLab ReportRehanNasirNo ratings yet

- Eee111 Experiment 3 (Lab Report)Document4 pagesEee111 Experiment 3 (Lab Report)Amirul 0205No ratings yet

- ECE CA Question PaperDocument2 pagesECE CA Question PaperHarsh RajNo ratings yet

- C2 Cadence Transistor Level EMIR SolutionDocument26 pagesC2 Cadence Transistor Level EMIR SolutionYogesh GaidhaneNo ratings yet

- (전자기학 jackson 솔루션) 전자기학 jackson 솔루션 65 4000 PDFDocument65 pages(전자기학 jackson 솔루션) 전자기학 jackson 솔루션 65 4000 PDFgbsNo ratings yet

- Caribbean Examinations Council: Caribbean Secondary Education Certificate ExaminationDocument24 pagesCaribbean Examinations Council: Caribbean Secondary Education Certificate ExaminationMarco McleanNo ratings yet

- Chapter 2 CapstoneDocument3 pagesChapter 2 Capstonematt bianzonNo ratings yet

- Introduction To MEMS Lecture 4Document12 pagesIntroduction To MEMS Lecture 4Vaibhav ChaudharyNo ratings yet