Professional Documents

Culture Documents

Operation Mode: nMOS Operation Mode: pMOS: CMOS Inverter: Transient Response

Operation Mode: nMOS Operation Mode: pMOS: CMOS Inverter: Transient Response

Uploaded by

Raja GopalOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Operation Mode: nMOS Operation Mode: pMOS: CMOS Inverter: Transient Response

Operation Mode: nMOS Operation Mode: pMOS: CMOS Inverter: Transient Response

Uploaded by

Raja GopalCopyright:

Available Formats

1

3 March 2009 1

Gate

Source

Drain

Ids

Operation Mode: nMOS

VGS < Vtn

Gate

Source

Drain

Ids

VGS > Vtn

VGD > Vtn

Gate

Source

Drain

Ids

VGS > Vtn

VGD < Vtn

Cutoff

Linear

Saturation

(

=

2

) (

2

DS

DS T GS n DS

V

V V V k I

2

) (

2

T GS

n DS

V V

k I

= 0 =

DS

I

3 March 2009 2

Gate

Source

Drain

Ids

Operation Mode: pMOS

VGS < Vtp

VGD < Vtp

Gate

Source

Drain

Ids

VGS < Vtp

VGD > Vtp

Gate

Source

Drain

Ids

VGS > Vtp

Cutoff

Linear

Saturation

(

=

2

) (

2

DS

DS T GS

p

DS

V

V V V k I

2

) (

2

T GS

p DS

V V

k I

= 0 =

DS

I

3 March 2009 3

Gate

Source

Drain

Ids

Operation Region: pMOS

VGS < Vtp

VGD < Vtp

Gate

Source

Drain

Ids

VGS < Vtp

VGD > Vtp

Gate

Source

Drain

Ids

VGS > Vtp

Cutoff

Linear

Saturation

0 =

DS

I

(

=

2

) (

2

DS

DS T GS

p

DS

V

V V V k I

2

) (

2

T GS

p DS

V V

k I

=

3 March 2009 4

CMOS Inverter

First-Order DC Analysis

Vin = 0 Vin = VDD

High noise margin

Ratioless

low output impedance

extremely high input impedance

no static power

Vin Vout

VDD

3 March 2009 5

CMOS Inverter: Transient Response

Vin = VDD 0 Vin = 0 VDD

Low-to-High High-to-Low

To reduce delay:

Reduce CL

Reduce Rp,n

Increase W/L ratio

Output:

CL is composed of the drain diffusion capacitances of the NMOS and PMOS transistors,

the capacitance of connecting wires, and the input capacitance of the fan-out gates

3 March 2009 6

NMOS Load Lines

0 0.5 1 1.5 2 2.5

0

1

2

3

4

5

6

x 10

-4

V

DS

(V)

I D

S

(

A

)

VGS= 2.5 V

VGS= 2.0 V

VGS= 1.5 V

VGS= 1.0 V

Linear Saturation

V

DS

= V

GS

- V

T

2

3 March 2009 7

PMOS Load Lines

Vin Vout

VDD

3 March 2009 8

CMOS Inverter Load Characteristics

3 March 2009 9

CMOS Inverter VTC

VTC: Voltage-Transfer

Characteristic

3 March 2009 10

CMOS Inverter VTC

Vtn Vin

Vout

VDD

Vin Vout

VDD

S

S

D

D

G

G

3 March 2009 11

CMOS Inverter VTC

Vtn Vin

VDD

Vout

Vout - |Vtp|

Vin Vout

VDD

S

S

D

D

G

G

3 March 2009 12

CMOS Inverter VTC

Set pMOS Linear I

DS

equal to nMOS

Saturation I

DS

( )

|

|

\

|

=

|

|

\

|

2

) (

) )( (

2

2 2

DD out

DD out tp DD in p

tn in

n

V V

V V V V V k

V V

k

( )

0

2

) )( (

2

) (

2 2

=

tn in

p

n

DD out tp DD in

DD out

V V

k

k

V V V V V

V V

( )

2 2

) ( ) ( ) (

tn in

p

n

tp DD in tp DD in DD out

V V

k

k

V V V V V V V V + =

( )

2 2

) ( ) (

tn in

p

n

tp DD in tp in out

V V

k

k

V V V V V V + =

3

3 March 2009 13

CMOS Inverter VTC

Vtn

VDD

Vout

Vout - |Vtp| Vout + Vtn

Vin

Vin Vout

VDD

S

S

D

D

G

G

3 March 2009 14

CMOS Inverter VTC

Vtn

VDD

Vout

Vout - |Vtp| Vout + Vtn

Vtn VDD - |Vtp| Vin

Vin Vout

VDD

S

S

D

D

G

G

3 March 2009 15

CMOS Inverter VTC

Set nMOS Linear I

DS

equal to pMOS

Saturation I

DS

( )

( )

|

|

\

|

=

|

|

\

|

2 2

2

2

out

out tn in n

tp DD in

p

V

V V V k

V V V

k

( )

( )

0

2 2

2

2

=

+

tp DD in

n

p

out tn in

out

V V V

k

k

V V V

V

( ) ( ) ( )

2 2

tp DD in

n

p

tn in tn in out

V V V

k

k

V V V V V =

3 March 2009 16

CMOS Inverter VTC

Vtn

VDD

Vout

Vout - |Vtp| Vout + Vtn

Vtn VDD - |Vtp| Vin

VDD

Vin Vout

VDD

S

S

D

D

G

G

3 March 2009 17

CMOS Inverter VTC

VDD

Vin

Vout

VDD

3 March 2009 18

CMOS Inverter

(assume Vt = Vtn = |Vtp|)

4

3 March 2009 19

Switching Threshold

The point (V

m

) at which the inverter has

both transistors in saturation (V

in

= V

out

)

2 2

) (

2

) (

2

tp DD M

p

tn M

n

V V V

k

V V

k

=

) ( ) (

tp DD M

n

p

tn M

V V V

k

k

V V =

) ( ) 1 (

tp DD tn M

V V r V r V + + = +

r

V V r V

V

tp DD tn

M

+

+ +

=

1

) (

r is the relative driving strengths of the PMOS and NMOS transistors

r

3 March 2009 20

Switching Threshold

When V

tn

= -V

tp

and r = 1,

When V

tn

= -V

tp

and r > 1,

r

V V r V

V

tp DD tn

M

+

+ +

=

1

) (

2

DD

M

V

V =

2

DD

M

V

V >

Stronger PMOS

3 March 2009 21

0

0.5

1

1.5

2

2.5

0 0.5 1 1.5 2 2.5

V

in

(V)

V

o

u

t

(

V

)

Balanced

Strong PMOS

Strong NMOS

Switching Threshold

3 March 2009 22

Noise Margin

A measure of the acceptable noise at a gate

input so that the output is not affected.

Noise margin is closely related to the DC

voltage characteristics

Sources: supply noise, crosstalk,

interference

3 March 2009 23

Noise Margin

VOLmax: Maximum low

output voltage produced

by the driving gate

VILmax: Maximum low input

voltage recognized by the

receiving gate

Low Noise Margin

High Noise Margin

Logical Low Input Voltage

Logical Low Output Voltage

Output

Characteristics

Input

Characteristics

3 March 2009 24

Noise Margins

Voltage Transfer Function

Voltage Transfer Function with Noise

Perturbed voltage is the sum of the nominal

output plus the gain times the noise

Keep the gain less than 1

) (

in out

V f V =

) (

noise in out

V V f V + =

noise

in

out

in out

V

dV

dV

V f V + ) (

5

3 March 2009 25

Noise Margins

VDD

Vin

Vout

VDD

VOH

VOL

Undefined region

VIL

VIH

3 March 2009 26

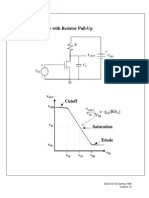

Static Load Inverter

3 March 2009 27

Static Load Inverter

3 March 2009 28

Static Load Inverter

Linear

Mode

3 March 2009 29

Static Load Inverter

Transistor is in linear region

(

=

2

) (

2

DS

DS T GS n DS

V

V V V k I

(

=

2

) (

2

OUT

OUT T IN n DD OUT

V

V V V Rk V V

0 ) 1 ) ( (

2

2

= + +

DD OUT T IN n OUT

n

V V V V Rk V

Rk

( )

n

DD

n

T IN

n

T IN OUT

Rk

V

Rk

V V

Rk

V V V 2

1 1

) (

2

|

|

\

|

+ + =

3 March 2009 30

Static Load Inverter

6

3 March 2009 31

Static Load Inverter

Transistor is in saturation

) 1 (

2

) (

2

DS

T GS

n DS

V

V V

k I +

=

) 1 (

2

) (

2

OUT

T IN

n DD OUT

V

V V

Rk V V +

=

2

2

) ( 2

) ( 2

T IN n

T IN n DD

OUT

V V Rk

V V Rk V

V

+

=

3 March 2009 32

Static Load Inverter

V

OH

V

OL

Undefined region

3 March 2009 33

Static Load Inverter

Does not go down all the way to 0 due to

the resistance path between V

DD

and

ground when nMOS is on

Static power

Noise margins are tighter

Switching threshold is not centered

To get high gain in the transition region,

bigger resistors are needed

You might also like

- Iso 228 1Document12 pagesIso 228 1andy100% (1)

- SAU DescriptionDocument11 pagesSAU Descriptionдмитрий ивановNo ratings yet

- Interconnect Delay Interconnect Delay: Lumped RC ModelDocument6 pagesInterconnect Delay Interconnect Delay: Lumped RC ModelLava Kumar BNo ratings yet

- Review: ASIC Design CMOS Delay EquationsDocument32 pagesReview: ASIC Design CMOS Delay EquationsSurya KanthNo ratings yet

- Lect 07 Differential AmpDocument36 pagesLect 07 Differential AmpRogerZhangNo ratings yet

- I. Mosfet Circuit Models A. Large Signal Model - Nmos: Vgs VTN Id Vgs VTN Vds Vgs VTNDocument10 pagesI. Mosfet Circuit Models A. Large Signal Model - Nmos: Vgs VTN Id Vgs VTN Vds Vgs VTNmanohar487No ratings yet

- Lecture17 Ee474 Folded Cascode OtaDocument17 pagesLecture17 Ee474 Folded Cascode OtaRinkitori NorikarinNo ratings yet

- P.R. Gray, "Analysis and Design of Analog Integrated Circuits", 4.3.5, 6.2 6.3Document70 pagesP.R. Gray, "Analysis and Design of Analog Integrated Circuits", 4.3.5, 6.2 6.3Yeu academiaNo ratings yet

- Lecturer On Mos InverterDocument24 pagesLecturer On Mos InvertersoumikbhNo ratings yet

- 9085 CMOS Analog Design Chapter 5Document25 pages9085 CMOS Analog Design Chapter 5istlyyNo ratings yet

- S98 Lecture12Document11 pagesS98 Lecture12manohar487No ratings yet

- Mosfet Transistor Equations: University of Edinburgh EE4 Electrical EngineeringDocument5 pagesMosfet Transistor Equations: University of Edinburgh EE4 Electrical EngineeringShachi P GowdaNo ratings yet

- Simplified CMOS Voltage Transfer Curve Step 1. Finding V: M M IN MDocument6 pagesSimplified CMOS Voltage Transfer Curve Step 1. Finding V: M M IN MSeizalal SingsonNo ratings yet

- Formula SheetDocument1 pageFormula SheetChika OfiliNo ratings yet

- MOSFET Structure: Source Gate Drain Field Oxide Gate OxideDocument12 pagesMOSFET Structure: Source Gate Drain Field Oxide Gate OxideRaj HakaniNo ratings yet

- Cmos InverterDocument92 pagesCmos Invertersreekanthreddy peramNo ratings yet

- Esc201: Introduction To Electronics: Operational Amplifier Operational Amplifier Part 2Document26 pagesEsc201: Introduction To Electronics: Operational Amplifier Operational Amplifier Part 2egupta1No ratings yet

- Tutorial 5 SolutionsDocument11 pagesTutorial 5 SolutionsbarneyNo ratings yet

- CMOS Inverter Amplifier:) 0 (Or Z Y) (Or Z 0 Y V V V V VDocument13 pagesCMOS Inverter Amplifier:) 0 (Or Z Y) (Or Z 0 Y V V V V VomenderNo ratings yet

- EE42 100 Wb-Lecture18 080513-FDocument44 pagesEE42 100 Wb-Lecture18 080513-FozanistzNo ratings yet

- n-MOSFET (D) :: (I-V) Equations: Cut Off ModeDocument6 pagesn-MOSFET (D) :: (I-V) Equations: Cut Off ModeJo KontNo ratings yet

- CMOS Logic Gates: Gagandeep SinghDocument37 pagesCMOS Logic Gates: Gagandeep SinghGagandeep Singh Dhingra100% (1)

- CMOS Inverter Cmosinv: DescriptionDocument3 pagesCMOS Inverter Cmosinv: DescriptionCherry AbhiNo ratings yet

- 9309 - CMOS Analog Design Chapter 8Document54 pages9309 - CMOS Analog Design Chapter 8raju.kprr8862No ratings yet

- EE5518 VLSI Digital Circuit Design VLSI Digital Circuit DesignDocument39 pagesEE5518 VLSI Digital Circuit Design VLSI Digital Circuit DesignBharat Kumar100% (1)

- Bias Circuits: Kanazawa University Microelectronics Research Lab. Akio KitagawaDocument22 pagesBias Circuits: Kanazawa University Microelectronics Research Lab. Akio Kitagawapani256No ratings yet

- N Channel MOSFET Level 1Document5 pagesN Channel MOSFET Level 1Kyusang ParkNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument78 pagesDigital Integrated Circuits: A Design Perspectiveدانشجویان فوق لیسانس الکترونیک 91 سیرجانNo ratings yet

- Chapter 2 MOS Transistor TheoryDocument25 pagesChapter 2 MOS Transistor TheoryrasheeenNo ratings yet

- Small Signal Operation and Model: Assignment-3Document15 pagesSmall Signal Operation and Model: Assignment-3Keshavamurthy LNo ratings yet

- The Cmos Inverter: OutlineDocument20 pagesThe Cmos Inverter: OutlinehappyharrNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument78 pagesDigital Integrated Circuits: A Design Perspectiveapi-127299018No ratings yet

- Formulas 2010Document2 pagesFormulas 2010Matthew PerryNo ratings yet

- 3.1. Resistive Load Mos Inverter: An ExampleDocument41 pages3.1. Resistive Load Mos Inverter: An Exampleerdem10139No ratings yet

- Amplitude ModulationDocument76 pagesAmplitude Modulationyogitom81No ratings yet

- Small Signal Operation and Model: Assignment-3Document15 pagesSmall Signal Operation and Model: Assignment-3Keshavamurthy LNo ratings yet

- Pcirf 3 3 Mos 2Document25 pagesPcirf 3 3 Mos 2Marius FerdyNo ratings yet

- CmosDocument14 pagesCmosJannathul Firdous MohamedNo ratings yet

- Series: ApplicationsDocument22 pagesSeries: ApplicationsAnildo Eldivar De Oliveira SarmentoNo ratings yet

- Mosfet 01Document56 pagesMosfet 01Edward Allan MangubatNo ratings yet

- Cobep2013 Plenary Humperto PinheiroDocument200 pagesCobep2013 Plenary Humperto PinheiroedsonacordiNo ratings yet

- Current Sources, Current Sinks and Current MirrorsDocument27 pagesCurrent Sources, Current Sinks and Current MirrorsÂnuradha ÐăßĭNo ratings yet

- 2N3819Document5 pages2N3819Rifki AsfariNo ratings yet

- Ecen 5355 L13Document3 pagesEcen 5355 L13alimapecuNo ratings yet

- Amplifier Biasing TechniquesDocument3 pagesAmplifier Biasing TechniquesMagnanil GoswamiNo ratings yet

- CMOS InverterDocument16 pagesCMOS Invertersreekanthreddy peramNo ratings yet

- Class-A Source Follower With External Resistor Output StageDocument23 pagesClass-A Source Follower With External Resistor Output StagelaksologinNo ratings yet

- MDD3752 PDFDocument6 pagesMDD3752 PDFsonytel2No ratings yet

- Cmos Inverter CharacterizationDocument54 pagesCmos Inverter CharacterizationVivekNo ratings yet

- ECE 5202: Integrated Circuit Microfabrication Gated Diode MOS Capacitor MOS Field Effect TransistorsDocument33 pagesECE 5202: Integrated Circuit Microfabrication Gated Diode MOS Capacitor MOS Field Effect TransistorsSuma VimalNo ratings yet

- Inverter NmosDocument124 pagesInverter Nmosapoorva10393No ratings yet

- Field Effect TransistorsDocument40 pagesField Effect TransistorsRatanNo ratings yet

- KNL4343 VLSI Design and Technology Lecture 04: CMOS Inverter (Static View)Document23 pagesKNL4343 VLSI Design and Technology Lecture 04: CMOS Inverter (Static View)yikamnnNo ratings yet

- (Vishay Siliconix) 2N4393Document6 pages(Vishay Siliconix) 2N4393SevenUp2014No ratings yet

- Cascode Amplifier: VDD VG3 VDD - VTP0 - + - VDocument29 pagesCascode Amplifier: VDD VG3 VDD - VTP0 - + - VSyed Maqsood AliNo ratings yet

- Devices and Circuits Ii: Small Signal Parameters of MOSFETDocument5 pagesDevices and Circuits Ii: Small Signal Parameters of MOSFETMạnh Cường TrầnNo ratings yet

- ELEC 3400 VI. Operational Amplifiers: 1. MOS Differential Pair With Resistive LoadsDocument21 pagesELEC 3400 VI. Operational Amplifiers: 1. MOS Differential Pair With Resistive Loadskidus100% (1)

- ENEE 3543 - Homework 4 - SolutionsDocument4 pagesENEE 3543 - Homework 4 - SolutionsTSwayNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsRating: 5 out of 5 stars5/5 (1)

- EN1803 Workshop 03Document3 pagesEN1803 Workshop 03kavindawickramasinghe.uniNo ratings yet

- Amir FarooqiDocument3 pagesAmir FarooqiMuhammadwaqasnaseemNo ratings yet

- Stacked Reservoirs Development Optimization Technical PaperDocument1 pageStacked Reservoirs Development Optimization Technical PaperJoy FaruzNo ratings yet

- EDA Lesson 4Document2 pagesEDA Lesson 4Cathrina ClaveNo ratings yet

- CTR 8500-8300 3.5.20 RMON2 CLI Commands - January2018Document10 pagesCTR 8500-8300 3.5.20 RMON2 CLI Commands - January2018Sandra Milena ViracachaNo ratings yet

- OuiDocument1,628 pagesOuiSev HuangNo ratings yet

- Prem CVDocument3 pagesPrem CVengineeringwatchNo ratings yet

- PIM - Data HubDocument3 pagesPIM - Data Hubmdfaraz55No ratings yet

- Net E-Business ArchitectureDocument463 pagesNet E-Business Architecturedharbab100% (1)

- 如何为报告撰写执行摘要Document10 pages如何为报告撰写执行摘要snaznkmpdNo ratings yet

- Manual Tecnico Bulletplusac-Cat9Document211 pagesManual Tecnico Bulletplusac-Cat9Dante FalconNo ratings yet

- Ananya Cisco Networking Academy Coures ListDocument8 pagesAnanya Cisco Networking Academy Coures ListSAURAV kumarNo ratings yet

- 11th Bipartite Arrears Calculation Package - Clerk: How To Use This PackageDocument12 pages11th Bipartite Arrears Calculation Package - Clerk: How To Use This PackageKshitij GulatiNo ratings yet

- 11 - Wiring DiagramDocument8 pages11 - Wiring DiagramAivars LīpenītsNo ratings yet

- Gis ProcessingDocument46 pagesGis Processingsamosir123xxxxNo ratings yet

- CITROEN C4 BrochureDocument36 pagesCITROEN C4 Brochurenloukis236No ratings yet

- Case Study-Whatsapp Pay-Cohort 3Document14 pagesCase Study-Whatsapp Pay-Cohort 3BRANDEB CONSULTING100% (1)

- Adv Job SchedulerDocument38 pagesAdv Job SchedulerradhagopalamkvNo ratings yet

- DIGICO SD7 BrochureDocument40 pagesDIGICO SD7 BrochureDave Ruiz HernandezNo ratings yet

- Hemant Kumar: ObjectiveDocument2 pagesHemant Kumar: ObjectiveChandan PandeyNo ratings yet

- Institute of Technology: Practical ListDocument4 pagesInstitute of Technology: Practical ListAlex TiwariNo ratings yet

- Arup Paper On CFD For Tsinghua University CFD Seminar1-45Document10 pagesArup Paper On CFD For Tsinghua University CFD Seminar1-45voldumvejNo ratings yet

- Central Battery System ZB-S: © 2014 Eaton, All Rights ReservedDocument41 pagesCentral Battery System ZB-S: © 2014 Eaton, All Rights ReservedEmmanuel ToretaNo ratings yet

- ITL PVBX Systems - Sample QuotesDocument2 pagesITL PVBX Systems - Sample QuotesKevin LathamNo ratings yet

- List of Partner 3 2012Document157 pagesList of Partner 3 2012minhdung.pham4713100% (1)

- EC Experiment No 4Document3 pagesEC Experiment No 4Aryan KukretiNo ratings yet

- Grade 12 Ict Work Immersion Narrative Report: Week 1/february 27-March 03 2023Document35 pagesGrade 12 Ict Work Immersion Narrative Report: Week 1/february 27-March 03 2023julita pelovelloNo ratings yet

- Wso psr3 Guide To Work Final 6Document21 pagesWso psr3 Guide To Work Final 6api-286185563No ratings yet