Professional Documents

Culture Documents

An 4134 (Forward)

An 4134 (Forward)

Uploaded by

rrrrrrrrrrqCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

An 4134 (Forward)

An 4134 (Forward)

Uploaded by

rrrrrrrrrrqCopyright:

Available Formats

Appl i c at i on Not e AN4134

Desi gn Gui del i nes f or Of f -l i ne For war d Conver t er s

Usi ng Fai r c hi l d Power Sw i t ch (FPS

TM

)

www.fairchildsemi.com

2003 Fairchild Semiconductor Corporation

Abstract

This paper presents practical design guidelines for off-line

forward converter employing FPS (Fairchild Power Switch).

Switched mode power supply (SMPS) design is inherently a

time consuming job requiring many trade-offs and iteration

with a large number of design variables.

The step-by-step design procedure described in this paper

helps the engineers to design a SMPS easily. In order to

make the design process more efficient, a software design

tool, FPS design as sistant, that contains all the equations

described in this paper, is also provided.

Rev. 1.0.0

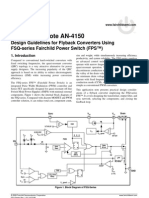

1. Introduction

Due to circuit simplicity, the forward converter has been

widely used for low to medium power conversion

applications. Figure 1 shows the schematic of the basic off-

line forward converter using FPS, which also serves as the

reference circuit for the design procedure described in this

paper. Because the MOSFET and PWM controller together

with various additional circuits are integrated into a single

package, the design of SMPS is much easier than the discrete

MOSFET and PWM controller solution.

This paper provides step-by-step design procedure for an

FPS based off-line forward converter, which includes

transformer

design, reset circuit design, output filter design, component

selection and closing the feedback loop. The design

procedure described herein is general enough to be applied

to various applications. The design procedure presented in

this paper is also implemented in a software design tool (FPS

design assistant) to enable the engineer to finish SMPS

design in a short time. In the appendix, a step-by-step design

example using the software tool is provided.

Np

N

S1

+

V

DC

-

AC line

D

R1

C

O1

Drain

Vcc

GND FB

FPS

NTC Fuse

R

L1

C

L1

Line Filter

C

L2

N

a

D

a

R

a

C

a

KA431

817A

R

d R

bias

R

1

R

2

R

F C

F

Bridge

rectifier

diode

V

O1

L

1

C

B

2C

DC N

S2

D

R2

V

O2

L

2

D

F2

D

F1

C

O2

2C

DC

Non-doubled

Doubled

Reset Circuit

C

p1

L

p1

C

p2

L

p2

Figure 1. Basic Off-line Forward Converter Using FPS

AN4134 APPLICATION NOTE

2

2002 Fairchild Semiconductor Corporation

2. Step-by-step Design Procedure

In this section, design procedure is presented using the

schematic of the figure 1 as a reference. In general, most FPS

has the same pin configuration from pin 1 to pin 4, as shown

in figure 1.

(1) STEP-1 : Determine the system specifications

- Line voltage range (V

line

min

and V

line

max

) : Usually, voltage

doubler circuit as shown in figure 1 is used for a forward

converter with universal input. Then, the minimum line

voltage is twice the actual minimum line voltage.

- Line frequency (f

L

).

- Maximum output power (P

o

).

- Estimated efficiency (E

ff

) : It is required to estimate the

power conversion efficiency to calculate the maximum input

power. If no reference data is available, set E

ff

= 0.7~0.75 for

low voltage output applications and E

ff

= 0.8~0.85 for high

voltage output applications.

With the estimated efficiency, the maximum input power is

given by

Considering the maximum input power, choose the proper

FPS. Since the voltage stress on the MOSFET is about twice

the input voltage in the case of the forward converter, an FPS

with 800V rated MOSFET is recommended for universal

input voltage. The FPS lineup with proper power rating is

also included in the software design tool.

(2) STEP-2 : Determine DC link capacitor (C

DC

) and the

DC link voltage range.

The maximum DC link voltage ripple is obtained as

where D

ch

is the DC link capacitor charging duty ratio

defined as shown in figure 2, which is typically about 0.2.

It is typical to set V

DC

max

as 10~15% of For

voltage doubler circuit, two capacitors are used in series,

each of which has capacitance twice of the capacitance that

is determined by equation (2).

With the resulting maximum voltage ripple, the minimum

and maximum DC link voltages are given as

Figure 2.DC Link Voltage Waveform

(3) STEP-3 : Determine the transformer reset method and

the maximum duty ratio (D

max

)

One inherent limitation of the forward converter is that the

transformer must be reset during the MOSFET off period.

Thus, additional reset schemes should be employed. Two

most commonly used reset schemes are auxiliary winding

reset and RCD reset. According to the reset schemes, the

design procedure is changed a little bit.

(a) Aux iliary win ding r eset : Figure 3 shows the basic

circuit diagram of forward converter with auxiliary winding

reset. This scheme is advantageous in respect of efficiency

since the energy stored in the magnetizing inductor goes

back to the input. However, the extra reset winding makes

the construction of the transformer more complicated.

Figure 3. Auxiliary Winding Reset Forward Converter

P

i n

P

o

E

f f

------- = (1)

V

DC

max

P

i n

1 D

ch

( )

2V

l i ne

mi n

2f

L

C

DC

------------------------------------------------------------ = (2)

2V

l i ne

mi n

V

DC

mi n

2V

l i ne

mi n

V

DC

max

= (3)

V

DC

max

2V

l i ne

max

= (4)

DC link voltage

DC link voltage ripple

T

1

T

2

D

ch

=T

1

/ T

2

=0.2 - 0.25

Nr

Np

Ns

L

V

DC

Vo

Vgs

ON ON

Vds

V

DC

I

M

V

in

N

p

/N

r

r

p

oss m

DC

N

N

C L

V

/

T

0

T

3

T

2

T

1 T

4

I

M

I

M-

I

M+

T

5

I

r

I

r

+

Vds

-

L

m

Vgs

D

reset

APPLICATION NOTE AN4134

3

2002 Fairchild Semiconductor Corporation

The maximum voltage on MOSFET and the maximum duty

ratio are given by

where N

p

and N

r

are the number of turns for the primary

winding and reset winding, respectively.

As can be seen in equations (5) and (6), the maximum

voltage on the MOSFET can be reduced by decreasing D

max

.

However, decreasing D

max

results in increased voltage stress

on the secondary side. Therefore, it is proper to set

D

max

=0.45 and N

p

=N

r

for universal input. For auxiliary

winding reset, FPS, of which duty ratio is internally limited

below 50%, is recommended to prevent core saturation

during transient.

(b) RCD reset : Figure 4 shows the basic circuit diagram of

the forward converter with RCD reset. One disadvantage of

this scheme is that the energy stored in the magnetizing

inductor is dissipated in the RCD snubber, unlike in the reset

winding method. However, due to its simplicity, this scheme

is widely used for many cost-sensitive SMPS.

Figure 4. RCD Reset Forward Converter

The maximum voltage stress and the nominal snubber capac-

itor voltage are given by

Since the snubber capacitor voltage is fixed and almost

independent of the input voltage, the MOSFET voltage

stress can be reduced compared to the reset winding

approach when the converter is operated with a wide input

voltage range. Another advantage of RCD reset method is

that it is possible to set the maximum duty ratio larger than

50% with relatively low voltage stress on the MOSFET

compared to auxiliary winding reset method, which results

in reduced voltage stress on the secondary side.

(4) STEP-4 : Determine the ripple factor of the output

inductor current.

Figure 5 shows the current of the output inductor. The ripple

factor is defined as

where I

o

is the maximum output current. For most practical

design, it is reasonable to set K

RF

=0.1~ 0.2.

Figure 5. Output Inductor Current and Ripple Factor

Once the ripple factor is determined, the peak current and

rms current of MOSFET are obtained as

Check if the MOSFET maximum peak current (I

ds

peak

) is

below the pulse-by-pulse current limit level of the FPS (I

lim

).

V

ds

max

V

DC

max

1

N

p

N

r

------- +

! "

# $

= (5)

D

max

N

p

N

p

N

r

+

-------------------- (6)

-

V

sn

+

Ns

L

V

DC

Vo

Vgs

ON ON

Vds

V

DC

I

M

V

sn

oss m

sn

C L

V

/

T

0

T

3

T

2

T

1 T

4

I

M

I

M-

I

M+

T

5

I

sn

L

m

Np

R

sn

I

sn

Vgs

+

Vds

-

D

reset

V

ds

max

V

DC

max

= V

sn

+ (7)

V

sn

V

DC

mi n

D

max

1 D

max

( )

---------------------------------------- > (8)

K

RF

I

2I

o

-------- = (9)

I

o

I

o

RF

I

I

K

2

=

T

s

DT

s

I

ds

peak

I

EDC

1 K

RF

+ ( ) = (10)

I

ds

rms

I

EDC

3 K

RF

2

+ ( )

D

max

3

-------------- = (11)

where I

EDC

P

i n

V

DC

mi n

D

max

-------------------------------------- = (12)

AN4134 APPLICATION NOTE

4

2002 Fairchild Semiconductor Corporation

(5) STEP-5 : Determine the proper core and the minimum

primary turns for the transformer to prevent core

saturation.

Actually, the initial selection of the core is bound to be crude

since there are too many variables. One way to select the

proper core is to refer to the manufacture's core selection

guide. If there is no proper reference, use the following

equation as a starting point.

where A

w

is the window area and A

e

is the cross sectional

area of the core in mm

2

as shown in figure 6. f

s

is the

switching frequency and B is the maximum flux density

swing in tesla for normal operation. B is typically 0.2-0.3 T

for most power ferrite cores in the case of a forward

converter. Notice that the maximum flux density swing is

small compared to flyback converter due to the remnant flux

density.

Figure 6. Window Area and Cross Sectional Area

With a determined core, the minimum number of turns for

the transformer primary side to avoid saturation is given by

(6) S TEP-6 : D etermine the number of turns for each

winding of the transformer

First, determine the turns ratio between the primary side and

the feedback controlled secondary side as a reference.

where N

p

and N

s1

are the number of turns for primary side

and reference output, respectively. V

o1

is the output voltage

and V

F1

is the diode forward voltage drop of the reference

output.

Then, determine the proper integer numbers for N

s1

so that

the resulting N

p

is larger than Npmin obtained from equation

(14). The magnetizing inductance of the primary side is

given by

where A

L

is the AL-value with no gap in nH/turns

2

.

The numer of turns for the n-th output is determined as

where V

o(n)

is the output voltage and V

F(n)

is the diode

forward voltage drop of the n-th output.

The next step is to determine the number of turns for Vcc

winding. The number of turns for Vcc winding is determined

differently according to the reset method.

(a) Auxiliary winding reset : For auxiliary winding reset,

the number of turns of the Vcc winding is obtained as

where Vcc* is the nominal voltage for Vcc and V

Fa

is the

diode forward voltage drop. Since Vcc is proportional to the

input voltage when auxiliary winding reset is used, it is

proper to set Vcc* as the Vcc start voltage to avoid the over

voltage protection during the normal operation.

(b) RCD reset : For RCD reset, the number of turns of the

Vcc winding is obtained as

where Vcc* is the nominal voltage for Vcc. Since Vcc is

almost constant for RCD reset in normal operation, it is

proper to set Vcc* to be 2-3 V higher than Vcc start voltage.

(7) ST EP-7 : Determin e the wir e di ameter for each

transformer winding based on the rms current.

The rms current of the n-th winding is obtained as

where I

o(n)

is the maximum current of n-th output.

A

p

A

w

A

e

=

11.1 P

i n

0.141 B f

s

-------------------------------------

1.31

10

4

mm

4

( ) = 13 ( )

Aw Aw Aw Aw

Ae Ae Ae Ae

N

p

mi n

V

DC

mi n

D

max

A

e

f

s

B

-------------------------------------- 10

6

= turns ( ) 14 ( )

n

N

p

N

sI

--------

V

DC

mi n

D

max

V

o1

V

F1

+

-------------------------------------- = = (15)

L

m

A

L

N

p

2

10

9

(H) = (16)

N

s n ( )

V

o n ( )

V

F n ( )

+

V

o1

V

F1

+

---------------------------------- N

s1

(turns) = (17)

N

a

V

cc

* V

Fa

+

V

DC

mi n

---------------------------- N

r

(turns) = (18)

N

a

V

cc

* V

Fa

+

V

sn

---------------------------- N

p

(turns) = (19)

I

n ( ) sec

rms

I

o n ( )

3 K

RF

2

+ ( )

D

max

3

-------------- = (20)

APPLICATION NOTE AN4134

5

2002 Fairchild Semiconductor Corporation

When the auxiliary winding reset is employed, the rms cur-

rent of the reset winding is as follows.

The current density is typically 5A/mm

2

when the wire is

long (>1m). When the wire is short with small number of

turns, current density of 6-10 A/mm

2

is also acceptable.

Avoid using wire with a diameter larger than 1 mm to avoid

severe eddy current losses and to make winding easier. For

high current output, it is better to use parallel winding with

multiple strands of thinner wire to minimize skin effect.

Check if the winding window area of the core is enough to

accommodate the wires. The required window area is given

by

where A

c

is the actual conductor area and K

F

is the fill factor.

Typically the fill factor is 0.2-0.3 when a bobbin is used.

(8) STEP-8 : Determine the proper core and the number

of turns for output inductor

When the forward converter has more than one output as

shown in figure 7, coupled inductors are usually employed to

improve the cross regulation, which are implemented by

winding their separate coils on a single, common core.

Figure 7. Coupled Output Inductors

First, determine the turns ratio of the n-th winding to the

reference winding (the first winding) of the coupled

inductor. The turns ratio should be the same with the

transformer turns ratio of the two outputs as follows.

Then, calculate the inductance of the reference output

inductor as

The minimum number of turns for L

1

to avoid saturation is

given by

where I

lim

is the FPS current limit level, A

e

is the cross

sectional area of the core in mm

2

and B

sat

is the saturation

flux density in tesla. If there is no reference data, use B

sat

=0.35-0.4 T. Once N

L1

is determined, N

L(n)

is determined by

equation (23).

(9) ST EP-9 : Determin e the wir e di ameter for each

inductor winding based on the rms current.

The rms current of the n-th inductor winding is obtained as

The current density is typically 5A/mm

2

when the wire is

long (>1m). When the wire is short with small number of

turns, a current density of 6-10 A/mm

2

is also acceptable.

Avoid using wire with diameter larger than 1 mm to avoid

severe eddy current losses and to make winding easier. For

high current output, it is better to use parallel winding with

multiple strands of thinner wire to minimize skin effect.

(10) STEP-10 : Determine the diode in the secondary side

based on the voltage and current ratings.

The maximum voltage and the rms current of the rectifier

diode of the n-th output are obtained as

(11) STEP-11 : Determine the output capacitor

considering the voltage and current ripple.

The ripple current of the n-th output capacitor is obtained as

I

Reset

rms

V

DC

mi n

D

max

L

m

f

s

----------------------------------------

D

max

3

-------------- = (21)

A

w

A

c

K

F

= (22)

Np

N

S1

D

R1

C

O1

V

O1

L

1

N

S2

D

R2

V

O2

L

2

D

F2

D

F1

C

O2

N

L2

N

L1

N

s n ( )

N

s1

-------------

N

L n ( )

N

L1

------------- = (23)

L

1

V

o1

V

o1

V

F1

+ ( )

2 f

s

K

RF

P

o

----------------------------------------- 1 D

mi n

( ) = (24)

where D

mi n

D

max

V

DC

mi n

V

DC

max

--------------------- = (25)

N

L1

mi n

L

1

P

O

1 K

RF

+ ( )

V

O1

B

sat

A

e

---------------------------------------- 10

6

= turns ( ) 26 ( )

I

L n ( )

rms

I

o n ( )

3 K

RF

2

+ ( )

3

---------------------------- = (27)

V

D n ( )

V

DC

max

N

s n ( )

N

P

------------- = (28)

I

D n ( )

rms

I

o n ( )

3 K

RF

2

+ ( )

D

max

3

-------------- = (29)

AN4134 APPLICATION NOTE

6

2002 Fairchild Semiconductor Corporation

The ripple current should be equal to or smaller than the

ripple current specification of the capacitor.

The voltage ripple on the n-th output is given by

where C

o(n)

is the capacitance and R

c(n)

is the effective series

resistance (ESR) of the n-th output capacitor.

Sometimes it is impossible to meet the ripple specification

with a single output capacitor due to the high ESR of the

electrolytic capacitor. Then, additional LC filter (post filter)

can be used. When using additional LC filter, be careful not

to place the corner frequency too low. If the corner

frequency is too low, it may make the system unstable or

limit the control bandwidth. It is proper to set the corner

frequency of the filter to be around 1/10 to 1/5 of the

switching frequency.

(12) STEP-12 : Design the Reset circuit.

(a) Auxiliary winding reset : For auxiliary winding reset,

the maximum voltage and rms current of the reset diode are

given by

(b) RCD reset : For RCD reset, the maximum voltage and

rms current of the reset diode are given by

The power loss of the snubber network in normal operation

is obtained as

where V

sn

is the snubber capacitor voltage in normal

operation, R

sn

is the snubber resistor, n is N

p

/N

s1

and C

oss

is

the ouput capacitance of the MOSFET. Based on the power

loss, the snubber resistor with proper rated wattage should be

chosen.

The ripple of the snubber capacitor voltage in normal

operation is obtained as

In general, 5-10% ripple is practically reasonable.

Figure 8. Snubber Capacitor Voltage

(13) STEP-13 : Design the feed back loop.

Since FPS employs current mode control as shown in figure

9, the feedback loop can be simply implemented with a one

pole and one zero compensation circuit.

Figure 9. Control Block Diagram

For continuous conduction mode (CCM) operation, the

control-to-output transfer function of forward converter

using FPS is given by

I

C n ( )

rms

K

RF

I

o n ( )

3

---------------------- = (30)

V

o n ( )

I

o n ( )

K

RF

4C

o n ( )

f

s

-------------------------- 2K

RF

I

o n ( )

R

c n ( )

+ = (31)

V

Dreset

V

DC

max

1

N

r

N

p

------- +

! "

# $

= (32)

I

Dreset

rms

V

DC

mi n

D

max

L

m

f

s

----------------------------------

D

max

3

-------------- = 33 ( )

V

DR

V

DC

max

V

sn

+ = (34)

I

DR

rms

V

DC

mi n

D

max

L

m

f

s

----------------------------------

D

max

3

-------------- = (35)

Loss

sn

V

sn

2

R

sn

------------

1

2

---

nV

o1

( )

2

L

m

f

s

---------------------

2nV

o1

V

sn

L

m

C

oss

---------------------------- = = 36 ( )

V

sn

V

sn

D

max

C

sn

R

sn

f

s

------------------------ = (37)

Vds

V

DC

V

sn

T

0

T

3

T

2

T

1 T

4

V

sn

sn

V

v

o1

R

D

i

D

R

bias

R

1

R

2

B

i

bias

C

B

v

FB

1:1

FPS

v

o1

'

C

F

R

F

431

I

pk

MOSFET

current

L

p1

APPLICATION NOTE AN4134

7

2003 Fairchild Semiconductor Corporation

and R

L

is the effective total load resistance of the controlled

output defined as V

o1

2

/P

o

.When the converter has more than

one output, the DC and low frequency control-to-output

transfer function are proportional to the parallel combination

of all load resistance, adjusted by the square of the turns

ratio. Therefore, the effective total load resistance is used in

equation (38) instead of the actual load resistance of V

o1

.

The voltage-to-current conversion ratio of FPS, K is defined

as

where I

pk

is the peak drain current and V

FB

is the feedback

voltage for a given operating condition.

Figure 10 shows the variation of control-to-output transfer

function for a CCM forward converter according to the load.

Since a CCM forward converter has inherent good line

regulation, the transfer function is independent of input

voltage variation. While the system pole together with the

DC gain changes according to the load condition.

The feedback compensation network transfer function of

figure 9 is obtained as

As can be seen in figure 10, the worst case in designing the

feedback loop for a CCM forward converter is the full load

condition. Therefore, by designing the feedback loop with

proper phase and gain margin in low line and full load

condition, the stability all over the operation ranges can be

guaranteed.

The procedure to design the feedback loop is as follows:

(a) Determine the crossover frequency (f

c

). When an

additional LC filter (post filter) is employed, the crossover

frequency should be placed below 1/3 of the corner

frequency of the post filter, since it introduces -180 degrees

phase drop. Never place the crossover frequency beyond the

corner frequency of the post filter. If the crossover frequency

is too close to the corner frequency, the controller should be

designed to have enough phase margin more than about 90

degrees when ignoring the effect of the post filter.

(b) Determine the DC gain of the compensator (w

i

/w

zc

) to

cancel the control-to-output gain at f

c

.

(c) Place compensator zero (f

zc

) around f

c

/3.

(d) Place compensator pole (f

pc

) above 3f

c

.

Figure 10. CCM Forward Converter Control-to-output

Transfer Function variation According to the Load

Figure 11. Compensator Design

When determining the feedback circuit component, there are

some restrictions as follows.

(a) The capacitor connected to feedback pin (C

B

) is related to

the shutdown delay time in an overload situation as

where V

SD

is the shutdown feedback voltage and I

delay

is the

shutdown delay current. These values are given in the data

sheet. In general, 10~100 ms delay time is proper for most

practical applications. In some cases, the bandwidth may be

limited due to the required delay time in over load

protection.

(b) The resistor R

bias

and R

D

used together with opto-coupler

and the KA431 should be designed to provide proper operat-

ing current for the KA431 and to guarantee the full swing of

the feedback voltage of the FPS. In general, the minimum

cathode voltage and current for KA431 is 2.5V and 1mA,

respectively. Therefore, R

bias

and R

D

should be designed to

satisfy the following conditions.

G

vc

o1

FB

--------- K R

L

N

p

N

s1

---------

1 s w

z

+

1 s + w

p

------------------------ = = 38 ( )

where w

z

1

R

c1

C

o1

--------------------, w

p

1

R

L

C

o1

----------------- = =

K

I

pk

V

FB

----------

I

l i m

3

-------- = = (39)

FB

o1

--------- -

w

i

s

-----

1 s + w

zc

1 1 + w

pc

--------------------------- = (40)

where w

i

R

B

R

1

R

D

C

F

s

--------------------------,w

zc

1

R

F

R

1

+ ( )C

F

---------------------------------,w

pc

1

R

B

C

B

--------------- = = =

0 dB

20 dB

-20 dB

-40 dB

40 dB

10Hz 100Hz 10kHz 1kHz 1Hz 100kHz

Heavy load

Light load

f

p

f

p

f

z

0 dB

20 dB

-20 dB

-40 dB

40 dB

10Hz 100Hz 10kHz 1kHz 1Hz 100kHz

Control to output

f

p

f

z

Compensator

Loog gain T

f

zc

f

pc

f

c

w

i

/w

zc

T

del ay

V

SD

3 ( ) = C

B

I

del ay

(41)

AN4134 APPLICATION NOTE

8

2003 Fairchild Semiconductor Corporation

where V

OP

is opto-diode forward voltage drop, which is

typically 1V and I

FB

is the feedback current of FPS, which

is typically 1mA. For example, R

bias

<1k and R

D

<1.5k

for V

o1

=5V.

V

o

V

OP

2.5

R

D

-------------------------------------- I

FB

> (42)

V

OP

R

bi as

-------------- 1mA > (43)

APPLICATION NOTE AN4134

9

2002 Fairchild Semiconductor Corporation

- Summary of symbols -

A

w

: Window area of the core in mm

2

Ae : Cross sectional area of the core in mm

2

B

sat

: Saturation flux density in tesla.

B : Maximum flux density swing in tesla in normal operation

C

o

: Capacitance of the output capacitor.

D

max

: Maximum duty cycle ratio

E

ff

: Estimated efficiency

f

L

: Line frequency

f

s

: Switching frequency

I

ds

peak

: Maximum peak current of MOSFET

I

ds

rms

: RMS current of MOSFET

I

lim

: FPS current limit level.

I

sec(n)

rms

: RMS current of the n-th secondary winding

I

D(n)

rms

: Maximum rms current of the rectifier diode for the n-th output

I

c(n)

rms

: RMS Ripple current of the n-th output capacitor

I

O

: Output load current

K

L(n)

: Load occupying factor for n-th output

K

RF

: Current ripple factor

L

m

: Transformer primary side inductance

Loss

sn

: Power loss of the snubber network in normal operation

N

p

min

: The minimum number of turns for the transformer primary side to avoid saturation

N

p

: Number of turns for primary side

N

r

: Number of turns for reset winding

N

s1

: Number of turns for the reference output

P

o

: Maximum output power

P

in

: Maximum input power

R

c

: Effective series resistance (ESR) of the output capacitor.

R

sn

: Snubber resistor

R

L

: Output load resistor

V

line

min

: Minimum line voltage

V

line

max

: Maximum line voltage

V

DC

min

: Minimum DC link voltage

V

DC

max

: Maximum DC line voltage

V

ds

nom

: Maximum nominal MOSFET voltage

V

o1

: Output voltage of the reference output.

V

F1*

: Diode forward voltage drop of the reference output.

V

cc*

: Nominal voltage for Vcc

V

Fa

: Diode forward voltage drop of Vcc winding

V

DC

max

: Maximum DC link voltage ripple

V

D(n)

: Maximum voltage of the rectifier diode for the n-th output

V

o(n)

: Output voltage ripple of the n-th output

V

sn

: Snubber capacitor voltage in normal operation

V

sn

: Snubber capacitor voltage ripple

V

sn

max

: Maximum snubber capacitor voltage during transient or over load situation

V

ds

max

: Maximum voltage stress of MOSFET

AN4134 APPLICATION NOTE

10

2003 Fairchild Semiconductor Corporation

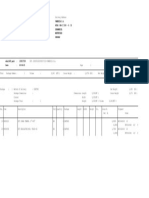

Appendix. Design Example using FPS design Assistant

Target System : PC Power Supply

- Input : universal input (90V-265Vrms) with voltage doubler

- Output : 5V/15A, 3.3V/10A, 12V/6A

By Choi

For forward converter with reset winding

Blue cell is the input parameters

Red cell Red cell Red cell Red cell is the output parameters

1. Define specifications of the SMPS 1. Define specifications of the SMPS 1. Define specifications of the SMPS 1. Define specifications of the SMPS

Minimum Line voltage (V_line.min) 180 V.rms

Maximum Line voltage (V_line.max) 265 V.rms

Line frequency (fL) 60 Hz

Vo Vo Vo Vo Io Io Io Io Po Po Po Po KL KL KL KL

1st output for feedback 5 V 15 A 75 75 75 75 W WW W 42 42 42 42 % %% %

2nd output 3.3 V 10 A 33 33 33 33 W WW W 18 18 18 18 % %% %

3rd output 12 V 6 A 72 72 72 72 W WW W 40 40 40 40 % %% %

4th output 0 V 0 A 0 00 0 W WW W 0 00 0 % %% %

Maximum output power (Po) = Maximum output power (Po) = Maximum output power (Po) = Maximum output power (Po) = 180.0 180.0 180.0 180.0 W WW W

Estimated efficiency (Eff) 70 %

Maximum input power (Pin) = Maximum input power (Pin) = Maximum input power (Pin) = Maximum input power (Pin) = 257.1 257.1 257.1 257.1 W WW W

2. Determine DC link capacitor and the DC voltage range 2. Determine DC link capacitor and the DC voltage range 2. Determine DC link capacitor and the DC voltage range 2. Determine DC link capacitor and the DC voltage range

DC link capacitor 235 uF

DC link voltage ripple = DC link voltage ripple = DC link voltage ripple = DC link voltage ripple = 29 29 29 29 V VV V

Minimum DC link voltage = Minimum DC link voltage = Minimum DC link voltage = Minimum DC link voltage = 226 226 226 226 V VV V

Maximum DC link voltage = Maximum DC link voltage = Maximum DC link voltage = Maximum DC link voltage = 375 375 375 375 V VV V

3. Determine the maximum duty ratio (Dmax) 3. Determine the maximum duty ratio (Dmax) 3. Determine the maximum duty ratio (Dmax) 3. Determine the maximum duty ratio (Dmax)

Maximum duty ratio 0.4

Turns ratio (Np/Nr) 1 >

Maximum nominal MOSFET voltage = Maximum nominal MOSFET voltage = Maximum nominal MOSFET voltage = Maximum nominal MOSFET voltage = 750 750 750 750 V VV V

4. Determine the ripple factor of the output inductor current 4. Determine the ripple factor of the output inductor current 4. Determine the ripple factor of the output inductor current 4. Determine the ripple factor of the output inductor current

Output Inductor current ripple factor 0.15

Maximum peak drain current = Maximum peak drain current = Maximum peak drain current = Maximum peak drain current = 3.27 3.27 3.27 3.27 A AA A

RMS drain current = RMS drain current = RMS drain current = RMS drain current = 1.81 1.81 1.81 1.81 A AA A

Current limit of FPS 4 A

5. Determine proper core and minimum primary turns for transformer 5. Determine proper core and minimum primary turns for transformer 5. Determine proper core and minimum primary turns for transformer 5. Determine proper core and minimum primary turns for transformer

Switching frequency of FPS (kHz) 67 kHz

Maximum flux density swing 0.32 T --> --> --> -->EER2834 EER2834 EER2834 EER2834

Estimated AP value of core = Estimated AP value of core = Estimated AP value of core = Estimated AP value of core = 9275 9275 9275 9275 mm mm mm mm

4 44 4

AP=12470 AP=12470 AP=12470 AP=12470

Cross sectional area of core (Ae) 86 mm

2

Ae=86 Ae=86 Ae=86 Ae=86

Minimum primary turns = Minimum primary turns = Minimum primary turns = Minimum primary turns = 49.0 49.0 49.0 49.0 T TT T Aw=145 Aw=145 Aw=145 Aw=145

FPS Design Assistant ver.1.0

0.67 0.67 0.67 0.67

I

o

I

o

RF

I

I

K

2

=

T

s

DT

s

APPLICATION NOTE AN4134

11

2002 Fairchild Semiconductor Corporation

6. Determine the numner of turns for each outputs 6. Determine the numner of turns for each outputs 6. Determine the numner of turns for each outputs 6. Determine the numner of turns for each outputs

Vo Vo Vo Vo VF VF VF VF # of turns # of turns # of turns # of turns

Vcc (Use Vcc start voltage) Vcc (Use Vcc start voltage) Vcc (Use Vcc start voltage) Vcc (Use Vcc start voltage) 15 V 1.2 V 3.6 3.6 3.6 3.6 => 4 44 4 T TT T

1st output for feedback 1st output for feedback 1st output for feedback 1st output for feedback 5 V 0.4 V 3 => 3 33 3 T TT T

2nd output 2nd output 2nd output 2nd output 3.3 V 0.4 V 2.06 2.06 2.06 2.06 => 2 22 2 T TT T

3rd output 3rd output 3rd output 3rd output 12 V 0.5 V 6.94 6.94 6.94 6.94 => 7 77 7 T TT T

4th output 4th output 4th output 4th output 0 V 0 V 0 00 0 => 0 00 0 T TT T

VF : Forward voltage drop of rectifier diode Reset winding = Reset winding = Reset winding = Reset winding = 50 50 50 50 T TT T

Primary turns = Primary turns = Primary turns = Primary turns = 50 50 50 50 T TT T

->enough turns ->enough turns ->enough turns ->enough turns

AL value (no gap) 2490 nH/T

2

Transformer magnetizing inductance = Transformer magnetizing inductance = Transformer magnetizing inductance = Transformer magnetizing inductance = 6.27499 6.27499 6.27499 6.27499 mH mH mH mH -->EER2834 EER2834 EER2834 EER2834

7. Determine the wire diameter for each transformer winding 7. Determine the wire diameter for each transformer winding 7. Determine the wire diameter for each transformer winding 7. Determine the wire diameter for each transformer winding

Diameter Diameter Diameter Diameter Parallel Parallel Parallel Parallel Irms Irms Irms Irms (A/mm (A/mm (A/mm (A/mm

2 22 2

) )) )

Primary winding (Np) Primary winding (Np) Primary winding (Np) Primary winding (Np) 0.68 mm 1 T 1.81 1.81 1.81 1.81 A AA A

Reset winding (Nr) Reset winding (Nr) Reset winding (Nr) Reset winding (Nr) 0.31 mm 1 T 0.08 0.08 0.08 0.08 A AA A

Vcc winding Vcc winding Vcc winding Vcc winding 0.31 mm 1 T 0.10 0.10 0.10 0.10 A AA A

1st output winding 1st output winding 1st output winding 1st output winding 0.68 mm 4 T 9.5 9.5 9.5 9.5 A AA A

2nd output winding 2nd output winding 2nd output winding 2nd output winding 0.68 mm 3 T 6.3 6.3 6.3 6.3 A AA A

3rd output winding 3rd output winding 3rd output winding 3rd output winding 0.68 mm 2 T 3.8 3.8 3.8 3.8 A AA A

4th output winding 4th output winding 4th output winding 4th output winding 0 mm 0 T 0.0 0.0 0.0 0.0 A AA A

Copper area = Copper area = Copper area = Copper area = 33.9262 33.9262 33.9262 33.9262 mm mm mm mm

2 22 2

Fill factor 0.25

Required window area Required window area Required window area Required window area 135.705 135.705 135.705 135.705 mm mm mm mm

2 22 2

--> EER2834 EER2834 EER2834 EER2834 (Aw=145) (Aw=145) (Aw=145) (Aw=145)

8. Determine proper core and number of turns for inductor (coupled inductor) 8. Determine proper core and number of turns for inductor (coupled inductor) 8. Determine proper core and number of turns for inductor (coupled inductor) 8. Determine proper core and number of turns for inductor (coupled inductor)

Cross sectional area of Inductor core (A 86 mm

2

--> EER2834 EER2834 EER2834 EER2834

Saturation flux density 0.42 T

Inductance of 1st output (L1) = Inductance of 1st output (L1) = Inductance of 1st output (L1) = Inductance of 1st output (L1) = 5.7 5.7 5.7 5.7 uH uH uH uH

Minimum turns of L1 = Minimum turns of L1 = Minimum turns of L1 = Minimum turns of L1 = 6.5 6.5 6.5 6.5 T TT T

Actual number of turns for L1 6 => 6 66 6 T TT T

Number of turns for L2 = Number of turns for L2 = Number of turns for L2 = Number of turns for L2 = 4 44 4 => 4 44 4 T TT T

Number of turns for L3 = Number of turns for L3 = Number of turns for L3 = Number of turns for L3 = 14 14 14 14 => 14 14 14 14 T TT T

Number of turns for L4 = Number of turns for L4 = Number of turns for L4 = Number of turns for L4 = 0 00 0 => 0 00 0 T TT T

9. Determine the wire diameter for each inductor winding 9. Determine the wire diameter for each inductor winding 9. Determine the wire diameter for each inductor winding 9. Determine the wire diameter for each inductor winding

Diameter Diameter Diameter Diameter Parallel Parallel Parallel Parallel Irms Irms Irms Irms (A/mm (A/mm (A/mm (A/mm

2 22 2

) )) )

Winding for L1 Winding for L1 Winding for L1 Winding for L1 0.68 mm 5 T 15.1 15.1 15.1 15.1 A AA A

Winding for L2 Winding for L2 Winding for L2 Winding for L2 0.68 mm 3 T 10.0 10.0 10.0 10.0 A AA A

Winding for L3 Winding for L3 Winding for L3 Winding for L3 0.68 mm 2 T 6.0 6.0 6.0 6.0 A AA A

Winding for L4 Winding for L4 Winding for L4 Winding for L4 0 mm 0 T 0.0 0.0 0.0 0.0 A AA A

Copper area = Copper area = Copper area = Copper area = 25.4089 25.4089 25.4089 25.4089 mm mm mm mm

2 22 2

Fill factor 0.25

Required window area Required window area Required window area Required window area 101.636 101.636 101.636 101.636 mm mm mm mm

2 22 2

--> EER2834(Aw=145) EER2834(Aw=145) EER2834(Aw=145) EER2834(Aw=145)

10. Determine the rectifier diodes in the secondary side 10. Determine the rectifier diodes in the secondary side 10. Determine the rectifier diodes in the secondary side 10. Determine the rectifier diodes in the secondary side

Reverse voltage Reverse voltage Reverse voltage Reverse voltage Rms Current Rms Current Rms Current Rms Current

Vcc diode Vcc diode Vcc diode Vcc diode 55 55 55 55 V VV V 0.10 0.10 0.10 0.10 A AA A -->UF4003 -->UF4003 -->UF4003 -->UF4003

1st output diode 1st output diode 1st output diode 1st output diode 22 22 22 22 V VV V 9.5 9.5 9.5 9.5 A AA A -->MBR3060PT -->MBR3060PT -->MBR3060PT -->MBR3060PT

2nd output diode 2nd output diode 2nd output diode 2nd output diode 15 15 15 15 V VV V 6.3 6.3 6.3 6.3 A AA A -->MBR3045PT -->MBR3045PT -->MBR3045PT -->MBR3045PT

3rd output diode 3rd output diode 3rd output diode 3rd output diode 52 52 52 52 V VV V 3.81 3.81 3.81 3.81 A AA A -->MBR20H100CT -->MBR20H100CT -->MBR20H100CT -->MBR20H100CT

4th output diode 4th output diode 4th output diode 4th output diode 0 00 0 V VV V 0.00 0.00 0.00 0.00 A AA A

8.30 8.30 8.30 8.30

#DIV/0! #DIV/0! #DIV/0! #DIV/0!

9.22 9.22 9.22 9.22

8.30 8.30 8.30 8.30

5.83 5.83 5.83 5.83

5.25 5.25 5.25 5.25

#DIV/0! #DIV/0! #DIV/0! #DIV/0!

4.98 4.98 4.98 4.98

1.04 1.04 1.04 1.04

1.33 1.33 1.33 1.33

6.56 6.56 6.56 6.56

AN4134 APPLICATION NOTE

12

2003 Fairchild Semiconductor Corporation

11. Determine the output capacitor 11. Determine the output capacitor 11. Determine the output capacitor 11. Determine the output capacitor

ESR ESR ESR ESR Current Current Current Current Voltage Voltage Voltage Voltage

ripple ripple ripple ripple Ripple Ripple Ripple Ripple

1st output capacitor 1st output capacitor 1st output capacitor 1st output capacitor 4400 uF 20 m! 1.3 1.3 1.3 1.3 V VV V 0.09 0.09 0.09 0.09 V VV V

2nd output capacitor 2nd output capacitor 2nd output capacitor 2nd output capacitor 4400 uF 20 m! 0.9 0.9 0.9 0.9 V VV V 0.06 0.06 0.06 0.06 V VV V

3rd output capacitor 3rd output capacitor 3rd output capacitor 3rd output capacitor 2000 uF 60 m! 0.5 0.5 0.5 0.5 V VV V 0.11 0.11 0.11 0.11 V VV V

4th output capacitor 4th output capacitor 4th output capacitor 4th output capacitor 0 uF 0 m! 0.0 0.0 0.0 0.0 V VV V #### #### #### #### V VV V

12. Design the Reset Circuit 12. Design the Reset Circuit 12. Design the Reset Circuit 12. Design the Reset Circuit

Reset diode rms current Reset diode rms current Reset diode rms current Reset diode rms current 0.08 0.08 0.08 0.08 A AA A

Maximum voltage of reset diode Maximum voltage of reset diode Maximum voltage of reset diode Maximum voltage of reset diode 750 750 750 750 V VV V -->UF4007 -->UF4007 -->UF4007 -->UF4007

13. Design Feedback control loop 13. Design Feedback control loop 13. Design Feedback control loop 13. Design Feedback control loop

Contr ol-to-output DC gain = Contr ol-to-output DC gain = Contr ol-to-output DC gain = Contr ol-to-output DC gain = 3 33 3

Contr ol-to-output zero = Contr ol-to-output zero = Contr ol-to-output zero = Contr ol-to-output zero = 1,809 1,809 1,809 1,809 Hz Hz Hz Hz

Contr ol-to-output pole = Contr ol-to-output pole = Contr ol-to-output pole = Contr ol-to-output pole = 261 261 261 261 Hz Hz Hz Hz

Voltage divider resistor (R1) 5 "

Voltage divider resistor (R2) 5 "

Opto coupler diode resistor (RD) 1 "

431 Bias resistor (Rbias) 1.2 "

Feeback pin capacitor (CB) = 10 nF

Feedback Capacitor (CF) = 100 nF

Feedback resistor (RF) = 1 "

Feedback integrator gain (fi) = Feedback integrator gain (fi) = Feedback integrator gain (fi) = Feedback integrator gain (fi) = 955 955 955 955 Hz Hz Hz Hz

Feedback zero (fz) = Feedback zero (fz) = Feedback zero (fz) = Feedback zero (fz) = 265.393 265.393 265.393 265.393 Hz Hz Hz Hz

Feedback pole (fp) = Feedback pole (fp) = Feedback pole (fp) = Feedback pole (fp) = 5307.86 5307.86 5307.86 5307.86 Hz Hz Hz Hz

16 9.80783 36 45 16 # -86.7 #

25 9.78487 32 41 25 # -84.9 #

40 9.7248 28 37 40 # -81.9 #

63 9.58236 24 33 63 # -77.3 #

100 9.24037 20 29 100 # -70.4 #

160 8.46816 17 25 160 # -60.6 #

250 7.07174 14 21 250 # -49.4 #

400 4.77208 13 17 400 # -37.8 #

630 1.96652 12 14 630 # -29.6 #

1000 -0.9856 11 10 1000 # -25.5 #

1600 -3.5451 11 7.3 1600 # -26.2 #

2500 -5.2263 10 5.1 2500 # -31.3 #

4000 -6.2187 9.2 3 4000 # -40.8 #

6300 -6.6721 7.3 0.6 6300 # -52.3 #

10000 -6.8719 4.5 -2 #### # -63.5 #

16000 -6.9549 1.1 -6 #### # -72.6 #

25000 -6.9867 -3 -10 #### # -78.6 #

40000 -7.0002 -6 -13 #### # -82.8 #

63000 -7.0054 -10 -17 #### # -85.4 #

100000 -7.0075 -14 -21 #### # -87.1 #

Capacitance Capacitance Capacitance Capacitance

v

o

R

D

i

D

R

bias

R

1

R

2

B

i

bias

C

B

v

FB

1: 1

FPS v

o

'

C

F

R

F

431

-40

-20

0

20

40

60

10 100 1000 10000 100000

G

a

i

n

(

d

B

)

Contorl-to-output

Compensator

T

-120

-90

-60

-30

0

10 100 1000 10000 100000

P

h

a

s

e

(

d

e

g

r

e

e

)

APPLICATION NOTE AN4134

13

2003 Fairchild Semiconductor Corporation

Design Summary

For the FPS, FS7M0880 is chosen. This device has a fixed switching frequency of 67kHz.

To limit the current, a 10 ohm resistor (Ra) is used in series with the Vcc diode.

The control bandwidth is 6kHz. Since the crossover frequency is too close the corner frequency of the post filter (additional

LC filter), the controller is designed to have enough phase margin of 120 degrees when ignoring the effect of the post filter.

Figure 12 shows the final schematic of the forward converter designed by FPS Design Assistant

Figure 12. The final schematic of the forward converter

KA1M0280RB,KA1M0380RB,KA1L0380RB,KA1H0680B,KA1M0680B,KA1H0680RFB,KA1M0680RB,KA1M0880B,KA1M0

880BF,KA1M0880D,KA5H0280R,KA5M0280R,KA5H0380R,KA5M0380R,KA5L0380R,KA5P0680C,FS7M0680,FS7M0880

Np

N

S1

+

V

DC

-

AC li ne

D

R1

C

O1

Drai n

Vcc

GND FB

FS7M0880

NTC Fuse

R

L1

C

L1

Line Filter

C

L2

N

a

D

a

R

a

C

a

KA431

817A

10

R

bias

R

1

R

2

R

F C

F

GBU606

V

O1

L

1

C

B

2C

DC N

S2

D

R2

V

O2

L

2

D

F2

D

F1

C

O2

2C

DC

Non-doubled

Doubled

D

Reset

5k

5k

5V

3.3V

N

S2

V

O3

D

F3

C

O3

Nr

D

R3

L

3

12V

1.2k

1k

2200uF # ## #2

2200uF# ## #2

1000uF # ## #2

MBR3060PT

MBR3045PT

MBR120H100CT

R

start

S/S

Css

1uF

UF4007

UF4003

22uF

560k

10nF

470uF

470uF

1k 100nF

1M

100nF

100nF

L

p1

C

p1

470uF

L

p2

C

p2

1000uF

1.2uH

1.2uH

R

d

AN4134 APPLICATION NOTE

3/24/04 0.0m 002

2003 Fairchild Semiconductor Corporation

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY

PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY

LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER

DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES

OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR

CORPROATION. As used herein:

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the body,

or (b) support or sustain life, or (c) whose failure to perform

when properly used in accordance with instructions for use

provided in the labeling, can be reasonably expected to

result in significant injury to the user.

2. A critical component is any component of a life support

device or system whose failure to perform can be

reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

by Hang-Seok Choi / Ph. D

FPS Application Group / Fairchild Semiconductor

Phone : +82-32-680-1383 Facsimile : +82-32-680-1317

E-mail : hschoi@fairchildsemi.co.kr

You might also like

- HW1Document4 pagesHW1Caio CezarNo ratings yet

- Fluidization of Bulk SolidsDocument77 pagesFluidization of Bulk SolidsManfredHeyde100% (1)

- Designing Loop AntennasDocument18 pagesDesigning Loop AntennasCesar AvilaNo ratings yet

- Step Recovery Diode Frequency MultiplierDocument4 pagesStep Recovery Diode Frequency MultiplierfahkingmoronNo ratings yet

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- Fly BackDocument20 pagesFly BackĐặng Văn TàiNo ratings yet

- Design Battery ChargerDocument20 pagesDesign Battery Chargeranand_girgaonkar100% (1)

- An 4137Document20 pagesAn 4137Andres RinconNo ratings yet

- Funcionamiento Del 5Q1265RF en La FuenteDocument19 pagesFuncionamiento Del 5Q1265RF en La FuenteJorge Corrales100% (1)

- An 4140Document11 pagesAn 4140ommidbeNo ratings yet

- Bien AP XungDocument11 pagesBien AP XungVan Thanh TranNo ratings yet

- An 4140Document11 pagesAn 4140Anonymous j7toV6z7PNo ratings yet

- Application Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Document16 pagesApplication Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Nagendra ChaitanyaNo ratings yet

- Universal Block DiagramDocument6 pagesUniversal Block Diagramapneetsandhu1234No ratings yet

- Step-ByStep Flyback SMPS DesignDocument6 pagesStep-ByStep Flyback SMPS DesignPhạm Văn TưởngNo ratings yet

- An-9014-Fairchild QFET For Synchronous Rectification DC To DC Converters - ImpDocument16 pagesAn-9014-Fairchild QFET For Synchronous Rectification DC To DC Converters - ImpbmmostefaNo ratings yet

- Designing DC-DC Converters Based On ZETA TopologyDocument8 pagesDesigning DC-DC Converters Based On ZETA TopologyMayeth MacedaNo ratings yet

- Compensation Method Peak Current Mode Control Buck AN028 enDocument13 pagesCompensation Method Peak Current Mode Control Buck AN028 ensadqazwsxNo ratings yet

- Design Guideline For Flyback Charger Using FAN302HL/ULDocument20 pagesDesign Guideline For Flyback Charger Using FAN302HL/ULteomondoNo ratings yet

- Implementing The TL431 Feedback LoopDocument10 pagesImplementing The TL431 Feedback LoopAnand KumarNo ratings yet

- Lm5032 Interleaved Boost Converter: D1 L1 Vin VoutDocument12 pagesLm5032 Interleaved Boost Converter: D1 L1 Vin VoutParvesh GautamNo ratings yet

- Design Guideline of AC-DC Converter Using FL6961 & FL6300A For 70W LED LightingDocument13 pagesDesign Guideline of AC-DC Converter Using FL6961 & FL6300A For 70W LED Lightingshiva1luNo ratings yet

- Inrush 2016 R2Document9 pagesInrush 2016 R2AuslanderNo ratings yet

- Forward Design 300W STmicroelectronics App NoteDocument10 pagesForward Design 300W STmicroelectronics App Notecristi7521No ratings yet

- An 1162Document36 pagesAn 1162naniknanikNo ratings yet

- 3.4.2 Output Capacitor: Out C, Max OutDocument14 pages3.4.2 Output Capacitor: Out C, Max OutReza RzNo ratings yet

- UCC28070Document27 pagesUCC28070gubiliNo ratings yet

- Chang 09 Med PrimDocument6 pagesChang 09 Med PrimSuselleNo ratings yet

- RESEARCH of Communications Research No. 2Document19 pagesRESEARCH of Communications Research No. 2Princess EsmejardaNo ratings yet

- Äñ Æ÷Éè Æ Ó ©Document6 pagesÄñ Æ÷Éè Æ Ó ©Rachel RowlandNo ratings yet

- High Frequency Power Transformers - Design A High-Frequency Power Transformer Based On Flyback TopologyDocument6 pagesHigh Frequency Power Transformers - Design A High-Frequency Power Transformer Based On Flyback TopologyShyam Bin Jamil100% (1)

- 130nm CMOS Technology Design of Passive UHF RFID Tag inDocument4 pages130nm CMOS Technology Design of Passive UHF RFID Tag inDuc DucNo ratings yet

- And8328 DDocument8 pagesAnd8328 DJonatan LunaNo ratings yet

- Basic Calculation of A Boost Converter's Power StageDocument9 pagesBasic Calculation of A Boost Converter's Power Stagexuanvan1303No ratings yet

- Anp013 1509Document9 pagesAnp013 1509camorra1923No ratings yet

- AND8182Document6 pagesAND8182carlos_eqnNo ratings yet

- EECS267B Proj3Document19 pagesEECS267B Proj3hellwellNo ratings yet

- Uc3842 Provides Low-Cost Current-Mode Control: Application NoteDocument16 pagesUc3842 Provides Low-Cost Current-Mode Control: Application NoteLeonardo Ortiz100% (1)

- 90204diDocument8 pages90204diadialaktosNo ratings yet

- Simple FSKDocument6 pagesSimple FSKFaten AliNo ratings yet

- How To Use Analog Dimming With The TPS6116x: Application ReportDocument6 pagesHow To Use Analog Dimming With The TPS6116x: Application ReportlaltukarmakarNo ratings yet

- Very Wide Input Voltage Range-Flyback (90V To 600V AC)Document12 pagesVery Wide Input Voltage Range-Flyback (90V To 600V AC)senkum812002No ratings yet

- 5W USB Flyback Design ReviewApplication ReportDocument21 pages5W USB Flyback Design ReviewApplication ReportleechulmiuNo ratings yet

- Viper22a Equivalent PDFDocument16 pagesViper22a Equivalent PDFXande Nane Silveira0% (1)

- AND8241/D A 5.0 V/2.0 A Standby Power Supply For INTEL Compliant ATX ApplicationsDocument16 pagesAND8241/D A 5.0 V/2.0 A Standby Power Supply For INTEL Compliant ATX ApplicationsJonatan LunaNo ratings yet

- An 1024Document19 pagesAn 1024vipulugale100% (1)

- Small-Signal Analysis of Open-Loop PWM Flyback DCDC Converter For CCMDocument8 pagesSmall-Signal Analysis of Open-Loop PWM Flyback DCDC Converter For CCMAslı ÇakırNo ratings yet

- CMOS Low-Power Analog Circuit Design: Christian C. Enz and Eric A. VittozDocument55 pagesCMOS Low-Power Analog Circuit Design: Christian C. Enz and Eric A. VittozRavinder KumarNo ratings yet

- Application Note ANP 16: Loop Compensation of Voltage-Mode Buck ConvertersDocument9 pagesApplication Note ANP 16: Loop Compensation of Voltage-Mode Buck ConvertersNguyen Thanh TuanNo ratings yet

- Design Note: Optimizing Performance in Uc3854 Power Factor Correction ApplicationsDocument42 pagesDesign Note: Optimizing Performance in Uc3854 Power Factor Correction ApplicationsidsufixNo ratings yet

- RC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentDocument8 pagesRC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentMani BharathiNo ratings yet

- Amplitude Modulation of The AD9850Document2 pagesAmplitude Modulation of The AD9850maruja4No ratings yet

- PWM To DC Voltage Conversion: Kyle Burgess 4/3/2015Document8 pagesPWM To DC Voltage Conversion: Kyle Burgess 4/3/2015NaranLoganNo ratings yet

- An Efficiency Primer For Switch-Mode, DC-DC Converter Power SuppliesDocument11 pagesAn Efficiency Primer For Switch-Mode, DC-DC Converter Power SuppliesJonathan JaegerNo ratings yet

- Cntfet Technology Based Precision Full-Wave Rectifier Using DDCCDocument8 pagesCntfet Technology Based Precision Full-Wave Rectifier Using DDCCresearchinventyNo ratings yet

- Snubber Circuit Design CalculatorsDocument3 pagesSnubber Circuit Design CalculatorsteomondoNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Power System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)From EverandPower System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)No ratings yet

- DN 315 FDocument2 pagesDN 315 Fshri.bhairavkar6977No ratings yet

- AN-4102: Colour TV Receiver SMPSDocument16 pagesAN-4102: Colour TV Receiver SMPSshri.bhairavkar6977No ratings yet

- 24v To 5v DC Power Supply With Uc3842Document19 pages24v To 5v DC Power Supply With Uc3842shri.bhairavkar6977100% (1)

- 24v To 5v DC Power Supply With Uc3842Document19 pages24v To 5v DC Power Supply With Uc3842shri.bhairavkar6977100% (1)

- EtherCAT ET1200 Datasheet All V1i7Document271 pagesEtherCAT ET1200 Datasheet All V1i7shri.bhairavkar6977No ratings yet

- Formet For ManuscriptDocument2 pagesFormet For Manuscriptshri.bhairavkar6977No ratings yet

- AN ESC FAQ V1i1Document52 pagesAN ESC FAQ V1i1shri.bhairavkar6977No ratings yet

- Mccsemi: 1N5221 Thru 1N5281Document3 pagesMccsemi: 1N5221 Thru 1N5281shri.bhairavkar6977No ratings yet

- EMI IC Application Aug 2Document25 pagesEMI IC Application Aug 2shri.bhairavkar6977No ratings yet

- Thyristor PDFDocument10 pagesThyristor PDFMihir HembramNo ratings yet

- Physics 1 Week 9Document16 pagesPhysics 1 Week 9Santos, Alexsandria PaulaNo ratings yet

- 1 in 60 RuleDocument3 pages1 in 60 Rulegovin74No ratings yet

- Chapter 7 - Assignment 1Document6 pagesChapter 7 - Assignment 1HarshilNo ratings yet

- Charles Law Example Experiment - 1Document5 pagesCharles Law Example Experiment - 1nettexts75% (4)

- Pressure: Unit 2Document14 pagesPressure: Unit 2Sumit ShahNo ratings yet

- Green HVAC As Part of Smart HospitalDocument51 pagesGreen HVAC As Part of Smart HospitalFitri susilowatiNo ratings yet

- 220kv Budhil Line Rev-1Document5 pages220kv Budhil Line Rev-1t_syamprasadNo ratings yet

- Electrical Power Systems DDocument2 pagesElectrical Power Systems DdhrghamNo ratings yet

- Second Periodical Examination Science Grade 10Document6 pagesSecond Periodical Examination Science Grade 10Walter Orpilla100% (1)

- Protective Device Coordination ETAP Star PDFDocument89 pagesProtective Device Coordination ETAP Star PDFTadala Maluwa50% (2)

- Datasheet Septa 31 RuagDocument7 pagesDatasheet Septa 31 RuagPatosanNo ratings yet

- Moving Charges and Magnetism Grade 12 - PPT PresentationDocument12 pagesMoving Charges and Magnetism Grade 12 - PPT Presentationfdkfja dafklaNo ratings yet

- Ac Cassette 1Document1 pageAc Cassette 1Surya LiemNo ratings yet

- Theory and Design of Mechanical Systems ProjectDocument27 pagesTheory and Design of Mechanical Systems ProjectSneha Girish ShirsatNo ratings yet

- Packing List Vamerica PDFDocument1 pagePacking List Vamerica PDFEduardo ContrerasNo ratings yet

- E85001-1026 - Wall Mount Speakers and Speaker-StrobesDocument6 pagesE85001-1026 - Wall Mount Speakers and Speaker-StrobesJun AntonioNo ratings yet

- Mtbe 3 - DP 2Document303 pagesMtbe 3 - DP 2Faiz ZainiNo ratings yet

- 2901-Physics Paper With Solution EveningDocument10 pages2901-Physics Paper With Solution Eveningravigupta1984No ratings yet

- Natural Gas Transmission Pipeline Temperature Drop CalculationDocument5 pagesNatural Gas Transmission Pipeline Temperature Drop CalculationCarina QuibinitNo ratings yet

- Lesson 5 Angles and Angular MeasureDocument32 pagesLesson 5 Angles and Angular MeasureParadox Hans AgravanteNo ratings yet

- Problem Set 2Document2 pagesProblem Set 2Julcris JimenezNo ratings yet

- Inflon Ptfe Gasket Sheet: Inmarco Type 600Document1 pageInflon Ptfe Gasket Sheet: Inmarco Type 600ArunNo ratings yet

- Instruction Bulletin Square D Services: Procedures For Startup and Commissioning of Electrical Equipment Class 0180Document66 pagesInstruction Bulletin Square D Services: Procedures For Startup and Commissioning of Electrical Equipment Class 0180aceel_fitchNo ratings yet

- Storage Battery Maintenance Manual (Eng Version)Document99 pagesStorage Battery Maintenance Manual (Eng Version)harry.nuryantoNo ratings yet

- 15.flow Switch For Piston Cooling OilDocument10 pages15.flow Switch For Piston Cooling OilKaleb Z king webNo ratings yet

- An Accurate Method To Determine Electric Motor Efficiency While The Motor Is in OperationDocument28 pagesAn Accurate Method To Determine Electric Motor Efficiency While The Motor Is in OperationShri KulkarniNo ratings yet

- Simple Harmonic Motion 1Document11 pagesSimple Harmonic Motion 1Golam RabbaniNo ratings yet

- Electromagnetic - Theory - NET-JRF June 2011-Dec 2014Document24 pagesElectromagnetic - Theory - NET-JRF June 2011-Dec 2014Prasad RavichandranNo ratings yet