Professional Documents

Culture Documents

Experiment 6: Aim: Eda Tool Used: Methodology

Uploaded by

Thomas JamesOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Experiment 6: Aim: Eda Tool Used: Methodology

Uploaded by

Thomas JamesCopyright:

Available Formats

FPGA/ CPLD LAB

EXPERIMENT 6

AIM : To design a 16:1 multiplexer using a 4:1 multiplexer at the dataflow and behavioural levels.

EDA TOOL USED : Xilinx ISE 8.1i

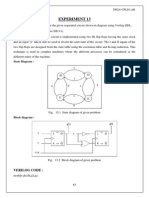

METHODOLOGY : 16:1 Mux is a combinational circuit having 16 input lines from I0 - I15

and 4 select lines from S0 S3. On the basis of select lines it is decided which input will be

transmitted to output. Large multiplexers can be implemented by using smaller size multiplexers. On

the basis of this theory, 16:1 mux can be designed by using five 4:1 muxes as shown in figure.

Logic Symbol :

Fig. 6.1 Logic symbol of 16 : 1 MUX

Truth Table:

Select lines

S3

S2

S1

S0

0

0

0

0

0

0

0

1

0

0

1

0

Block

Diagram

:

0

0

1

1

0

1

0

0

Fig.

6.2

Block

0

1

0

1

0VERILOG

1

1

0

0

1

1

1

Dataflow

level

module

input

Output

Output

(Y)

I0

I1

I2

I3

I4

I5

I6

I7

(Y)

diagram of 16 : 1 MUX

CODE :

Modelling

Selec

muxd2(I0, I1, I2, I3, S0, S1, Y);

I0,I1,I2,I3,S0,S1; output Y; assign

lines

S3

S2

S1

S0

endmodule

I8

module

I9

muxg(I, S, Y);

input [15:0]

I10

I;

I11

I12

I13

030

I14

I15

{Y}=S0?(S1?

y1,y2,y3,y4;

muxd2

I3:I1):(S1?I2:I0);

input [3:0] S;

output Y;

wire

m1(I[0],I[1],I[2],I[3],S[0],S[1],y1);

FPGA/ CPLD LAB

muxd2 m2(I[4],I[5],I[6],I[7],S[0],S[1],y2);

muxd2 m3(I[8],I[9],I[10],I[11],S[0],S[1],y3);

muxd2 m4(I[12],I[13],I[14],I[15],S[0],S[1],y4);

muxd2 m5(y1,y2,y3,y4,S[2],S[3],Y);

endmodule

Behavioural level Modelling

module muxb(I,S,Y);

input [3:0]I; input [1:0]S; output reg Y;

always@(I,S)

begin

case(S)

0: begin Y=I[0]; end

1: begin Y=I[1]; end

2: begin Y=I[2]; end

3: begin Y=I[3]; end

endcase

end

endmodule

module mux(I, S, Y, F);

input [15:0] I; input [3:0] S; wire [3:0]Y; output F;

muxb(I[3:0],S[1:0],Y[0]); muxb(I[7:4],S[1:0],Y[1]); muxb(I[11:8],S[1:0],Y[2]);

muxb(I[15:12],S[1:0],Y[3]); muxb(Y[3:0],S[3:2],F);

endmodule

RTL SCHEMATIC VIEW :

Dataflow level Modelling

Fig 6.3

RTL schematic of 16 : 1 MUX

Behavioural level Modelling

31

FPGA/ CPLD LAB

Fig 6.4

RTL schematic of 16 : 1 MUX

OUTPUT WAVEFORM :

32

FPGA/ CPLD LAB

Fig 6.5

Output waveform of 16 : 1 MUX

RESULT : Successfully implemented 16 : 1 multiplexer using 4 : 1 multiplexer modules and

verified its operation through simulation.

33

You might also like

- Experiment 5: Aim: Eda Tool Used: MethodologyDocument4 pagesExperiment 5: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- Experiment 5: Aim: Eda Tool Used: MethodologyDocument4 pagesExperiment 5: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- Multiplexer Circuit and How It WorksDocument9 pagesMultiplexer Circuit and How It WorksEpnixNo ratings yet

- Data Processing CircuitsDocument19 pagesData Processing CircuitsBhaskar MNo ratings yet

- EEE 304 Experiment No. 04 Name of The Experiment: Design of Decoder/Encoder/Multiplexer CircuitDocument5 pagesEEE 304 Experiment No. 04 Name of The Experiment: Design of Decoder/Encoder/Multiplexer CircuitAurongo NasirNo ratings yet

- EEE 304 - Exp4 PDFDocument5 pagesEEE 304 - Exp4 PDFAurongo NasirNo ratings yet

- 17 - de Journal - EcsDocument48 pages17 - de Journal - EcsPrakalp JhaNo ratings yet

- VHDL Lab RecordDocument13 pagesVHDL Lab RecordRajBhanNo ratings yet

- 20mee207 Signal Mux Demux PASDocument27 pages20mee207 Signal Mux Demux PASSharad Patil DholeNo ratings yet

- Com Bi National Logic Design Using MSI CctsDocument4 pagesCom Bi National Logic Design Using MSI CctsRGiteyaNo ratings yet

- K-MAP MINIMIZATIONDocument49 pagesK-MAP MINIMIZATIONPavithraNo ratings yet

- 17 - de Exp Journal - EcsDocument48 pages17 - de Exp Journal - EcsPrakalp JhaNo ratings yet

- Lab Report 4Document10 pagesLab Report 4abdulbabulNo ratings yet

- Lab Exercise #7: Decoders, Multiplexors, Shifters and EncodersDocument8 pagesLab Exercise #7: Decoders, Multiplexors, Shifters and EncodersRenita MinkNo ratings yet

- Multiplexer and DemultiplexerDocument18 pagesMultiplexer and DemultiplexerTara SharmaNo ratings yet

- Group 2 Report 3 VLSI E PDFDocument9 pagesGroup 2 Report 3 VLSI E PDFStrt SandyNo ratings yet

- 16 LEDs With 3 IineDocument9 pages16 LEDs With 3 IineWalid AliNo ratings yet

- Multiplex Er 1Document19 pagesMultiplex Er 1pkrk123456789100% (1)

- Implementation of Serial Peripheral Interface (Spi) For Lpc2148 MicrocontrollerDocument4 pagesImplementation of Serial Peripheral Interface (Spi) For Lpc2148 MicrocontrollerSanchit AgrawalNo ratings yet

- Multiplexer and DemultiplexerDocument5 pagesMultiplexer and DemultiplexerAdebayo AdebariNo ratings yet

- Coa Lab 4Document6 pagesCoa Lab 405raiuttuNo ratings yet

- Design 16:1 Mux Using VHDL Generator StatementDocument8 pagesDesign 16:1 Mux Using VHDL Generator StatementSoumya ChoubeyNo ratings yet

- University of Essex: School of Computer Science andDocument6 pagesUniversity of Essex: School of Computer Science andVlad SimizeanuNo ratings yet

- Unit 3 Combinational Functions1Document106 pagesUnit 3 Combinational Functions1sharvarictamaneNo ratings yet

- VERIFICATION OF TRUTH TABLES OF LOGIC GATES AND CIRCUITSDocument40 pagesVERIFICATION OF TRUTH TABLES OF LOGIC GATES AND CIRCUITSRockRahil100% (3)

- Interfacing With The ISA BusDocument12 pagesInterfacing With The ISA BusseyfiNo ratings yet

- Mpi ReportDocument20 pagesMpi ReportHoorain SajjadNo ratings yet

- DLD 7 StudentDocument6 pagesDLD 7 StudentAminul IslamNo ratings yet

- AppendixA ISCAS CircuitsDocument31 pagesAppendixA ISCAS Circuitsarshdeep1990No ratings yet

- Lab 9 Comb CKT With MUX and DEC Full PackageDocument4 pagesLab 9 Comb CKT With MUX and DEC Full PackageLoveWorldCanadaNo ratings yet

- 7 Segment IntterfaceDocument9 pages7 Segment IntterfaceGaneshRahulWolverine100% (2)

- Multiplexer & DemultiplexerDocument23 pagesMultiplexer & DemultiplexerVarunNo ratings yet

- Digital Open EndedDocument13 pagesDigital Open EndedudayNo ratings yet

- Combinational Logic Multiplexer ExperimentDocument7 pagesCombinational Logic Multiplexer ExperimentHarish RamasubramanianNo ratings yet

- MUXDocument6 pagesMUXSunil KumarNo ratings yet

- Digital Circuits - MultiplexersDocument6 pagesDigital Circuits - MultiplexerssardarzaibibalochNo ratings yet

- 16×4 EncoderDocument6 pages16×4 Encoderrmedu07.officialNo ratings yet

- Military College of Signals Digital Logic Design: Lab Engr HammadDocument9 pagesMilitary College of Signals Digital Logic Design: Lab Engr Hammadahmad khanNo ratings yet

- Apparatus Required:: TitleDocument4 pagesApparatus Required:: Titlesuchipriya muchandeNo ratings yet

- ADE Lecture11Document12 pagesADE Lecture11Baraa MuhammadNo ratings yet

- Project Report: Course Title: Digital Logic Design Course Code: CSE 345 Section: 2Document9 pagesProject Report: Course Title: Digital Logic Design Course Code: CSE 345 Section: 2sh laskarNo ratings yet

- UEC612 Digital Systems Design Tutorial Sheet-1Document1 pageUEC612 Digital Systems Design Tutorial Sheet-1PriyAnkKohLiNo ratings yet

- Damson University College of Engineering Computer Engineering DepartmentDocument5 pagesDamson University College of Engineering Computer Engineering DepartmentZedrik MojicaNo ratings yet

- PC Interfacing Fourth Level Lecture Four: Experiment Board Design and Expanding The CentronicDocument9 pagesPC Interfacing Fourth Level Lecture Four: Experiment Board Design and Expanding The Centronicأسامة المياحيNo ratings yet

- Chapter 3 - Encoder, DecoderDocument39 pagesChapter 3 - Encoder, Decodernizar_ayub95No ratings yet

- MP MC NotesDocument166 pagesMP MC NotesPalani Arjunan100% (1)

- Implementation of 8Ã 1 MultiplexerDocument5 pagesImplementation of 8Ã 1 MultiplexerFrancesco De FlorenceNo ratings yet

- Cadence Nclaunch LabDocument86 pagesCadence Nclaunch Labsweety987No ratings yet

- Driving Dot LED Matrix Displays with Parallel PortsDocument5 pagesDriving Dot LED Matrix Displays with Parallel PortsFrenzoe Nillas DemecilloNo ratings yet

- Multiplexer and DemultiplexerDocument12 pagesMultiplexer and Demultiplexermarck_camamaNo ratings yet

- Mux Ra1911004010178Document10 pagesMux Ra1911004010178Shivanshu TripathiNo ratings yet

- Ejemplo Comunicasion SpiDocument7 pagesEjemplo Comunicasion SpinoevidalNo ratings yet

- DLD Lab ManualDocument35 pagesDLD Lab ManualHrishikesh Garud100% (2)

- Design of Multiplexer and Demultiplexer Aim:: Dual 4-Line To 1-Line Multiplexer Dual 1-Line To 4-Line DemultiplexerDocument11 pagesDesign of Multiplexer and Demultiplexer Aim:: Dual 4-Line To 1-Line Multiplexer Dual 1-Line To 4-Line DemultiplexerPranav Satish0% (1)

- Design of Multiplexer and Demultiplexer Aim:: Dual 4-Line To 1-Line Multiplexer Dual 1-Line To 4-Line DemultiplexerDocument11 pagesDesign of Multiplexer and Demultiplexer Aim:: Dual 4-Line To 1-Line Multiplexer Dual 1-Line To 4-Line DemultiplexerPranav Satish100% (1)

- Experiment 6 - Multiplexer and Demultiplexer Using NAND GatesDocument6 pagesExperiment 6 - Multiplexer and Demultiplexer Using NAND GatesPrr PrrNo ratings yet

- Experiment 8Document6 pagesExperiment 8a57f06c601f1No ratings yet

- Philemon Bible StudyDocument8 pagesPhilemon Bible StudyThomas JamesNo ratings yet

- Design Methodologies LectureDocument95 pagesDesign Methodologies LectureThomas JamesNo ratings yet

- High Performance 8-Bit Display Interface AD9980: Features Functional Block DiagramDocument44 pagesHigh Performance 8-Bit Display Interface AD9980: Features Functional Block DiagramThomas JamesNo ratings yet

- B - Tech - B - Arch Degree Exam November, December 2015 NTFNDocument2 pagesB - Tech - B - Arch Degree Exam November, December 2015 NTFNThomas JamesNo ratings yet

- Electronics and Communication Ece Formula Book For Gate Ies and PsuDocument56 pagesElectronics and Communication Ece Formula Book For Gate Ies and PsuThomas James88% (16)

- Verilog HDL - Samir PalnitkarDocument403 pagesVerilog HDL - Samir PalnitkarSameer RaichurNo ratings yet

- DSP 2 LowpassfilterDocument20 pagesDSP 2 LowpassfilterDr-Atul Kumar DwivediNo ratings yet

- 200907261900DWC21ASAAA BeauHughes PhilemonPt2-ForgivenessDocument8 pages200907261900DWC21ASAAA BeauHughes PhilemonPt2-ForgivenessThomas JamesNo ratings yet

- 2420 0 Pap LXY SimulinkDocument5 pages2420 0 Pap LXY SimulinkThomas JamesNo ratings yet

- FPGA-Based Feature DetectionDocument9 pagesFPGA-Based Feature DetectionThomas JamesNo ratings yet

- EdatoolsDocument44 pagesEdatoolsThomas JamesNo ratings yet

- Exp 1Document7 pagesExp 1Thomas JamesNo ratings yet

- Exp18 THDocument3 pagesExp18 THThomas JamesNo ratings yet

- Lab3 - Create Simulink Edge DetectorDocument13 pagesLab3 - Create Simulink Edge DetectorArvind ChauhanNo ratings yet

- Experiment 12: Aim: Eda Tool Used: MethodologyDocument2 pagesExperiment 12: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- Exp18 THDocument3 pagesExp18 THThomas JamesNo ratings yet

- Exp18 THDocument3 pagesExp18 THThomas JamesNo ratings yet

- FPGA CPLD LAB Experiment 13 JK Flip-Flop Verilog DesignDocument2 pagesFPGA CPLD LAB Experiment 13 JK Flip-Flop Verilog DesignThomas JamesNo ratings yet

- Experiment 13: Aim: Eda Tool Used: MethodologyDocument2 pagesExperiment 13: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- Program 14Document3 pagesProgram 14Thomas JamesNo ratings yet

- DSP Lab Exponential SignalsDocument4 pagesDSP Lab Exponential SignalsThomas JamesNo ratings yet

- Experiment 11: Aim: Eda Tool Used: MethodologyDocument4 pagesExperiment 11: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- DSP Lab Report on Exponential SignalsDocument4 pagesDSP Lab Report on Exponential SignalsThomas JamesNo ratings yet

- Experiment 2 (B) : Aim: To Write A MATLAB Program To Receive An Input Sequence From The User and ToDocument4 pagesExperiment 2 (B) : Aim: To Write A MATLAB Program To Receive An Input Sequence From The User and ToThomas JamesNo ratings yet

- Implement AM FM Modulation Demodulation MATLABDocument4 pagesImplement AM FM Modulation Demodulation MATLABThomas JamesNo ratings yet

- Program 14Document3 pagesProgram 14Thomas JamesNo ratings yet

- Program 15Document4 pagesProgram 15Thomas JamesNo ratings yet