Professional Documents

Culture Documents

Experiment 5: Aim: Eda Tool Used: Methodology

Uploaded by

Thomas JamesOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Experiment 5: Aim: Eda Tool Used: Methodology

Uploaded by

Thomas JamesCopyright:

Available Formats

FPGA/ CPLD LAB

EXPERIMENT 5

AIM : To design a 4:1 multiplexer at different levels of modelling.

EDA TOOL USED : Xilinx ISE 8.1i

METHODOLOGY : A digital multiplexer is a combinational circuit that selects one digital

information from several sources and transmits the selected information on a single output line. A

mux is also called a data selector since it selects one of many inputs. If the number of n input lines is

equal to 2m then m select lines are required to select one of the input lines, for example, if there are 4

inputs, then 2 select lines are required.

Truth Table :

Select lines

Output

S1

S0

(Y)

I0

I1

I2

I3

Expression : Y = S1 S0 I0 + S1 S0 I1 + S1 S0 I2 + S1 S0 I3

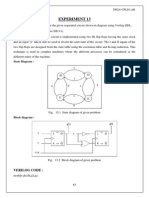

Block Diagam :

Fig 5.1 Block diagram of 4 : 1 MUX

VERILOG CODE :

Gate level Modelling

module muxb(I0, I1, I2, I3, S0, S1, Y);

input I0,I1,I2,I3,S0,S1;

output Y;

wire t0,t1,r0,r1,r2,r3;

not(t0,S0); not(t1,S1); and(r0,I0,t0,t1); and(r1,I1,S0,t1);

and(r2,I2,t0,S1); and(r3,I3,S0,S1);

or(Y,r0,r1,r2,r3);

endmodule

26

FPGA/ CPLD LAB

Data flow level Modelling

Using Continuous statements:

module muxd1(I0, I1, I2, I3, S0, S1, Y);

input I0,I1,I2,I3,S0,S1;

output Y;

assign {Y}=(I0&(~S1)&(~S0))|(I1&(~S1)&(S0))|(I2&(S1)&(~S0))|(I3&(S1)&(S0));

endmodule

Using conditional statement:

module muxd2(I0, I1, I2, I3, S0, S1, Y);

input I0,I1,I2, I3,S0,S1;

output Y;

assign {Y}=S0?(S1?I3:I1):(S1?I2:I0);

endmodule

Behavioural level Modelling

module muxb(I,S,Y);

input [3:0]I; input [1:0]S; output reg Y;

always@(I,S)

begin

case(S)

0: begin

Y=I[0]; end

1: begin

Y=I[1]; end

2: begin

Y=I[2]; end

3: begin

Y=I[3]; end

endcase

end

endmodule

RTL SCHEMATIC VIEW :

Gate level Modelling

Fig 5.2 RTL schematic of 4 : 1 MUX

27

FPGA/ CPLD LAB

Data flow level Modelling

(a)

(b)

Fig 5.3 (a) & (b) RTL schematic of 4 : 1 MUX

Behavioural level Modelling

(a)

28

FPGA/ CPLD LAB

(b)

Fig 5.4 (a) & (b) RTL schematic of 4 : 1 MUX

OUTPUT WAVEFORM :

Fig 5.5 Output waveform of 4 : 1 MUX

RESULT : Successfully implemented 4 : 1 MUX using different levels of modelling and verified

its operation through simulation.

29

You might also like

- Experiment 5: Aim: Eda Tool Used: MethodologyDocument4 pagesExperiment 5: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- Chapter #5Document22 pagesChapter #5علوم حاسبNo ratings yet

- Encoders and Multiplexer CircuitsDocument22 pagesEncoders and Multiplexer CircuitsahmedNo ratings yet

- Exp 5Document6 pagesExp 5RishabhNo ratings yet

- Mux Demux Encoder DecoderDocument18 pagesMux Demux Encoder Decoderaryan.bhosale002No ratings yet

- Lab Exercise #7: Decoders, Multiplexors, Shifters and EncodersDocument8 pagesLab Exercise #7: Decoders, Multiplexors, Shifters and EncodersRenita MinkNo ratings yet

- University of Essex: School of Computer Science andDocument6 pagesUniversity of Essex: School of Computer Science andVlad SimizeanuNo ratings yet

- Bolean Implementation Using MuxDocument29 pagesBolean Implementation Using Muxabhishek kolseNo ratings yet

- Chapter 3 - Encoder, DecoderDocument39 pagesChapter 3 - Encoder, Decodernizar_ayub95No ratings yet

- Group 2 Report 3 VLSI E PDFDocument9 pagesGroup 2 Report 3 VLSI E PDFStrt SandyNo ratings yet

- VHDL Lab RecordDocument13 pagesVHDL Lab RecordRajBhanNo ratings yet

- Lab Report 4Document10 pagesLab Report 4abdulbabulNo ratings yet

- 20mee207 Signal Mux Demux PASDocument27 pages20mee207 Signal Mux Demux PASSharad Patil DholeNo ratings yet

- Experiment 10: Multiplexers: Mr. Mohamed El-SaiedDocument4 pagesExperiment 10: Multiplexers: Mr. Mohamed El-SaiedEstéfano GómezNo ratings yet

- Experiment-5: Aim: To Write VHDL Code For 4 To 1 MUX and Observe The Waveform and Synthesize The CodeDocument3 pagesExperiment-5: Aim: To Write VHDL Code For 4 To 1 MUX and Observe The Waveform and Synthesize The CodeYidnekachwe MekuriaNo ratings yet

- VLSI Design Lab EC-16203 Experiment 4 ObjectiveDocument5 pagesVLSI Design Lab EC-16203 Experiment 4 ObjectiveBrajesh SainiNo ratings yet

- Experiment 6: Aim: Eda Tool Used: MethodologyDocument4 pagesExperiment 6: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- Cadence Nclaunch LabDocument86 pagesCadence Nclaunch Labsweety987No ratings yet

- Project Report: Course Title: Digital Logic Design Course Code: CSE 345 Section: 2Document9 pagesProject Report: Course Title: Digital Logic Design Course Code: CSE 345 Section: 2sh laskarNo ratings yet

- Aim: - Tool Used: Theory:: Experiment-5Document4 pagesAim: - Tool Used: Theory:: Experiment-5udayNo ratings yet

- LR 3Document9 pagesLR 3noirNo ratings yet

- Experiment 8Document6 pagesExperiment 8a57f06c601f1No ratings yet

- Military College of Signals Digital Logic Design: Lab Engr HammadDocument9 pagesMilitary College of Signals Digital Logic Design: Lab Engr Hammadahmad khanNo ratings yet

- VHDL ProgramsDocument30 pagesVHDL ProgramsVijay Singh100% (1)

- 13 PLC Program To Implement 4.1 MultiplexerDocument3 pages13 PLC Program To Implement 4.1 MultiplexerMaria GuerreroNo ratings yet

- Aim: To Perform Simulation and Synthesis of 4:1 Multiplexer and 1:4 De-Multiplexer UsingDocument13 pagesAim: To Perform Simulation and Synthesis of 4:1 Multiplexer and 1:4 De-Multiplexer UsingEr Shubham RaksheNo ratings yet

- VERIFICATION OF TRUTH TABLES OF LOGIC GATES AND CIRCUITSDocument40 pagesVERIFICATION OF TRUTH TABLES OF LOGIC GATES AND CIRCUITSRockRahil100% (3)

- FALLSEM2022-23 BECE102L TH VL2022230104585 Reference Material I 10-09-2022 Module-3 PDFDocument92 pagesFALLSEM2022-23 BECE102L TH VL2022230104585 Reference Material I 10-09-2022 Module-3 PDFChiranjeev Vishnoi 21BCT0043No ratings yet

- II & III UnitsDocument25 pagesII & III UnitsManasa PillavadanNo ratings yet

- DDL 06Document8 pagesDDL 06Anonymous KLGejaVNo ratings yet

- Chapter 9 Notes: 9.1 Binary Decoders - Acts Much Like A Switch Statement in The C LanguageDocument12 pagesChapter 9 Notes: 9.1 Binary Decoders - Acts Much Like A Switch Statement in The C LanguageRahul SinghNo ratings yet

- Logic Design Lab ManualDocument22 pagesLogic Design Lab ManualAzarkhan Mokashi100% (1)

- Experiment No.3: Aim: Tool RequiredDocument12 pagesExperiment No.3: Aim: Tool RequiredRohit PanwarNo ratings yet

- Data Processing CircuitsDocument19 pagesData Processing CircuitsBhaskar MNo ratings yet

- DSD LabDocument42 pagesDSD LabArun GoyalNo ratings yet

- VLSI Lab5Document4 pagesVLSI Lab5Aayan ShahNo ratings yet

- Lecture 9 - MSI CircuitsDocument56 pagesLecture 9 - MSI CircuitsTECH BANGLADESHNo ratings yet

- Experiment 2: Inputs OutputDocument6 pagesExperiment 2: Inputs OutputSdoNo ratings yet

- Military College Digital Logic Design Lab Report 08Document4 pagesMilitary College Digital Logic Design Lab Report 08ahmad khanNo ratings yet

- Experiment Number (6) 4:1 Multiplexer: Digital Electronic LabDocument5 pagesExperiment Number (6) 4:1 Multiplexer: Digital Electronic Labewnetu kassaNo ratings yet

- Interfacing With The ISA BusDocument12 pagesInterfacing With The ISA BusseyfiNo ratings yet

- Dl4 Comb DevicesDocument13 pagesDl4 Comb Devicesomgcharlie12No ratings yet

- Experiment No.: 10Document5 pagesExperiment No.: 10samrudhiNo ratings yet

- Chip Neuron Lonworks PDFDocument19 pagesChip Neuron Lonworks PDFCesar PalaciosNo ratings yet

- Ecad & Vlsi Lab Manual - MrecwDocument104 pagesEcad & Vlsi Lab Manual - Mrecwvaseem_ahmedNo ratings yet

- Course Title: Digital Electronics Lab Course Code: CSE224 Experiment NameDocument7 pagesCourse Title: Digital Electronics Lab Course Code: CSE224 Experiment NameSajib BormonNo ratings yet

- CO Lab Manual-MinDocument40 pagesCO Lab Manual-MinMatheen TabidNo ratings yet

- Design of Multiplexer and Demultiplexer Aim:: Dual 4-Line To 1-Line Multiplexer Dual 1-Line To 4-Line DemultiplexerDocument11 pagesDesign of Multiplexer and Demultiplexer Aim:: Dual 4-Line To 1-Line Multiplexer Dual 1-Line To 4-Line DemultiplexerPranav Satish0% (1)

- Design of Multiplexer and Demultiplexer Aim:: Dual 4-Line To 1-Line Multiplexer Dual 1-Line To 4-Line DemultiplexerDocument11 pagesDesign of Multiplexer and Demultiplexer Aim:: Dual 4-Line To 1-Line Multiplexer Dual 1-Line To 4-Line DemultiplexerPranav Satish100% (1)

- DLD 7 StudentDocument6 pagesDLD 7 StudentAminul IslamNo ratings yet

- Multiplexers & Demultiplexers: Object: TheoryDocument4 pagesMultiplexers & Demultiplexers: Object: TheoryMonir JihadNo ratings yet

- Chapter 3 - Combinational Logic DesignDocument36 pagesChapter 3 - Combinational Logic Designmahbub mitulNo ratings yet

- Digital Logic Design Laboratory Manual: ObjectiveDocument8 pagesDigital Logic Design Laboratory Manual: ObjectiveDawit Adane KebedeNo ratings yet

- Comb CircuitsDocument11 pagesComb CircuitsShekhil HassanNo ratings yet

- Experiment 6 - Multiplexer and Demultiplexer Using NAND GatesDocument6 pagesExperiment 6 - Multiplexer and Demultiplexer Using NAND GatesPrr PrrNo ratings yet

- Unit 3 Combinational Functions1Document106 pagesUnit 3 Combinational Functions1sharvarictamaneNo ratings yet

- LAB #04 Task #01: Implement 4X1 Mux by Calling 2x1 Mux ?Document14 pagesLAB #04 Task #01: Implement 4X1 Mux by Calling 2x1 Mux ?kiranNo ratings yet

- High Performance 8-Bit Display Interface AD9980: Features Functional Block DiagramDocument44 pagesHigh Performance 8-Bit Display Interface AD9980: Features Functional Block DiagramThomas JamesNo ratings yet

- Philemon Bible StudyDocument8 pagesPhilemon Bible StudyThomas JamesNo ratings yet

- Electronics and Communication Ece Formula Book For Gate Ies and PsuDocument56 pagesElectronics and Communication Ece Formula Book For Gate Ies and PsuThomas James88% (16)

- Design Methodologies LectureDocument95 pagesDesign Methodologies LectureThomas JamesNo ratings yet

- 200907261900DWC21ASAAA BeauHughes PhilemonPt2-ForgivenessDocument8 pages200907261900DWC21ASAAA BeauHughes PhilemonPt2-ForgivenessThomas JamesNo ratings yet

- DSP 2 LowpassfilterDocument20 pagesDSP 2 LowpassfilterDr-Atul Kumar DwivediNo ratings yet

- 2420 0 Pap LXY SimulinkDocument5 pages2420 0 Pap LXY SimulinkThomas JamesNo ratings yet

- Experiment 12: Aim: Eda Tool Used: MethodologyDocument2 pagesExperiment 12: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- FPGA-Based Feature DetectionDocument9 pagesFPGA-Based Feature DetectionThomas JamesNo ratings yet

- Exp18 THDocument3 pagesExp18 THThomas JamesNo ratings yet

- Lab3 - Create Simulink Edge DetectorDocument13 pagesLab3 - Create Simulink Edge DetectorArvind ChauhanNo ratings yet

- B - Tech - B - Arch Degree Exam November, December 2015 NTFNDocument2 pagesB - Tech - B - Arch Degree Exam November, December 2015 NTFNThomas JamesNo ratings yet

- Verilog HDL - Samir PalnitkarDocument403 pagesVerilog HDL - Samir PalnitkarSameer RaichurNo ratings yet

- Exp18 THDocument3 pagesExp18 THThomas JamesNo ratings yet

- Exp18 THDocument3 pagesExp18 THThomas JamesNo ratings yet

- EdatoolsDocument44 pagesEdatoolsThomas JamesNo ratings yet

- Exp 1Document7 pagesExp 1Thomas JamesNo ratings yet

- FPGA CPLD LAB Experiment 13 JK Flip-Flop Verilog DesignDocument2 pagesFPGA CPLD LAB Experiment 13 JK Flip-Flop Verilog DesignThomas JamesNo ratings yet

- Experiment 6: Aim: Eda Tool Used: MethodologyDocument4 pagesExperiment 6: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- Experiment 11: Aim: Eda Tool Used: MethodologyDocument4 pagesExperiment 11: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- Program 15Document4 pagesProgram 15Thomas JamesNo ratings yet

- Experiment 13: Aim: Eda Tool Used: MethodologyDocument2 pagesExperiment 13: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- Implement AM FM Modulation Demodulation MATLABDocument4 pagesImplement AM FM Modulation Demodulation MATLABThomas JamesNo ratings yet

- DSP Lab Report on Exponential SignalsDocument4 pagesDSP Lab Report on Exponential SignalsThomas JamesNo ratings yet

- DSP Lab Exponential SignalsDocument4 pagesDSP Lab Exponential SignalsThomas JamesNo ratings yet

- Program 14Document3 pagesProgram 14Thomas JamesNo ratings yet

- Program 14Document3 pagesProgram 14Thomas JamesNo ratings yet

- Experiment 2 (B) : Aim: To Write A MATLAB Program To Receive An Input Sequence From The User and ToDocument4 pagesExperiment 2 (B) : Aim: To Write A MATLAB Program To Receive An Input Sequence From The User and ToThomas JamesNo ratings yet