Professional Documents

Culture Documents

Comparator ALU

Comparator ALU

Uploaded by

FaiizNartwadee0 ratings0% found this document useful (0 votes)

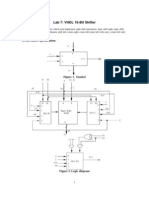

6 views1 pageThis document describes a VHDL module for a comparator ALU. The module takes in two 4-bit inputs A and B and outputs signals to indicate whether A equals B, A is greater than B, or A is less than B. It also takes in a 3-bit selection signal and outputs a 4-bit result based on the selected operation, which includes subtraction, addition, XOR, OR, and AND.

Original Description:

Original Title

comparator_ALU

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document describes a VHDL module for a comparator ALU. The module takes in two 4-bit inputs A and B and outputs signals to indicate whether A equals B, A is greater than B, or A is less than B. It also takes in a 3-bit selection signal and outputs a 4-bit result based on the selected operation, which includes subtraction, addition, XOR, OR, and AND.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

6 views1 pageComparator ALU

Comparator ALU

Uploaded by

FaiizNartwadeeThis document describes a VHDL module for a comparator ALU. The module takes in two 4-bit inputs A and B and outputs signals to indicate whether A equals B, A is greater than B, or A is less than B. It also takes in a 3-bit selection signal and outputs a 4-bit result based on the selected operation, which includes subtraction, addition, XOR, OR, and AND.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

comparator_ALU.

vhd Thu Dec 30 23:14:08 2010

1 ----------------------------------------------------------------------------------

2 -- Create Date: 21:51:50 12/30/2010 -- Module Name: comparator_ALU - Behavioral

3 ----------------------------------------------------------------------------------

4 library IEEE;

5 use IEEE.STD_LOGIC_1164.ALL;

6 use ieee.std_logic_unsigned.all;

7

8 entity comparator_ALU is

9 Port ( A : in STD_LOGIC_VECTOR (3 downto 0);

10 B : in STD_LOGIC_VECTOR (3 downto 0);

11 AeqB : out STD_LOGIC;

12 AgtB : out STD_LOGIC;

13 AltB : out STD_LOGIC;

14 s : in STD_LOGIC_VECTOR (2 downto 0);

15 F : out STD_LOGIC_VECTOR (3 downto 0));

16 end comparator_ALU;

17

18 architecture Behavioral of comparator_ALU is

19 begin

20 AeqB <= '1' when A = B else '0';

21 AgtB <= '1' when A > B else '0';

22 AltB <= '1' when A < B else '0';

23 process (s,A,B)

24 begin

25 case s is

26 when "000" => F <= "0000";

27 when "001" => F <= B - A;

28 when "010" => F <= A - B;

29 when "011" => F <= A + B;

30 when "100" => F <= A xor B;

31 when "101" => F <= A or B;

32 when "110" => F <= A and B;

33 when others => F <= "1111";

34 end case;

35 end process;

36 end Behavioral;

Page 1

You might also like

- VHDL Codes For Mips Instructions LW, SW, Beq, Bne, J, Jal, Lui, Add, Addi, Or, Ori, SLT, Nor, And, ExceptionsDocument24 pagesVHDL Codes For Mips Instructions LW, SW, Beq, Bne, J, Jal, Lui, Add, Addi, Or, Ori, SLT, Nor, And, ExceptionsbingoahaNo ratings yet

- VHDL KeypadDocument17 pagesVHDL Keypadtroid426No ratings yet

- Vlsi 2ND AssignmentDocument9 pagesVlsi 2ND Assignmentshivanimali9096No ratings yet

- Exp9 Shresht GuptaDocument9 pagesExp9 Shresht GuptaLakshay SharmaNo ratings yet

- FinalSolutions F09Document8 pagesFinalSolutions F09boooreshNo ratings yet

- Raisul Falah - (165060300111051) - Lab1Document11 pagesRaisul Falah - (165060300111051) - Lab1Wibi Wisnu WNo ratings yet

- Coding:: VHDL Code For BufferDocument27 pagesCoding:: VHDL Code For BufferAar Kay GautamNo ratings yet

- HDL Lab Manual For VTUDocument93 pagesHDL Lab Manual For VTULavanya Vaishnavi D.A.No ratings yet

- ch5 PDFDocument9 pagesch5 PDFSrinivas CherukuNo ratings yet

- Combinational Logic Circuits: Prof. David Márquez ViloriaDocument16 pagesCombinational Logic Circuits: Prof. David Márquez ViloriaJose Mateo Aristizabal DiazNo ratings yet

- Aim: Hardware RequiredDocument12 pagesAim: Hardware RequiredfjhgfiuyufyjNo ratings yet

- Library Ieee Use Ieee - STD - Logic - 1164.all Use Ieee - STD - Logic - Unsigned - All UseDocument7 pagesLibrary Ieee Use Ieee - STD - Logic - 1164.all Use Ieee - STD - Logic - Unsigned - All Useshib_sankarNo ratings yet

- Ruta de DatosDocument3 pagesRuta de DatosPercy Julio Chambi PaccoNo ratings yet

- Adsd Lab Experiments: NAME: Ankit Mukherjee REG NO: RA1911043040015 Class: Ece B'Document29 pagesAdsd Lab Experiments: NAME: Ankit Mukherjee REG NO: RA1911043040015 Class: Ece B'AnkitShubhoeMukherjeeNo ratings yet

- Federal Democratic Republic of Ethiopia Ministry of Defense Defense University, College of EngineeringDocument12 pagesFederal Democratic Republic of Ethiopia Ministry of Defense Defense University, College of EngineeringmelkamzerNo ratings yet

- VHDLDocument8 pagesVHDLAngieNo ratings yet

- ALU ProjectDocument10 pagesALU Projectsalmamaher2323No ratings yet

- VlsiDocument37 pagesVlsiRitwik SoniNo ratings yet

- MELZG623 Assignment 2Document11 pagesMELZG623 Assignment 2crypto.investnment100% (1)

- ArchitectureDocument50 pagesArchitectureEnanko Babaiya BasakNo ratings yet

- Digital Logic LAB Manual KL-300 (Shorted)Document66 pagesDigital Logic LAB Manual KL-300 (Shorted)s_afwan78% (9)

- Lab 7: VHDL 16-Bit ShifterDocument6 pagesLab 7: VHDL 16-Bit ShifterAvinash VikramNo ratings yet

- ALU CODE and TEST BENCHDocument8 pagesALU CODE and TEST BENCHSumit PatilNo ratings yet

- Digital System Design With VHDLDocument70 pagesDigital System Design With VHDLMohammed Wagih EmamNo ratings yet

- Verilog NotesDocument41 pagesVerilog NotesJaya SreeNo ratings yet

- VHDLDocument55 pagesVHDLparassh knowledgeNo ratings yet

- Ejercicio Compuerta ANDDocument4 pagesEjercicio Compuerta ANDJose Luis Martinez RochaNo ratings yet

- Entity Alu IsDocument3 pagesEntity Alu IsDiego Jarosky Chachayma FarfánNo ratings yet

- Library IEEE Use IEEE - STD - LOGIC - 1164.ALL Use Ieee - STD - Logic - Unsigned - All Use Ieee - STD - Logic - Arith - AllDocument4 pagesLibrary IEEE Use IEEE - STD - LOGIC - 1164.ALL Use Ieee - STD - Logic - Unsigned - All Use Ieee - STD - Logic - Arith - AllLeydycita HemofixNo ratings yet

- Exp - No: 1 Basic Gates Date: 30.01.10 - AimDocument31 pagesExp - No: 1 Basic Gates Date: 30.01.10 - AimmanichennaiNo ratings yet

- Electronics Design Lab Manual - VLSI Prog-V3Document14 pagesElectronics Design Lab Manual - VLSI Prog-V3shanmugasundatamNo ratings yet

- Scheme Quartus ASC Pentru Primul Subiect Poarta ŞiDocument11 pagesScheme Quartus ASC Pentru Primul Subiect Poarta ŞiAlin ChiperNo ratings yet

- Taller de Diseños de Sistemas DigitalesDocument22 pagesTaller de Diseños de Sistemas DigitalesCarlos Sánchez NietoNo ratings yet

- VHDL Code For Arithmetic and Logic UnitDocument4 pagesVHDL Code For Arithmetic and Logic Unitmeaow88No ratings yet

- CENG355 Final Exam Spring2019 SolutionDocument13 pagesCENG355 Final Exam Spring2019 SolutionHadi SleemNo ratings yet

- Testbench For OR GateDocument5 pagesTestbench For OR GateMae ZelNo ratings yet

- Bach Khoa University of Technology: Digital Systems Laboratory Prelab 4 Finite State MachineDocument11 pagesBach Khoa University of Technology: Digital Systems Laboratory Prelab 4 Finite State MachineMờ LanhNo ratings yet

- Práctica 3 VHDLDocument31 pagesPráctica 3 VHDLmoises garciaNo ratings yet

- Bài 1: thiết kế mạch giải mã 3 -8Document7 pagesBài 1: thiết kế mạch giải mã 3 -8Thắng TrầnNo ratings yet

- Half AdderDocument11 pagesHalf AdderTahsin RahmanNo ratings yet

- VHDL Examples - Combinational LogicDocument28 pagesVHDL Examples - Combinational Logicbinhnhi0007No ratings yet

- VHDL Prei Nforme 4Document19 pagesVHDL Prei Nforme 4R Patty FloresNo ratings yet

- HDL ProgramDocument6 pagesHDL ProgramChethan RaoNo ratings yet

- Termend-I - Key Cat1 PPR OldDocument8 pagesTermend-I - Key Cat1 PPR OldSANJUCTA CHOUDHURYNo ratings yet

- Tutorial 1Document29 pagesTutorial 1A'ziz MoNo ratings yet

- Solution Manual of Appendix A Exercise at (CMOS VLSI Design) by NEILL and HarrisDocument13 pagesSolution Manual of Appendix A Exercise at (CMOS VLSI Design) by NEILL and HarrisAhmed Gad100% (1)

- DSD VHDL Ch4Document31 pagesDSD VHDL Ch4Amanda JoshNo ratings yet

- Verilog Programs 5th UnitDocument14 pagesVerilog Programs 5th UnitVenkat ChadalavadaNo ratings yet

- Experiment No.1: A Binary To Gray ConverterDocument26 pagesExperiment No.1: A Binary To Gray ConverterVarun SharmaNo ratings yet

- Verilog Implementation of Single Cycle MicroprocessorDocument13 pagesVerilog Implementation of Single Cycle MicroprocessorAbhinav JhaNo ratings yet

- ECE-223, Solutions For Assignment #5Document4 pagesECE-223, Solutions For Assignment #5RUBIONo ratings yet

- Unit2 VHDL ProgDocument15 pagesUnit2 VHDL Progsayan.transcuratorsNo ratings yet

- Basic Gates ProgramDocument34 pagesBasic Gates ProgramJoychandra LoukrakpamNo ratings yet

- CA PracticalDocument11 pagesCA PracticalBidhan BaraiNo ratings yet

- LAB 3 - Bayu Abi Pamungkas - 165060300111007Document6 pagesLAB 3 - Bayu Abi Pamungkas - 165060300111007Bayu Abi PamungkasNo ratings yet

- Engr2015 Lab2Document13 pagesEngr2015 Lab2SUPER AMAZINGNo ratings yet

- Behavioral Modeling: 1. Design A 4:1 MUXDocument5 pagesBehavioral Modeling: 1. Design A 4:1 MUXIshan DarwhekarNo ratings yet

- Optrex Im50240 Modificacion 2Document8 pagesOptrex Im50240 Modificacion 2Pedro PerezNo ratings yet

- Abu Minhaj Farooqi 37560 Fpga Final ExamDocument20 pagesAbu Minhaj Farooqi 37560 Fpga Final ExamMinhaj FarooqiNo ratings yet