Professional Documents

Culture Documents

Digital Signal Processor C5X Addressing Modes

Digital Signal Processor C5X Addressing Modes

Uploaded by

jagadeesh mohan kumar0 ratings0% found this document useful (0 votes)

2 views40 pagesModes

Original Title

208356574 Digital Signal Processor C5X Addressing Modes

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentModes

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

2 views40 pagesDigital Signal Processor C5X Addressing Modes

Digital Signal Processor C5X Addressing Modes

Uploaded by

jagadeesh mohan kumarModes

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 40

TMS320C5X Addressing Modes

2/21/2014 Abhishek KumarSrivastava 1

Assembly Language Syntax

• A source statement can contain four ordered fields. Those are:

[label] [:] mnemonic [operand list] [;comment]

• Rules to be followed:

1. All statement begin with label, blank, asterisk or semicolon.

2. Labels (optional); must begin in column 1

3. Labels either placed before instruction in same line or on the

preceding line in first column.

4. Blank separate each fields of statement.

5. Comments are optional; begins with ‘*’ or ‘;’.

2/21/2014 Abhishek KumarSrivastava 2

Addressing Modes

• C5X processors can address 64K words of program memory

and 96K words of data memory.

• C5X supports following 6 addressing modes:

1. Direct addressing

2. Memory-mapped register addressing

3. Indirect addressing

4. Immediate addressing

5. Dedicated-register addressing

6. Circular addressing

2/21/2014 Abhishek KumarSrivastava 3

Direct Memory Addressing

• In the direct memory addressing mode, the instruction contains

the lower 7 bits of the data memory address (dma).

• The 7-bit dma is concatenated with the 9 bits of the data

memory page pointer (DP) in status register 0 to form the full

16-bit data memory address.

• This 16-bit data memory address is placed on an internal direct

data memory address bus (DAB).

• The DP points to one of 512 possible data memory pages and

the 7-bit address in the instruction points to one of 128 words

within that data memory page.

• You can load the DP bits by using the LDP or the LST #0

instruction.

2/21/2014 Abhishek KumarSrivastava 4

2/21/2014 Abhishek KumarSrivastava 5

Shift left by 5 bits then added to ACC.

0 = Direct

addressing

mode

Data memory page Data memory

pointer, points to address, points to

page number 19Dh word 010h=16d in

= 413d page 19Dh

2/21/2014 Abhishek KumarSrivastava 6

Indirect Addressing

• Uses Eight 16-bit auxiliary registers (AR0–AR7).

• In indirect addressing, any location in the 64K-word data

memory space can be accessed using a 16-bit address

contained in an AR.

• To select a specific AR, load the ARP with a value from 0

through 7, designating AR0 through AR7, respectively.

• The register pointed to by the ARP is referred to as the current

auxiliary register (current AR).

• You can load the address into the AR using the LAR instruction.

2/21/2014 Abhishek KumarSrivastava 7

2/21/2014 Abhishek KumarSrivastava 8

• You can change the content of the AR by the:

• ADRK instruction (The 8-bit immediate value, right-justified, is

added to current AR using ARAU. The result is stored in the AR.)

• MAR instruction (The MAR instruction modifies the ARs or the

ARP bits, and the old ARP bits are copied to the ARB bits.)

• SBRK instruction (The 8-bit immediate value, right-justified, is

subtracted from the current AR using ARAU. The result is stored

in the current AR.)

2/21/2014 Abhishek KumarSrivastava 9

• The content of the current AR is used as the address of the

data memory operand.

• After the instruction uses the data value, the content of the

current AR can be incremented or decremented by the

auxiliary register arithmetic unit (ARAU), which implements

unsigned 16-bit arithmetic.

• The ARAU performs auxiliary register arithmetic operations in

the decode phase of the pipeline.

• This allows the address to be generated before the decode

phase of the next instruction.

2/21/2014 Abhishek KumarSrivastava 10

• The content of the current AR is incremented or decremented

after it is used in the current instruction.

• You can load the ARs via the data bus by using memory-

mapped writes to the ARs.

• Be careful when using these memory-mapped loads of the

ARs because, in this case, the memory-mapped ARs are

modified in the execute phase of the pipeline, causing a

pipeline conflict, if one of the next two instruction words

modifies same AR (without memory mapped).

2/21/2014 Abhishek KumarSrivastava 11

• There are two ways to use the ARs for purposes other than

referencing data memory addresses:

1. Use the ARs to support conditional branches, calls, and

returns by using the CMPR instruction.

• This instruction compares the content of the current AR

with the content of the auxiliary register compare register

(ARCR) and puts the result in the test/control (TC) flag bit of

status register ST1.

2. Use the ARs for temporary storage by using the LAR

instruction to load a value into the AR and the SAR

instruction to store the AR value to a data memory

location.

2/21/2014 Abhishek KumarSrivastava 12

Indirect Addressing Options

• Here, the instruction uses the content of the current AR as

the data memory address.

• The ’C5x provides four indirect addressing options:

1. No increment or decrement (*) in AR content.

2. Increment or decrement by one (*+ or *-) in AR content.

3. Increment or decrement by an index amount (*0+ or *0-) in

AR content.

4. Increment or decrement by an index amount using reverse

carry added or subtracted (*BR0+ or *BR0-) (carry

propagating in the reverse direction from MSB to the LSB) in

AR content.

2/21/2014 Abhishek KumarSrivastava 13

Indirect Addressing Opcode Format

2/21/2014 Abhishek KumarSrivastava 14

2/21/2014 Abhishek KumarSrivastava 15

2/21/2014 Abhishek KumarSrivastava 16

2/21/2014 Abhishek KumarSrivastava 17

2/21/2014 Abhishek KumarSrivastava 18

Bit-Reversed Addressing

• In the bit-reversed addressing mode, INDX specifies one-half the

size of the FFT.

• The value contained in the current AR must be equal to 2n-1, where

n is an integer, and the FFT size is 2n.

• An auxiliary register points to the physical location of a data value.

• When you add INDX to the current AR using bit-reversed

addressing, addresses are generated in a bit-reversed fashion.

• When you add INDX to the current AR using bit-reversed

addressing, addresses are generated in a bit-reversed fashion.

• Assume that the auxiliary registers are eight bits long, AR2

represents the base address of the data in memory (0110 00002),

and that INDX contains the value 0000 10002.

2/21/2014 Abhishek KumarSrivastava 19

2/21/2014 Abhishek KumarSrivastava 20

Immediate Addressing

• In immediate addressing, the instruction word(s) contains the

value of the immediate operand.

• The ’C5x has both 1-word (8-bit, 9-bit, and 13-bit constant)

short immediate instructions and 2-word (16-bit constant)

long immediate instructions.

2/21/2014 Abhishek KumarSrivastava 21

Short Immediate Addressing

• In short immediate instructions, the operand is contained

within the instruction machine code.

• In this example, the lower 8 bits are the operand and will be

added to the ACC by the CALU.

2/21/2014 Abhishek KumarSrivastava 22

Long Immediate Addressing

• In long immediate instructions, the operand is

contained in the second word of a two-word

instruction.

2/21/2014 Abhishek KumarSrivastava 23

Data memory address,

Data memory page pointer, points points to word 012h=18d in

to page number 19Dh = 413d page 19Dh

2/21/2014 Abhishek KumarSrivastava 24

Dedicated-Register Addressing

• The dedicated-registered addressing mode operates like the

long immediate addressing mode, except that the address

comes from one of two special-purpose memory-mapped

registers in the CPU: the block move address register (BMAR)

and the dynamic bit manipulation register (DBMR).

• The advantage of this addressing mode is that the address of

the block of memory to be acted upon can be changed

during execution of the program.

2/21/2014 Abhishek KumarSrivastava 25

DP=6; 6X128 =

768d + 10d =

778d=030Ah

The PLU executes a read-modify-write operation on data stored in data space.

First, one operand is fetched from data memory space, and the second is fetched

from a long immediate on the program bus or from the dynamic bit manipulation

register (DBMR). Then, the PLU executes a logical operation on the two operands as

defined by the instruction. The result is written to the same data memory location

from which the first operand was fetched, without affecting ACC or PREG.

2/21/2014 Abhishek KumarSrivastava 26

Using the Contents of the BMAR

• The BLDD, BLDP, and BLPD instructions use the BMAR (holds an

address value for use with block moves or multiply/

accumulates).

2/21/2014 Abhishek KumarSrivastava 27

Role of PFC

• A 16-bit counter used to prefetch program instructions.

• The PFC contains the address of the instruction currently being

prefetched and is updated when a new prefetch is initiated.

• Once an instruction is prefetched, the instruction is loaded into

the IREG, unless the IREG still contains an instruction currently

executing, in which case the prefetched instruction is stored in

the QIR (Queue Instruction Register).

• The PFC is then incremented, and after the current instruction

has completed execution, the instruction in the QIR is loaded into

the IREG to be executed.

• The PFC is also used to address program memory when using

the block move (BLPD), multiply-accumulate (MAC/MACD), and

table read/write (TBLR/TBLW) instructions and to address data

memory when using the block move (BLDD) instruction.

2/21/2014 Abhishek KumarSrivastava 28

Role of PFC

• The long immediate addressing or BMAR also could apply for

a “second data memory access” for the execution of the

instruction (Immediate Addressing Mode).

• The prefetch counter (PFC) is pushed onto the microcall stack

(MCS), and the long immediate value or BMAR is loaded into

the PFC.

• The program address/data bus is then used for the operand

fetch or write.

• At the completion of the instruction, the MCS is popped back

to the PFC, the program counter (PC) is incremented by two

(long immediate operand), and execution continues.

2/21/2014 Abhishek KumarSrivastava 29

2/21/2014 Abhishek KumarSrivastava 30

Using the Contents of the DBMR

• The APL, CPL, OPL, XPL instructions use the PLU and the

contents of the DBMR when an immediate value is not

specified as one of the operands.

• APL (AND data memory value with DBMR, and store result in

data memory location)

• CPL (Compare data memory value with DBMR)

• OPL (OR data memory value with DBMR and store result in

data memory location)

• XPL (Exclusive-OR data memory value with DBMR and store

result in data memory location)

2/21/2014 Abhishek KumarSrivastava 31

Memory-Mapped Register Addressing

• With memory-mapped register addressing, you can modify

the memory mapped registers without affecting the current

data page pointer value.

• In addition, you can modify any scratch pad RAM (DARAM

B2) location or data page 0.

• The memory-mapped register addressing mode operates like

the direct addressing mode, except that the 9 MSBs of the

address are forced to 0 instead of being loaded with the

contents of the DP.

• This allows you to address the memory-mapped registers of

data page 0 directly without the overhead of changing the DP

or auxiliary register.

2/21/2014 Abhishek KumarSrivastava 32

• Using these instructions does not affect the contents of

the DP:

LAMM — Load accumulator with memory-mapped

register

LMMR — Load memory-mapped register with the

contents of the data memory location addressed by the

16-bit source address, #addr.

SAMM — Store accumulator in memory-mapped register

SMMR — Store memory-mapped register with the

contents of the data memory location addressed by the

16-bit source address, #addr.

2/21/2014 Abhishek KumarSrivastava 33

PMST: A MMR that contains status and control bits.

2/21/2014 Abhishek KumarSrivastava 34

2/21/2014 Abhishek KumarSrivastava 35

Circular Addressing

• The ’C5x supports two concurrent circular buffers (for

algorithms such as convolution, correlation, and FIR filters)

operating via the ARs.

• The following five memory-mapped registers control the

circular buffer operation:

1. CBSR1 — Circular buffer 1 start register

2. CBSR2 — Circular buffer 2 start register

3. CBER1 — Circular buffer 1 end register

4. CBER2 — Circular buffer 2 end register

5. CBCR — Circular buffer control register

2/21/2014 Abhishek KumarSrivastava 36

2/21/2014 Abhishek KumarSrivastava 37

• The 8-bit CBCR enables and disables the circular buffer

operation.

• To define circular buffers, we first load the start and end

addresses into the corresponding buffer registers; next, load a

value between the start and end registers for the circular buffer

into an AR.

• Load the proper AR value, and set the corresponding circular

buffer enable bit in the CBCR.

• If (ARn = CBER) and (any AR modification),

Then: ARn = CBSR.

Else: ARn = ARn + step.

• Circular buffers can be used in increment- or decrement-type

updates.

2/21/2014 Abhishek KumarSrivastava 38

Modify AR

Store long immediate in data memory location

Load AR

Load ACC with content available at

address held in AR6

Add short immediate to AR

2/21/2014 Abhishek KumarSrivastava 39

Thank you for listening !

2/21/2014 Abhishek KumarSrivastava 40

You might also like

- Microcontroller MCQ QuizDocument5 pagesMicrocontroller MCQ QuizDeepika SharmaNo ratings yet

- Pic Microcontroller - Class NotesDocument26 pagesPic Microcontroller - Class NotesNarasimha Murthy Yayavaram80% (25)

- ARM Notes For StudentsDocument24 pagesARM Notes For StudentsAkshit Sharma100% (1)

- Unit-4 Arm ArchitectureDocument71 pagesUnit-4 Arm ArchitectureChandu81870gmail.com KayithiNo ratings yet

- CAO AssignmentDocument44 pagesCAO AssignmentAbhishek Dixit40% (5)

- Roof Truss Design ProcedureDocument17 pagesRoof Truss Design ProcedureHasib Ahsan94% (16)

- Machine DesignDocument45 pagesMachine DesignSean Ackerman78% (9)

- Approach To ScienceDocument106 pagesApproach To Sciencemuon_kNo ratings yet

- Mylecture TMS320C5x ArchitectureDocument63 pagesMylecture TMS320C5x ArchitectureGurjeet Singh67% (3)

- Architecture of TMS320C54XX Digital Signal ProcessorsDocument20 pagesArchitecture of TMS320C54XX Digital Signal ProcessorsLydia Elezabeth Alappat100% (8)

- 8086 Interrupts and Interrupt ResponsesDocument8 pages8086 Interrupts and Interrupt ResponsesNiharika Korukonda100% (1)

- UNIT-V-TMS320C54x-DSP ProcessorDocument47 pagesUNIT-V-TMS320C54x-DSP ProcessorVasant DivekarNo ratings yet

- Software and Hardware Interrupt ApplicationsDocument10 pagesSoftware and Hardware Interrupt Applicationssatyanarayana12No ratings yet

- Capgemini Technical Topicwise SortedDocument21 pagesCapgemini Technical Topicwise SortedmmjNo ratings yet

- Features of Lpc2148.Document9 pagesFeatures of Lpc2148.Sampathhhhh Sai Tadepalli86% (7)

- D - Jayakumar Ece Ece Ece Viva Questions-JkDocument20 pagesD - Jayakumar Ece Ece Ece Viva Questions-Jktinku990056% (9)

- Dynamic Ram Interfacing NotesDocument3 pagesDynamic Ram Interfacing NotesrneevanNo ratings yet

- Question With Answer MP & MCDocument13 pagesQuestion With Answer MP & MCMATHANKUMAR.SNo ratings yet

- CHAPTER 5: ADC, DAC Interfacing With 8086 and Its ApplicationDocument10 pagesCHAPTER 5: ADC, DAC Interfacing With 8086 and Its ApplicationAnikhet Mulky100% (1)

- Interfacing of 16x2 LCD With 8051 MicrocontrollerDocument7 pagesInterfacing of 16x2 LCD With 8051 MicrocontrollerVinothkumar Uruman100% (1)

- Introduction To 8051 ProgrammingDocument24 pagesIntroduction To 8051 Programmingveeramaniks408No ratings yet

- Unit V Finite Word Length Effects in Digital FiltersDocument3 pagesUnit V Finite Word Length Effects in Digital Filterstamizhanps67% (3)

- LDICA Digital NotesDocument263 pagesLDICA Digital NotesAbhishek Reddy Garlapati80% (5)

- Dec Lab QuestionsDocument25 pagesDec Lab QuestionsPrathiksha Harish Medical Electronics Engineering100% (1)

- Introduction To The Tmslf2407 DSP Controller: By: Dr. Dheeraj Joshi Associate ProfessorDocument17 pagesIntroduction To The Tmslf2407 DSP Controller: By: Dr. Dheeraj Joshi Associate ProfessorSameer SharmaNo ratings yet

- Features of The LPC214X FamilyDocument13 pagesFeatures of The LPC214X FamilyramyaNo ratings yet

- Communication Lab Manual GitamDocument35 pagesCommunication Lab Manual Gitamଦେବୀ ପ୍ରସାଦ ପଟନାୟକNo ratings yet

- DSP Important Viva QuestionsDocument3 pagesDSP Important Viva QuestionsDeepak Sahu100% (2)

- Directives of 8051Document8 pagesDirectives of 8051Piyush chaudhariNo ratings yet

- DSP C16 - UNIT-6 (Ref-2)Document26 pagesDSP C16 - UNIT-6 (Ref-2)Vaishnavi. KoyaNo ratings yet

- Arm 7 ArchitectureDocument22 pagesArm 7 ArchitectureNarasimha Murthy YayavaramNo ratings yet

- Viva Questions For Advanced Communication LabDocument4 pagesViva Questions For Advanced Communication Labanittadevadas57% (7)

- Interfacing Stepper Motor With 8085Document9 pagesInterfacing Stepper Motor With 8085Ranjith Kasu100% (2)

- Question Bank-Microprocessor and ApplicaionDocument38 pagesQuestion Bank-Microprocessor and Applicaionchandrasekar100% (5)

- 8096 Microcontrollers NotesDocument9 pages8096 Microcontrollers NotesNarasimha Murthy YayavaramNo ratings yet

- MPMC Lab Manual - For 20-21 - FinalDocument34 pagesMPMC Lab Manual - For 20-21 - Finalchandra kiran100% (1)

- 8051 Oscillator CKT Diagram and DescriptionDocument3 pages8051 Oscillator CKT Diagram and DescriptionVipul Badge100% (1)

- Digital Electronics Interview Questions: 1) What Is The Difference Between Latch and Flip-Flop?Document11 pagesDigital Electronics Interview Questions: 1) What Is The Difference Between Latch and Flip-Flop?yashuNo ratings yet

- MPMC 2marks (Unit 1 To 5) (Q & A)Document32 pagesMPMC 2marks (Unit 1 To 5) (Q & A)Ganapathy Ramadoss100% (2)

- 04 - Generation of Control Signals & Address DecodingDocument20 pages04 - Generation of Control Signals & Address DecodingOFFICIAL BUVAPADA0% (1)

- Memory Interfacing With 8086Document14 pagesMemory Interfacing With 8086Anuj Kumar52% (21)

- Address Decoding TechniqueDocument8 pagesAddress Decoding TechniqueYash SarohaNo ratings yet

- ANALOG AND DIGITAL IC Short Question With AnswerDocument46 pagesANALOG AND DIGITAL IC Short Question With AnswerMATHANKUMAR.S100% (2)

- TMS3205Cx DSP ProcessorDocument30 pagesTMS3205Cx DSP ProcessorJohn cena75% (4)

- DSP Hardware: EKT353 Lecture Notes by Professor Dr. Farid GhaniDocument44 pagesDSP Hardware: EKT353 Lecture Notes by Professor Dr. Farid GhanifisriiNo ratings yet

- Binomial Array: Department of Electronics and Communication EngineeringDocument6 pagesBinomial Array: Department of Electronics and Communication EngineeringKavitha A K100% (1)

- Interrupts in DSPDocument2 pagesInterrupts in DSPGouse ModeenNo ratings yet

- Samples of MCQ ARM PDFDocument4 pagesSamples of MCQ ARM PDFKomal50% (2)

- TMS320C54xx Instruction SetDocument338 pagesTMS320C54xx Instruction SetPreetham SaigalNo ratings yet

- Memory Interfacing: Example: Interface 4KB Memory To 8085 With Starting Address A000HDocument5 pagesMemory Interfacing: Example: Interface 4KB Memory To 8085 With Starting Address A000HSreepadam Padam100% (1)

- EC8661 VLSI Design LaboratoryDocument53 pagesEC8661 VLSI Design LaboratorySriram100% (4)

- Architecture of Tms320c5xDocument32 pagesArchitecture of Tms320c5xUjwal Patil100% (1)

- PIC QuestionsDocument4 pagesPIC Questionsgopikrishnarao100% (1)

- Microprocessor & Microcontroller Objective Type QuestionsDocument2 pagesMicroprocessor & Microcontroller Objective Type Questionsgokulchandru100% (2)

- 16 Bit Multiplication 8051Document4 pages16 Bit Multiplication 8051Uday A Korat100% (5)

- Microcontroller Lab Viva Questions & AnswersDocument29 pagesMicrocontroller Lab Viva Questions & AnswersAmbika Narayan75% (16)

- Tms320c5x AssemblyDocument38 pagesTms320c5x AssemblyB11 Aswathy SureshNo ratings yet

- Unit 5 PDFDocument21 pagesUnit 5 PDFShifanilaNo ratings yet

- Guide To Assembly Code-TMS320C5xDocument314 pagesGuide To Assembly Code-TMS320C5xSivaranjan Goswami0% (1)

- Machine Dependent Assembler FeaturesDocument26 pagesMachine Dependent Assembler FeaturesRAJARAMNo ratings yet

- Various Type of Addressing ModeDocument3 pagesVarious Type of Addressing ModeRajalakshmi PNo ratings yet

- Digital Signal Processing AdvancedDocument14 pagesDigital Signal Processing AdvancedMathi YuvarajanNo ratings yet

- Addressing Modes in Computer OrganizationDocument8 pagesAddressing Modes in Computer OrganizationArchana R gopinathNo ratings yet

- C Manual PDFDocument86 pagesC Manual PDFHimanshu ReddipalliNo ratings yet

- SQLMAPDocument5 pagesSQLMAPQuratulain TariqNo ratings yet

- © 2014 Pearson Education, IncDocument54 pages© 2014 Pearson Education, IncIbrahim MNo ratings yet

- Hamm 311 NO PRINTDocument7 pagesHamm 311 NO PRINTyanwu shang100% (1)

- Spin The DialDocument1 pageSpin The DialrobinlpaulNo ratings yet

- Fina Points Calculator 2008 v2.0Document12 pagesFina Points Calculator 2008 v2.0Nenad BoskovicNo ratings yet

- Sensors FundamentalDocument2 pagesSensors Fundamentalvenktesh22No ratings yet

- MDiesel Marine2010Document20 pagesMDiesel Marine2010youngfpNo ratings yet

- Projectile Motion Formula - Formula For Projectile Motion - Formulas@TutorVista PDFDocument3 pagesProjectile Motion Formula - Formula For Projectile Motion - Formulas@TutorVista PDFserkansancak100% (2)

- Ficha Técnica de Inversor SOLISDocument2 pagesFicha Técnica de Inversor SOLISJohnny Alberto GaleanoNo ratings yet

- Lab09 ExceptionDocument2 pagesLab09 ExceptionHồ NamNo ratings yet

- ACS - Danaher MotionDocument2 pagesACS - Danaher MotionMamadou Djibril BaNo ratings yet

- Mec 424 - Laboratory Report: Faculty of Mechanical EngineeringDocument24 pagesMec 424 - Laboratory Report: Faculty of Mechanical EngineeringAli HashemiNo ratings yet

- Paper 2 Mock MarkschemeDocument19 pagesPaper 2 Mock MarkschemeToviel KiokoNo ratings yet

- LTN101NT06-001 DisplayDocument32 pagesLTN101NT06-001 Displayluis felipezNo ratings yet

- TM31 ServicemanualDocument48 pagesTM31 ServicemanualVic3501No ratings yet

- Supor Operation Manual Suporssv1 1b E 131207Document163 pagesSupor Operation Manual Suporssv1 1b E 131207raschid alberto palacios lopezNo ratings yet

- Lecture2 Chapter6 - An Introduction To CountersDocument17 pagesLecture2 Chapter6 - An Introduction To CountersMuhammad Hassan JavedNo ratings yet

- Bar ScheduleDocument15 pagesBar ScheduleABAMELANo ratings yet

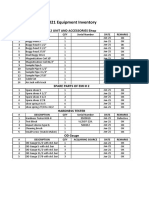

- 2021 Equipment Inventory: Emi 2 Unit and Accessories EitopDocument1 page2021 Equipment Inventory: Emi 2 Unit and Accessories Eitoptafani electricalNo ratings yet

- Pegylation of Phenothiazine - A Synthetic Route Towards Potent Anticancer DrugsDocument12 pagesPegylation of Phenothiazine - A Synthetic Route Towards Potent Anticancer DrugsIndriani BaharuddinNo ratings yet

- TPR 3º 2015-16 Donostiarra Examen 1A 1 Evaluación - EnglishDocument4 pagesTPR 3º 2015-16 Donostiarra Examen 1A 1 Evaluación - EnglishnachoyosNo ratings yet

- Research Paper ThesisDocument9 pagesResearch Paper Thesisrojthp9761100% (2)

- ENVI MET HP Software Features EnglischDocument1 pageENVI MET HP Software Features EnglischCarolina MacielNo ratings yet

- L2 DROID Turbo 2-Moto X Force Global Service and Repair Manual V3.0Document135 pagesL2 DROID Turbo 2-Moto X Force Global Service and Repair Manual V3.0diego_vrNo ratings yet

- Prayer For Research SubjectDocument18 pagesPrayer For Research SubjectKaila StefanieNo ratings yet

- 4 Trigonometric Transformation Trigonometric Substitution and RationalizingDocument10 pages4 Trigonometric Transformation Trigonometric Substitution and RationalizingTreesya EstradaNo ratings yet