Professional Documents

Culture Documents

Flip-Flop Reset

Flip-Flop Reset

Uploaded by

Diego Javier Cohecha León Sena0 ratings0% found this document useful (0 votes)

5 views1 pageThis VHDL code describes a D flip-flop circuit that uses a clock signal to synchronize the output to either mirror the input or reset to 0 depending on the state of the reset signal on each clock edge. The output is assigned the input value if reset is not active, or 0 if reset is active, triggered by a rising edge on the clock.

Original Description:

Original Title

Flip-Flop Reset.docx

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis VHDL code describes a D flip-flop circuit that uses a clock signal to synchronize the output to either mirror the input or reset to 0 depending on the state of the reset signal on each clock edge. The output is assigned the input value if reset is not active, or 0 if reset is active, triggered by a rising edge on the clock.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

5 views1 pageFlip-Flop Reset

Flip-Flop Reset

Uploaded by

Diego Javier Cohecha León SenaThis VHDL code describes a D flip-flop circuit that uses a clock signal to synchronize the output to either mirror the input or reset to 0 depending on the state of the reset signal on each clock edge. The output is assigned the input value if reset is not active, or 0 if reset is active, triggered by a rising edge on the clock.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 1

process (<clock>)

begin

if <clock>'event and <clock>='1' then

if <reset>='1' then

<output> <= '0';

else

<output> <= <input>;

end if;

end if;

end process;

You might also like

- Computer Engineering Drafting and Design: Control Unit: Hardwired Control ImplementationDocument7 pagesComputer Engineering Drafting and Design: Control Unit: Hardwired Control ImplementationRosendo CoquillaNo ratings yet

- VHDL LAB 10 FSM Code Solution and Test BenchDocument11 pagesVHDL LAB 10 FSM Code Solution and Test BenchHasanNo ratings yet

- VHDL Coding Syntax PDFDocument36 pagesVHDL Coding Syntax PDFA B ShindeNo ratings yet

- RR Prog 7Document4 pagesRR Prog 7Prashanth gowda A SNo ratings yet

- VLSI CodeDocument20 pagesVLSI CodeOm BhandareNo ratings yet

- Alarm ClockDocument4 pagesAlarm ClockAnisa FathimaNo ratings yet

- VHDL Interface ProgramsDocument17 pagesVHDL Interface ProgramssshhazNo ratings yet

- VHDL Code For A D Flip FlopDocument9 pagesVHDL Code For A D Flip FlopYogesh KhollamNo ratings yet

- Configuration Des Blocs de PIC10F200Document4 pagesConfiguration Des Blocs de PIC10F200MERIEM BEN HASSENNo ratings yet

- Library IEEEDocument3 pagesLibrary IEEEnumer_nine99No ratings yet

- VHDL Code For A D Flip FlopDocument5 pagesVHDL Code For A D Flip Flopashok_larkha4334No ratings yet

- 10100Document7 pages10100Đạt NguyễnNo ratings yet

- Divisor de Frecuencia de 50 MHZ A 10 HZDocument8 pagesDivisor de Frecuencia de 50 MHZ A 10 HZAlexis Espinoza HilarioNo ratings yet

- Diseño Digital ProblemasDocument36 pagesDiseño Digital ProblemasRenato ValverdeNo ratings yet

- Program-2: Suresh Prashad CS-3B UpadhyayDocument2 pagesProgram-2: Suresh Prashad CS-3B UpadhyayamazonNo ratings yet

- Scheduling Algorithms Implementation Lab Assignment # 2: Operating SystemsDocument12 pagesScheduling Algorithms Implementation Lab Assignment # 2: Operating SystemsIzzaTipuNo ratings yet

- Operating System Lab TaskDocument13 pagesOperating System Lab TaskSaad AfridiNo ratings yet

- ContasDocument3 pagesContasEduardo HenriqueNo ratings yet

- LAB - 2 (Fork) - CodeDocument2 pagesLAB - 2 (Fork) - Codeitspk007pkNo ratings yet

- C Code ClockDocument14 pagesC Code ClockMiltonNo ratings yet

- Experiment No - 14: Objective - To Implement 11011 Nonoverlapping Mealy Sequence DetectorDocument7 pagesExperiment No - 14: Objective - To Implement 11011 Nonoverlapping Mealy Sequence DetectorRanveerNo ratings yet

- Exemple - Code VHDLDocument4 pagesExemple - Code VHDLSaid EL AissaouyNo ratings yet

- Registro de Corrimiento de 4 Bits: Códigos UtilizadosDocument6 pagesRegistro de Corrimiento de 4 Bits: Códigos UtilizadosLuis FernandoNo ratings yet

- Códigos ElevadorDocument13 pagesCódigos ElevadorisaNo ratings yet

- Sipo VHDL CodeDocument5 pagesSipo VHDL CodeManohar thotaNo ratings yet

- Exp4 Counter - OdtDocument4 pagesExp4 Counter - OdtDaniel GabrielNo ratings yet

- Họ và tên: Lê Hồng Phú MSSV: 41801040 Bài tập 6 - buổi học 20211030Document8 pagesHọ và tên: Lê Hồng Phú MSSV: 41801040 Bài tập 6 - buổi học 20211030Hồng PhúNo ratings yet

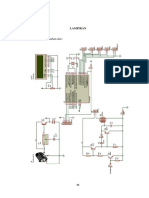

- Rangkaian Keseluruhan Alat:: LampiranDocument7 pagesRangkaian Keseluruhan Alat:: LampiranAdink M AlwiNo ratings yet

- Os Week-1Document6 pagesOs Week-1sadi dileepkumarNo ratings yet

- Problema 1 "Lavadora" Código VHDL ModuleDocument40 pagesProblema 1 "Lavadora" Código VHDL ModuleLeonardoNo ratings yet

- Digital System Design Example 1: GCD Calculator: Start Signal, Which Commences The Computation ProcessDocument31 pagesDigital System Design Example 1: GCD Calculator: Start Signal, Which Commences The Computation ProcessEMJAYNo ratings yet

- Ieee Ieee STD - LOGIC - 1164: Library Use ALLDocument3 pagesIeee Ieee STD - LOGIC - 1164: Library Use ALLAnonymous L9Fnfx7acNo ratings yet

- Compte Rendu: Réaliser ParDocument8 pagesCompte Rendu: Réaliser ParRami NsirNo ratings yet

- Process Statements - Wait Statements - Variable and Signal Assignments - If and Case Statements - Loop Statements - While StatementsDocument29 pagesProcess Statements - Wait Statements - Variable and Signal Assignments - If and Case Statements - Loop Statements - While StatementsQasimNo ratings yet

- DSD Lab3 Fa20-Bce-029 PDFDocument5 pagesDSD Lab3 Fa20-Bce-029 PDFabdullahNo ratings yet

- Divisor de Frecuencia de 50MHz A 1Hz para Parpadeo de LEDDocument2 pagesDivisor de Frecuencia de 50MHz A 1Hz para Parpadeo de LEDepievegaNo ratings yet

- Digital Design 2 Lab: An-Najah UniversityDocument17 pagesDigital Design 2 Lab: An-Najah UniversitySudqi JawabrehNo ratings yet

- Shift Register: CodeDocument3 pagesShift Register: Code1432badassNo ratings yet

- OS Lab Programs ExercisesDocument5 pagesOS Lab Programs ExercisesljjbNo ratings yet

- Resolución Del Examen Parcial: Diseño DigitalDocument5 pagesResolución Del Examen Parcial: Diseño DigitalJorge ZambranoNo ratings yet

- TUGAS 3 & 4 FPGA - Serly YulianaDocument9 pagesTUGAS 3 & 4 FPGA - Serly YulianaSerly YulianaNo ratings yet

- VHDL Interfacing ProgramsDocument22 pagesVHDL Interfacing ProgramsNithish ManjuNo ratings yet

- StageDocument5 pagesStagekokotskurveny185No ratings yet

- FPGA ExamplesDocument3 pagesFPGA Examplespraful_kohale6642No ratings yet

- BT3 TuvietDocument2 pagesBT3 TuvietChúc Văn KiênNo ratings yet

- Slic ProcesorDocument4 pagesSlic ProcesorgpuonlineNo ratings yet

- CHPT 3Document175 pagesCHPT 3tjdandin1No ratings yet

- HDL InterfacingDocument8 pagesHDL InterfacingshastryNo ratings yet

- Ejemplos VHDLDocument5 pagesEjemplos VHDLLeón Emmanuel NNo ratings yet

- PDF Primary-Whatsapp-Media-Whatsapp-Documents-VlsilabquestDocument17 pagesPDF Primary-Whatsapp-Media-Whatsapp-Documents-VlsilabquestSanju SraNo ratings yet

- Thi Nghiem Ky Thuat So Bao Cao Thi Nghiem Kts (2.1 2.5) (Cuuduongthancong - Com)Document12 pagesThi Nghiem Ky Thuat So Bao Cao Thi Nghiem Kts (2.1 2.5) (Cuuduongthancong - Com)Ha VuNo ratings yet

- Diseño ImprimirDocument4 pagesDiseño ImprimirRenato ValverdeNo ratings yet

- Peg Puzzle - JavaDocument10 pagesPeg Puzzle - JavaKsheerod ToshniwalNo ratings yet

- OS Lab-3 - 19JE0425 - KartikekishoreDocument13 pagesOS Lab-3 - 19JE0425 - KartikekishoreUtkarsh TiwariNo ratings yet

- Verilog Code For CLKDocument2 pagesVerilog Code For CLKSHREENo ratings yet

- VHDL Project: Title: "Stop Watch"Document13 pagesVHDL Project: Title: "Stop Watch"Soriya HiteshNo ratings yet

- 1.Thiết kế bộ đếm lùi thập phânDocument10 pages1.Thiết kế bộ đếm lùi thập phânTuấn AnhNo ratings yet

- Circular DevDocument4 pagesCircular DevAryaraj SinghNo ratings yet