Professional Documents

Culture Documents

Lab Assignment 1

Uploaded by

Ishrak MahmudOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lab Assignment 1

Uploaded by

Ishrak MahmudCopyright:

Available Formats

Islamic University of Technology

Department of Electrical and Electronic Engineering (EEE)

Embedded Systems Design Lab.(EEE 4766)

VHDL Examples and Exercises

Necessary concepts which will be required to perform the examples and exercises:

Signal(s) are like physical wires.

std_logic_vector is just a vector (or, array/collection) of std_logic elements.

others => '0' is used to set/initialize all the elements of an array to '0'

clk'event and clk = '1' is used to indicate the rising edge of the clock signal.

There is an alternative statement

if (rising_edge = clk) then

…

…

X"000000" refers to hexadecimal in VHDL and that consists of 24 bits.

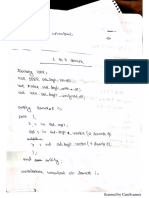

Example-1

4 to 1 Multiplexer:

Figure 1. 4 to 1 Multiplexer

Prepared by: Safayat Bin Hakim, Department of EEE, IUT

Source code:

library ieee;

use ieee.std_logic_1164.all;

entity mux4_to_1 is

port (

I0 : in std_logic;

I1 : in std_logic;

I2 : in std_logic;

I3 : in std_logic;

sel : in std_logic_vector (1 downto 0);

output : out std_logic

);

end entity;

architecture behavioral of mux4_to_1 is

begin

process(sel) -- process and sensitivity list

begin

case sel is

when "00" => output <= I0;

when "01" => output <= I1;

when "10" => output <= I2;

when others => output <= I3;

end case;

end process;

end architecture behavioral;

Test-bench code:

library ieee;

use ieee.std_logic_1164.all;

entity tb_mux4_to_1 is

end tb_mux4_to_1;

architecture behavioral of tb_mux4_to_1 is

component mux4_to_1

port (

I0 : in std_logic;

I1 : in std_logic;

I2 : in std_logic;

I3 : in std_logic;

sel : in std_logic_vector (1 downto 0);

output : out std_logic

);

end component;

signal tb_I0, tb_I1, tb_I2, tb_I3 : std_logic := '0';

signal tb_sel : std_logic_vector (1 downto 0) := (others => '0');

Prepared by: Safayat Bin Hakim, Department of EEE, IUT

signal tb_output : std_logic;

begin

uut: mux4_to_1 port map (

I0 => tb_I0,

I1 => tb_I1,

I2 => tb_I2,

I3 => tb_I3,

sel => tb_sel,

output => tb_output

);

-- stimulus process

stim_process: process

begin

wait for 50 ns;

tb_sel <= "00";

tb_I0 <= '1'; tb_I1 <= '0'; tb_I2 <= '1'; tb_I3 <= '1';

wait for 50 ns;

tb_sel <= "01";

wait for 50 ns;

tb_sel <= "10";

wait for 50 ns;

tb_sel <= "11";

wait for 50 ns;

tb_I0 <= '0'; tb_I1 <= '1'; tb_I2 <= '0'; tb_I3 <= '0';

tb_sel <= "11";

wait for 50 ns;

end process;

end architecture behavioral;

Figure 2. Simulation result (timing diagram) of the multiplexer testbench

Prepared by: Safayat Bin Hakim, Department of EEE, IUT

Example-2

D Flip-Flop:

In general, we define a synchronous sequential circuit, or just sequential circuit as a circuit with m inputs,

n outputs, and a distinguished clock input.

Figure 3. D Flip-Flop

Source code:

library ieee;

use ieee.std_logic_1164.all;

entity d_flipflop is

port (

clk : in std_logic;

D : in std_logic;

Q : out std_logic

);

end entity;

architecture behavioral of d_flipflop is

begin

process (clk, D)

begin

if (clk'event and clk = '1') then

Q <= D;

end if;

end process;

end architecture behavioral;

Test-bench code:

library ieee;

use ieee.std_logic_1164.all;

entity tb_d_flipflop is

end tb_d_flipflop;

architecture behavioral of tb_d_flipflop is

component d_flipflop

port (

Prepared by: Safayat Bin Hakim, Department of EEE, IUT

clk : in std_logic;

D : in std_logic;

Q : out std_logic

);

end component;

signal clk : std_logic;

signal tb_D : std_logic;

signal tb_Q : std_logic;

constant clk_period : time := 100 ns; -- period of the clock

begin

uut: d_flipflop port map(

clk => clk,

D => tb_D,

Q => tb_Q

);

-- clock process

clk_process: process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

-- stimulus process

stim_process: process

begin

wait for 50 ns;

tb_D <= '0';

wait for 50 ns;

tb_D <= '1';

wait for 50 ns;

tb_D <= '0';

end process;

end architecture behavioral;

Figure 4. Simulation result (timing diagram) of the D-flipflop testbench

Prepared by: Safayat Bin Hakim, Department of EEE, IUT

Example-3

A binary encoder has 2n input lines and n output lines, hence it encodes the information from 2n inputs into

an n-bit code. From all the input lines, only one of an input line is activated at a time, and depending on the

input line, it produces the n bit output code.

Depending on the number of input lines, digital or binary encoders produce the output codes in the form of

2 or 3 or 4 bit codes.

(a)

Input Output

A[3] A[2] A[1] A[0] B[1] B[0]

0 0 0 1 0 0

0 0 1 0 0 1

0 1 0 0 1 0

1 0 0 0 1 1

(b)

Figure 5. 4 to 2 Encoder (a) Block Diagram (b) Truth Table

Source code:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity encoder is

port(

A: in STD_LOGIC_VECTOR(3 downto 0);

B: out STD_LOGIC_VECTOR(1 downto 0)

);

end encoder;

architecture behavioral of encoder is

begin

process(a)

begin

if (A = "1000") then

B <= "00";

elsif (A = "0100") then

B <= "01";

elsif (A = "0010") then

Prepared by: Safayat Bin Hakim, Department of EEE, IUT

B <= "10";

elsif (A = "0001") then

B <= "11";

else

B <= "ZZ";

end if;

end process;

end architecture behavioral;

Test-bench code:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY tb_encoder IS

END tb_encoder;

ARCHITECTURE behavioral OF tb_encoder IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT encoder

PORT(

A : IN std_logic_vector(3 downto 0);

B : OUT std_logic_vector(1 downto 0)

);

END COMPONENT;

--Inputs

signal tb_A : std_logic_vector(3 downto 0) := (others => '0');

--Outputs

signal tb_B : std_logic_vector(1 downto 0);

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: encoder PORT MAP (

A => tb_A,

B => tb_B

);

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

wait for 100 ns;

tb_A <= "0000";

wait for 100 ns;

tb_A <= "0001";

wait for 100 ns;

tb_A <= "0010";

wait for 100 ns;

tb_A <= "0100";

wait for 100 ns;

tb_A <= "1000";

wait;

end process;

END architecture behavioral;

Prepared by: Safayat Bin Hakim, Department of EEE, IUT

Figure 6. Simulation result (timing diagram) of the 4 to 2 Encoder testbench

Home tasks (Implement in VHDL. Compile and simulate with Modelsim)

1. Design a full-adder circuit. Then simulate and verify with testbench.

2. Design a 1 to 8 demultiplexer. Then simulate and verify with testbench.

3. Design a 4-bit Arithmetic Logic Unit (ALU) which can perform addition, subtraction, AND, OR operation

between two numbers. Try to simulate with testbench.

4. Design a synchronous 5-bit shift register (use a input clock for synchronization). Then simulate and verify

with testbench providing different combinations.

Prepared by: Safayat Bin Hakim, Department of EEE, IUT

You might also like

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- DC80D MK3 Genset Controller User Manual V1.1Document37 pagesDC80D MK3 Genset Controller User Manual V1.1nathalie gonzelez100% (1)

- VHDL ProgramsDocument49 pagesVHDL Programsapi-369623583% (12)

- VHDL ProgramDocument5 pagesVHDL ProgramJaswanth TejaNo ratings yet

- VHDL CodeDocument34 pagesVHDL CodeHimanshu Thakur100% (1)

- Exercices VHDLDocument83 pagesExercices VHDLFadi Akoury50% (2)

- Newton's Laws of MotionDocument21 pagesNewton's Laws of MotionharlequinlhaiNo ratings yet

- HDL Lab Manual For VTUDocument93 pagesHDL Lab Manual For VTULavanya Vaishnavi D.A.No ratings yet

- Python Programming for Beginners Crash Course with Hands-On Exercises, Including NumPy, Pandas and MatplotlibFrom EverandPython Programming for Beginners Crash Course with Hands-On Exercises, Including NumPy, Pandas and MatplotlibNo ratings yet

- VHDL Programs LabDocument20 pagesVHDL Programs LabVasu SiriNo ratings yet

- Lecture 11 Network DesignDocument132 pagesLecture 11 Network Designjon-jon anchetaNo ratings yet

- Singapore DTL Signalling by Joana Lee (Siemens Pte LTD) 18th Nov 2016Document23 pagesSingapore DTL Signalling by Joana Lee (Siemens Pte LTD) 18th Nov 2016Rizky Harry SungguhNo ratings yet

- ECE 742 - Digital System-on-Chip Design: Lab ReportDocument18 pagesECE 742 - Digital System-on-Chip Design: Lab ReportAishwarya JSNo ratings yet

- CA PracticalDocument11 pagesCA PracticalBidhan BaraiNo ratings yet

- Ec-452 VHDL CadDocument39 pagesEc-452 VHDL Cadkishorereddy416No ratings yet

- Micro TPDocument7 pagesMicro TPsebastienNo ratings yet

- Assignment 1Document74 pagesAssignment 1Rajesh PathakNo ratings yet

- Writing VHDL For RTL Synthesis: 1 StructureDocument9 pagesWriting VHDL For RTL Synthesis: 1 StructuremmalgiNo ratings yet

- Experiment No.1: A Binary To Gray ConverterDocument26 pagesExperiment No.1: A Binary To Gray ConverterVarun SharmaNo ratings yet

- Introduction To VHDLDocument35 pagesIntroduction To VHDLsudharsanNo ratings yet

- Praktikum Guruh DenyDocument19 pagesPraktikum Guruh DenyMuhammad Rifki AzizieNo ratings yet

- EXOR Gate Using Concurrent Statements: RTL ViewDocument59 pagesEXOR Gate Using Concurrent Statements: RTL ViewSurbhit SinhaNo ratings yet

- Programme No.10 AIM-To Design A D - Flip Flop CODE - Following Is The VHDL Code For Simulation of D Flip FlopDocument8 pagesProgramme No.10 AIM-To Design A D - Flip Flop CODE - Following Is The VHDL Code For Simulation of D Flip FlopAnkit GoelNo ratings yet

- Date: 28 September, 2015: VHDL Assighment 2Document15 pagesDate: 28 September, 2015: VHDL Assighment 2Ishan DarwhekarNo ratings yet

- Lab 01Document7 pagesLab 0121021326 Phùng Mạnh KhangNo ratings yet

- DICA Manual Cycle-2Document14 pagesDICA Manual Cycle-2Krishna BoreddyNo ratings yet

- Benr Benc4473 Digital Ic Design Lab1 - 2022Document5 pagesBenr Benc4473 Digital Ic Design Lab1 - 2022Maga LakshmiNo ratings yet

- Evl 104 Vlsi Design Lab-I: Ex - No:1 Modeling of Sequential Digital Systems Using VHDLDocument34 pagesEvl 104 Vlsi Design Lab-I: Ex - No:1 Modeling of Sequential Digital Systems Using VHDLvijithacvijayanNo ratings yet

- VHDL From BotrosDocument17 pagesVHDL From BotrossanjanaNo ratings yet

- Structural LabDocument69 pagesStructural LabNABIRASOOLNo ratings yet

- Islamic University of Technology: EEE 4483 Digital Electronics & Pulse TechniquesDocument14 pagesIslamic University of Technology: EEE 4483 Digital Electronics & Pulse TechniquesMUHAMMAD JAWAD CHOWDHURY, 180041228No ratings yet

- Microelectronic System Lab. 1 ReportDocument6 pagesMicroelectronic System Lab. 1 ReportNorma HermawanNo ratings yet

- VHDL Lab ProgramsDocument51 pagesVHDL Lab ProgramsvenkiNo ratings yet

- Experiment No:-1 (A) : AIM: - To Write A Program in VHDL To Implement XOR GateDocument41 pagesExperiment No:-1 (A) : AIM: - To Write A Program in VHDL To Implement XOR GateankitNo ratings yet

- VHDL Operators BasicsDocument0 pagesVHDL Operators BasicsjushwanthNo ratings yet

- Lab 6Document4 pagesLab 6marwa abdelrazikNo ratings yet

- Combinational Logic Circuits: Prof. David Márquez ViloriaDocument16 pagesCombinational Logic Circuits: Prof. David Márquez ViloriaJose Mateo Aristizabal DiazNo ratings yet

- Modeling Scheme.: Objective 1: VHDL Code For 2 Input XOR Gate Using BehavioralDocument24 pagesModeling Scheme.: Objective 1: VHDL Code For 2 Input XOR Gate Using BehavioralAmrinder SinghNo ratings yet

- Dic File - 7 SemDocument22 pagesDic File - 7 SemShalini SharmaNo ratings yet

- VHDL - Xilinx Exercises CompilationDocument19 pagesVHDL - Xilinx Exercises CompilationNicko CasiNo ratings yet

- Verilog HDL Code For Y A'B+C'D'Document48 pagesVerilog HDL Code For Y A'B+C'D'Goutham KrishNo ratings yet

- Practical File OF VHDL Based Design Lab (Ec - 252) Bachelor of TechnologyDocument32 pagesPractical File OF VHDL Based Design Lab (Ec - 252) Bachelor of TechnologyTarunNo ratings yet

- Engr2015 Lab2Document13 pagesEngr2015 Lab2SUPER AMAZINGNo ratings yet

- Experiment-1: Simulation Result For Half Adder and Full Adder CircuitDocument7 pagesExperiment-1: Simulation Result For Half Adder and Full Adder CircuitHimanshu Rajan jainNo ratings yet

- VHDL ReportDocument29 pagesVHDL ReportSalman AliNo ratings yet

- VHDL Lab FileDocument48 pagesVHDL Lab FileAnkit Gupta100% (1)

- Lab 1 ReportDocument7 pagesLab 1 ReportNguyễn ThắngNo ratings yet

- DSD Lab ManualDocument16 pagesDSD Lab ManualPreeti SinghNo ratings yet

- 4 Bit Counter With Test BenchDocument3 pages4 Bit Counter With Test BenchJaya Balakrishnan100% (1)

- Module Fsmmealy1011Document30 pagesModule Fsmmealy1011Devang JoshiNo ratings yet

- Reg. No: Name:: Q.No. Sub. Sec. Question Description MarksDocument2 pagesReg. No: Name:: Q.No. Sub. Sec. Question Description MarksWINORLOSENo ratings yet

- Verilog Sequential ModelingDocument8 pagesVerilog Sequential ModelingR INI BHANDARINo ratings yet

- Dante Experiment#2Document8 pagesDante Experiment#2CHRISTIANJOIE DANTENo ratings yet

- CENG355 Final Exam Spring2019 SolutionDocument13 pagesCENG355 Final Exam Spring2019 SolutionHadi SleemNo ratings yet

- HDL ProgramDocument6 pagesHDL ProgramChethan RaoNo ratings yet

- VHDL Cheat Sheet Exam 1Document3 pagesVHDL Cheat Sheet Exam 1Kevin Wilczak100% (1)

- 1) VHDL Code To Realize All The Logic Gates: Iv Semester HDL LabDocument45 pages1) VHDL Code To Realize All The Logic Gates: Iv Semester HDL LabPamidi VishnuNo ratings yet

- VHDLDocument13 pagesVHDLSrijeeta SenNo ratings yet

- Adsd Lab Experiments: NAME: Ankit Mukherjee REG NO: RA1911043040015 Class: Ece B'Document29 pagesAdsd Lab Experiments: NAME: Ankit Mukherjee REG NO: RA1911043040015 Class: Ece B'AnkitShubhoeMukherjeeNo ratings yet

- DSP Mid SolutionDocument25 pagesDSP Mid SolutionIshrak MahmudNo ratings yet

- Ayana Soln CH 06Document22 pagesAyana Soln CH 06Ishrak MahmudNo ratings yet

- Es Lab1Document10 pagesEs Lab1Ishrak MahmudNo ratings yet

- Ques SolveDocument5 pagesQues SolveIshrak MahmudNo ratings yet

- Lecture 1 IntroDocument21 pagesLecture 1 IntroAshraful Islam MridhaNo ratings yet

- Assignment EEE 4766 - Id - 160021056Document17 pagesAssignment EEE 4766 - Id - 160021056Ishrak MahmudNo ratings yet

- SMM200 Derivatives and Risk Management 2021 QuestionsDocument5 pagesSMM200 Derivatives and Risk Management 2021 Questionsminh daoNo ratings yet

- Rate LawsDocument20 pagesRate LawsReginal MoralesNo ratings yet

- Tutorial 6Document5 pagesTutorial 6Nixon GamingNo ratings yet

- RPI Form PDFDocument1 pageRPI Form PDFJoko WiwiNo ratings yet

- Bos 5.5.1 Installation Guide JbossDocument20 pagesBos 5.5.1 Installation Guide JbossklepssNo ratings yet

- Data Sartocon X-Cap15 SPC2065-eDocument2 pagesData Sartocon X-Cap15 SPC2065-eJosé Ramón Devan DevanNo ratings yet

- k215-165b (15amp Trip Sel CB)Document1 pagek215-165b (15amp Trip Sel CB)Claudio DiazNo ratings yet

- 3d Printing CEDocument11 pages3d Printing CEShivam SamaiyaNo ratings yet

- 001-03 - Hydraulic Charge Pressure Switch Shorted To High SourceDocument6 pages001-03 - Hydraulic Charge Pressure Switch Shorted To High Sourceكؤمپيوته رى ديارىNo ratings yet

- CTR Manufacturing Develops 2 Tap Changer Transformers With FR3 Fluid 1Document5 pagesCTR Manufacturing Develops 2 Tap Changer Transformers With FR3 Fluid 1SM KNo ratings yet

- Bioresource Technology: Oscar Pardo-Planas, Hasan K. Atiyeh, John R. Phillips, Clint P. Aichele, Sayeed MohammadDocument8 pagesBioresource Technology: Oscar Pardo-Planas, Hasan K. Atiyeh, John R. Phillips, Clint P. Aichele, Sayeed Mohammadmohsen ranjbarNo ratings yet

- Chapter 7Document23 pagesChapter 7enes_ersoy_3No ratings yet

- 빛공해 방지를 위한 조명기구 설치·관리 권고기준 가이드라인Document114 pages빛공해 방지를 위한 조명기구 설치·관리 권고기준 가이드라인ByungHoon JungNo ratings yet

- Pac3A Sect 600 EarthworksDocument66 pagesPac3A Sect 600 EarthworksazizuddinNo ratings yet

- Parts of An Automobile and The FunctionDocument11 pagesParts of An Automobile and The Functionrajronson6938100% (8)

- P-G-R-T / P-G-R-S Truck: Preventative Maintenance GuideDocument2 pagesP-G-R-T / P-G-R-S Truck: Preventative Maintenance GuideKANG PRIYONo ratings yet

- Test Section 2 QuizDocument5 pagesTest Section 2 QuizDavidNo ratings yet

- Inspection and Testing of OC/EF Protection Relay: Relay Site Test ReportDocument3 pagesInspection and Testing of OC/EF Protection Relay: Relay Site Test ReportMASUD RANANo ratings yet

- Chapter 6 2022Document7 pagesChapter 6 2022khursheed rasoolNo ratings yet

- Oscilloscope HM 1004-: Manual - Handbuch - ManuelDocument31 pagesOscilloscope HM 1004-: Manual - Handbuch - ManuelSanyel SaitoNo ratings yet

- Frequent Itemset MiningDocument58 pagesFrequent Itemset MiningMesut ErkekliNo ratings yet

- 10385-J UTBI-001 ManualDocument2 pages10385-J UTBI-001 ManualMatias GiammariniNo ratings yet

- 500m 360 Degree Rotary HD Borewell Camera Water Well Borehole Inspection Camera With 12 Inch Screen Electric WinchDocument10 pages500m 360 Degree Rotary HD Borewell Camera Water Well Borehole Inspection Camera With 12 Inch Screen Electric WinchCristopferENo ratings yet

- Experiment No.1 CalorimetryDocument6 pagesExperiment No.1 Calorimetrytintindlr100% (1)

- C ProgramsDocument16 pagesC Programsvaishuraji2001No ratings yet

- Capaciter Working PrincipalDocument2 pagesCapaciter Working PrincipalSanjivee SachinNo ratings yet