Professional Documents

Culture Documents

EEE 248 CNG 232: Logic

EEE 248 CNG 232: Logic

Uploaded by

ARSALANOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

EEE 248 CNG 232: Logic

EEE 248 CNG 232: Logic

Uploaded by

ARSALANCopyright:

Available Formats

ELECTRICAL AND ELECTRONICS ENGINEERING

&

COMPUTER ENGINEERING

EEE 248 CNG 232

Logic Design

Dr. Gürtaç Yemişçioğlu

FALL 2020

HW2

Number of Questions: 4

December 28, 2020

Good Luck

Student Number:

Full Name:

Question Achieved Points

1 24

2 36

3 20

4 20

Total 100

EEE 248 CNG 232

Logic Design

Fall 2020 - 2021 HW2 28 December 2020

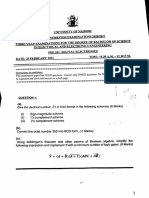

Question 1 (24 pts.):

a. (4 pts.) Determine the timing diagram shown below

i. (2 pts.) For output Q for gated S-R latch. Assume that Q is initially LOW.

ii. (2 pts.) Given a positive edge triggered JK flip-flops.

Dr. Gürtaç Yemişcioğlu Page| 2

EEE 248 CNG 232

Logic Design

Fall 2020 - 2021 HW2 28 December 2020

b. (20 pts) Analyse the circuit given below.

SET A

J Q

CLR

K Q

SET B

J Q

x

CLR

K Q

SET C

J Q

CLR

K Q

CLK

i. (8 pts.) Derive the next state equations for each flip-flop.

ii. (6 pts.) Tabulate the state table.

iii. (6 pts.) Draw the corresponding state diagram.

Dr. Gürtaç Yemişcioğlu Page| 3

EEE 248 CNG 232

Logic Design

Fall 2020 - 2021 HW2 28 December 2020

Question 2 (36 pts.):

a. (6 pts) Determine the functional behaviour of the circuit shown below. Assume that

input w is driven by a square wave signal.

b. (30 pts.) The state diagram of a synchronous sequential circuit is shown below.

00/0 1

0

0

1

11/1 01/1

1

0

0

10/0

a. (2 pts.) Is this a Mealy or Moore model, Why?

b. (4 pts.) Starting from state 00 determine state transitions and output sequence

that will be generated when an input sequence of 001001001110000 is

applied.

c. (12 pts.) Design a sequential circuit using T flip-flops.

d. (12 pts.) Design a sequential circuit using JK-flip-flops. For J-K implementation,

J-K inputs must be determined by tabulating a new state table.

Dr. Gürtaç Yemişcioğlu Page| 4

EEE 248 CNG 232

Logic Design

Fall 2020 - 2021 HW2 28 December 2020

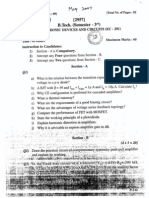

Question 3 (20 pts.):

a. (6 pts) The contents of a four-bit register is initially 1001. The register is shifted 10

cycles to the right with the serial input being 1100101001. What is the content of

the register after each shift?

b. (6 pts) The serial adder shown below uses two four-bit registers. Register A holds

the binary number 0011 and register B holds 1000. The carry flip-flop is initially

reset to 0. List the binary values in register A and the carry flip-flop after each shift.

Cycle no. regA regB x y J K carry sum

1

2

3

4

5

c. (8 pts) We build a new type of flip-flop as shown below.

A

B

S ET

D Q Qo

CLK

C LR

Q

ii. (4 pts.) Write the characteristic equation of this flip-flop.

iii. (4 pts.) Given the following waveforms for A, B and CLK (rising edge activated),

draw the waveform for Qo.

1

CLK

0

1

A

0

1

B

0

1

Q0

0

Dr. Gürtaç Yemişcioğlu Page| 5

EEE 248 CNG 232

Logic Design

Fall 2020 - 2021 HW2 28 December 2020

Question 4 (20 pts.): The data path is given for a 4-bit multiplier. It consists of a 4-bit adder,

a 4-bit register, and a 9-bit shift register. The latter shifts right when its Sh input is

asserted (assume that 0's are entered at the left for this operation). A new value is loaded

into the high-order 5 bits of the shift register when Ld is asserted. The same 5 bits are

zeroed when Cl is asserted These signals are synchronous. Design the control for a

sequential 4-bit multiplier.

4-bit

Multiplier

Sh

M

Ld

Cl

Shift

4-bit right

Multiplicand

Control S

Unit

4

Sh

Ld

Cl

Carry Out

+

a. (10 pts.) Sketch a complete state diagram for the operation of the Control Unit.

b. (10 pts.) Sketch a logic implementation of the Control Unit using D-type flip-flops

and logic gates of your choice using one-hot state assignment. You do not have to

show the transition/state tables.

Dr. Gürtaç Yemişcioğlu Page| 6

You might also like

- JavaScript Interview Questions and Answers PDF - CodeProjectDocument8 pagesJavaScript Interview Questions and Answers PDF - CodeProjectJagdish TripathiNo ratings yet

- Main Components of A GeneratorDocument7 pagesMain Components of A GeneratoradhyarthaNo ratings yet

- OL Sets and ComputationDocument419 pagesOL Sets and ComputationSérgio MirandaNo ratings yet

- PDF Learning SQL Master SQL Fundamentals Alan Beaulieu Ebook Full ChapterDocument53 pagesPDF Learning SQL Master SQL Fundamentals Alan Beaulieu Ebook Full Chapterlester.jarvis649100% (1)

- How To Use Google Apps Script To Store Price Data in Google SheetsDocument2 pagesHow To Use Google Apps Script To Store Price Data in Google SheetsJames ZhanNo ratings yet

- Galant ECU PinOutDocument1 pageGalant ECU PinOuthakyNo ratings yet

- CounterDocument33 pagesCounterAMIT KUMAR SINGHNo ratings yet

- Stat Q3 WK5 Las1Document1 pageStat Q3 WK5 Las1Gladzangel LoricabvNo ratings yet

- Combinatorial Algorithms: For Computers and CalculatorsFrom EverandCombinatorial Algorithms: For Computers and CalculatorsRating: 4 out of 5 stars4/5 (2)

- Xiaomi Mi Notebook Pro 15 Enchanced Edition Inventec A10 R15 6050A2940901Document72 pagesXiaomi Mi Notebook Pro 15 Enchanced Edition Inventec A10 R15 6050A2940901Delwar HossainNo ratings yet

- HW3 Fall2020Document6 pagesHW3 Fall2020ARSALANNo ratings yet

- ECE2030A Fall 2008 Introduction To Computer Engineering Exam #3Document8 pagesECE2030A Fall 2008 Introduction To Computer Engineering Exam #3salNo ratings yet

- Solution PDFDocument5 pagesSolution PDFCedric SunNo ratings yet

- Unit 5 (Tutorials) - Sequential Logic Circuits 1Document2 pagesUnit 5 (Tutorials) - Sequential Logic Circuits 1Wan AleeyaNo ratings yet

- Question Bank 3 Sem Digital System Design 2 Internals.: RD NDDocument2 pagesQuestion Bank 3 Sem Digital System Design 2 Internals.: RD NDDeepa JerinNo ratings yet

- COE/EE 243 Sample Exam #4 SolutionDocument4 pagesCOE/EE 243 Sample Exam #4 SolutionM Naveed ShakirNo ratings yet

- CS 2202 - Digital Principles and Systems DesignDocument3 pagesCS 2202 - Digital Principles and Systems DesignDhilip PrabakaranNo ratings yet

- COEN 3137 - Experiment No. 7 - Synchronous Binary CountersDocument19 pagesCOEN 3137 - Experiment No. 7 - Synchronous Binary Countersjocansino4496No ratings yet

- Tutorial CCB1223Document7 pagesTutorial CCB1223MOHD ZAMRI BIN IBRAHIMNo ratings yet

- 6 CountersDocument52 pages6 CountersBiniam TeferiNo ratings yet

- Due Date: 16.03.2006 Quiz I Chapter 6: Flip-Flops (Master Slave, Edge-Triggered), Analysis and Design of Sequential Circuits. March 16/2006Document2 pagesDue Date: 16.03.2006 Quiz I Chapter 6: Flip-Flops (Master Slave, Edge-Triggered), Analysis and Design of Sequential Circuits. March 16/2006mivriNo ratings yet

- Apr - May 2023Document3 pagesApr - May 2023Pandyselvi BalasubramanianNo ratings yet

- Digital Electronics ExamDocument4 pagesDigital Electronics ExamPeter JumreNo ratings yet

- Ee2255 Digital Logic CircuitsDocument3 pagesEe2255 Digital Logic CircuitsecessecNo ratings yet

- Digital Logic Design: CountersDocument44 pagesDigital Logic Design: CountersZelalem MeskiNo ratings yet

- 15 Hw03 DigitalSystems IDocument3 pages15 Hw03 DigitalSystems IWilliam ZhuangNo ratings yet

- Course 2 Acquisition and Treatment of Experimental Data 1. Sequential Logic CircuitsDocument14 pagesCourse 2 Acquisition and Treatment of Experimental Data 1. Sequential Logic CircuitsAna HodorogeaNo ratings yet

- Dflipfop Easy Problem Marvin JavierDocument9 pagesDflipfop Easy Problem Marvin JavierAngelica FangonNo ratings yet

- Assignment EDES232CDocument3 pagesAssignment EDES232CPrakash DasNo ratings yet

- 'Bahria University, Islamabad: Name: - EnrolmentDocument3 pages'Bahria University, Islamabad: Name: - EnrolmentHumza ZahidNo ratings yet

- Analog and Digital Electronics Laboratory: Truthtable-Jkflip-Flop Clock KQDocument7 pagesAnalog and Digital Electronics Laboratory: Truthtable-Jkflip-Flop Clock KQCovid CentreNo ratings yet

- Open Book TestDocument2 pagesOpen Book TestrodneymandizvidzaNo ratings yet

- DLD Lab-11 Sequential Circuit Using SR, D and JK Flip-Flop: Software: Circuit Maker TASK1Document7 pagesDLD Lab-11 Sequential Circuit Using SR, D and JK Flip-Flop: Software: Circuit Maker TASK1Anonymous AnonymousNo ratings yet

- 3CS3 04 PDFDocument3 pages3CS3 04 PDFprashantvlsiNo ratings yet

- Chapter 06Document4 pagesChapter 06leeNo ratings yet

- Stldmid2 PDFDocument4 pagesStldmid2 PDFsreekantha2013No ratings yet

- Lecture7 Chapter5 - Design of Clocked Sequential CircuitsDocument26 pagesLecture7 Chapter5 - Design of Clocked Sequential CircuitsHamza RiazNo ratings yet

- Answer Two Questions, Question No. 3 Is CompulsoryDocument3 pagesAnswer Two Questions, Question No. 3 Is CompulsoryABHILESH G KNo ratings yet

- EE2001 Tutorial 5Document9 pagesEE2001 Tutorial 5RetheshNo ratings yet

- Core-Iii-558-32511303-Digital Electronics and VHDL-21-12-2020Document4 pagesCore-Iii-558-32511303-Digital Electronics and VHDL-21-12-2020Sachin KumarNo ratings yet

- KPR Institute of Engineering and Technology Dept: Ac - Yr.: 2020-2021Document2 pagesKPR Institute of Engineering and Technology Dept: Ac - Yr.: 2020-2021Monith ViswanathanNo ratings yet

- Sequential CircuitsDocument33 pagesSequential CircuitsPrasun SinghalNo ratings yet

- Question Bank M Tech 2ND Sem Batch 2018Document31 pagesQuestion Bank M Tech 2ND Sem Batch 2018king khanNo ratings yet

- BMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsDocument3 pagesBMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsrameshNo ratings yet

- Extra Tutorial AnsDocument19 pagesExtra Tutorial Ansمحمد النقيبNo ratings yet

- Digital Logic For Computers (ACOE161) : Experiment #8 Flip-Flops - Pre-Lab ReportDocument8 pagesDigital Logic For Computers (ACOE161) : Experiment #8 Flip-Flops - Pre-Lab ReportOrangzaib RaoNo ratings yet

- ECE 124 Week 7 ReviewDocument55 pagesECE 124 Week 7 Reviewjahnavi thotaNo ratings yet

- FY Btech - EX - Electrical & Electronics Engineering - SEM - I - JAN 2023Document3 pagesFY Btech - EX - Electrical & Electronics Engineering - SEM - I - JAN 2023kumbhalkarvalay8No ratings yet

- Aits 2021 FT Ix Jeem.Document16 pagesAits 2021 FT Ix Jeem.Atharv AtoleNo ratings yet

- 15es3gcdec Dec 2017Document4 pages15es3gcdec Dec 2017MAHESHA GNo ratings yet

- Final CEG3155 Fall 2008Document17 pagesFinal CEG3155 Fall 2008TrulyboredNo ratings yet

- EC Digital-Circuits PDFDocument69 pagesEC Digital-Circuits PDFbharat patelNo ratings yet

- Chapter 7 SolutionDocument6 pagesChapter 7 SolutiongglrNo ratings yet

- Phy 10 MergedDocument22 pagesPhy 10 MergedPranav GurjarNo ratings yet

- Ece3 Edc May07Document2 pagesEce3 Edc May07InspireKaranNo ratings yet

- 2015 05 08 16 51 31Document12 pages2015 05 08 16 51 31mail2sgarg_841221144No ratings yet

- 3 SequentialDocument25 pages3 SequentialXXXNo ratings yet

- DigitalDocument68 pagesDigitalDibyarekha MaharanaNo ratings yet

- D Flip-Flop JK Flip-Flop SR-latch T Flip-Flop D Q J K Q S R Q T Q 0 0 0 0 0 0 1 0 1 0 1 1 1 0 1 0 1 1 1 1Document4 pagesD Flip-Flop JK Flip-Flop SR-latch T Flip-Flop D Q J K Q S R Q T Q 0 0 0 0 0 0 1 0 1 0 1 1 1 0 1 0 1 1 1 1Mộc SầuNo ratings yet

- EE 101 Mid-Sem Exam (MBP) : S S C + C +Document2 pagesEE 101 Mid-Sem Exam (MBP) : S S C + C +Kvv YadavNo ratings yet

- APR2013P21Document63 pagesAPR2013P21qsashutoshNo ratings yet

- DPP - 10 Physics:: Syllabus: KTG, Heat and ThermodynamicsDocument12 pagesDPP - 10 Physics:: Syllabus: KTG, Heat and Thermodynamicsravi shankarNo ratings yet

- Lab D4 CounterDocument8 pagesLab D4 Counterdhanabadee.kNo ratings yet

- Bals3033 Logic System DesignDocument5 pagesBals3033 Logic System DesignZhong Kiat TehNo ratings yet

- Ade Unit - 4 QBDocument17 pagesAde Unit - 4 QBNithya SNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Comp R16 Sem-VIII CSC801 Adhoc-Wireless-NetworkSample-QuestionsDocument7 pagesComp R16 Sem-VIII CSC801 Adhoc-Wireless-NetworkSample-QuestionsAbubakar KamalNo ratings yet

- Manual SilverfrostDocument15 pagesManual SilverfrostjuniorNo ratings yet

- Ca ReportDocument9 pagesCa ReportMandela HouseNo ratings yet

- EMV SWG NH20r2a Issuer Security Guidelines For 1st Gen August2018Document78 pagesEMV SWG NH20r2a Issuer Security Guidelines For 1st Gen August2018This FNo ratings yet

- How To Enter and Query Arabic Characters Into or From Database Via Forms ApplicationDocument2 pagesHow To Enter and Query Arabic Characters Into or From Database Via Forms ApplicationSHAHID FAROOQNo ratings yet

- Survey of Wormhole Attack in Wireless Sensor NetworksDocument10 pagesSurvey of Wormhole Attack in Wireless Sensor NetworksCSIT iaesprimeNo ratings yet

- Prim's and Kruskal's AlgorithmDocument58 pagesPrim's and Kruskal's AlgorithmAashish Kohli SarrafNo ratings yet

- Interpolation Methods - MATLAB & SimulinkDocument2 pagesInterpolation Methods - MATLAB & SimulinkjamsonjustiNo ratings yet

- DithDocument2 pagesDithjudith boringotNo ratings yet

- Parts Breakdown For Remote Mount Dmr-300-15-Xl-200Document1 pageParts Breakdown For Remote Mount Dmr-300-15-Xl-200UB HeavypartsNo ratings yet

- Ampoule Filling Line BDocument4 pagesAmpoule Filling Line BRahul JainNo ratings yet

- Dsu Microproject (Linked List) Ayush SasaneDocument18 pagesDsu Microproject (Linked List) Ayush SasaneAyush Sasane50% (2)

- CE 316 Slab Bridge Design (Final) PDFDocument12 pagesCE 316 Slab Bridge Design (Final) PDFhburitiNo ratings yet

- Apps My Apps: Google - Apps On Google PlayDocument3 pagesApps My Apps: Google - Apps On Google PlayJesNo ratings yet

- In Situ 3D Nanoprinting of Free-Form Coupling Elements For Hybrid Photonics IntegrationDocument9 pagesIn Situ 3D Nanoprinting of Free-Form Coupling Elements For Hybrid Photonics IntegrationMiles FernsbyNo ratings yet

- Project 2Document19 pagesProject 2api-515961562No ratings yet

- 003 ME31002 - Block Diagram-2021febDocument54 pages003 ME31002 - Block Diagram-2021febShek Yu LaiNo ratings yet

- TDS TutorialDocument33 pagesTDS Tutorialg2bfq6t7njNo ratings yet

- mq90 Develop PDFDocument1,328 pagesmq90 Develop PDFqihanchongNo ratings yet

- Od 430434800625785100Document2 pagesOd 430434800625785100agarwalanish041No ratings yet

- Anatomy-Specific Classification of Medical Images Using Deep Convolutional NetsDocument4 pagesAnatomy-Specific Classification of Medical Images Using Deep Convolutional NetsSiva SreeramdasNo ratings yet

- Cmpe 2 Lab M PDFDocument11 pagesCmpe 2 Lab M PDFNitheesh KumarNo ratings yet