Professional Documents

Culture Documents

Multistage BJT CC-CC Amplifier Experiment

Uploaded by

5611 M.Mubeen M.yaseenOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Multistage BJT CC-CC Amplifier Experiment

Uploaded by

5611 M.Mubeen M.yaseenCopyright:

Available Formats

Experiment No.

05

Multistage BJT CC-CC Amplifier (Darlington Configuration)

OBJECTIVE

Construct an RC coupled Multistage Amplifier with two Common Collector

amplifiers then analyze its performance in terms of gain, input and output

impedance.

EQUIPMENT

Instruments Components

• Digital Multimeter (DMM) • Transistors: 2N3904 (02)

• Oscilloscope with probes. • Resistors: 68 kΩ (02), 680 Ω

• Function generator. • Capacitors: 0.1F, 100µF

• Potentiometer 1 kΩ, 5 kΩ, 100 kΩ, 500 kΩ

THEORY

The Darlington Transistor named after its inventor, Sidney Darlington is a special arrangement

of two standard NPN or PNP bipolar junction transistors (BJT) connected together. The Emitter

of one transistor is connected to the Base of the other to produce a more sensitive transistor with

a much larger current gain being useful in applications where current amplification or switching

is required.

The Darlington Pair may sometimes also be referred to as a super-alpha pair, but this name is

used less these days. The circuit configuration was invented at Bell Laboratories by Sidney

Darlington in 1953 at the time when a significant amount of work was being undertaken into

transistor development. The idea is to have two or three transistors on a single chip where the

emitter of one transistor was connected to the base of the next, and all the transistors in the

Darlington configuration shared the same collector.

Darlington pair transistor circuits can be formed from two individual electronic components, i.e.

two transistors, or it is also possible to obtain them as a single electronic component with the two

transistors integrated onto one chip. Many Darlington arrays are also available where several

Darlington transistor pairs are contained within the same package. Typically these are contained

within an IC package as these are often used to drive displays, etc. This makes Darlington

transistor pairs very easy to use and incorporate into a new electronic design.

Electronic Circuit Design Lab Manual

CIRCUIT DIAGRAM

I1

IB1 =

I1 - I2

I2

VO1

Fig 5.1: Multistage Darlington configuration.

PROCEDURE

1. Using a Multimeter, measure the value of all Resistors and Capacitors being used in the

circuit. Also verify working of your BJT by testing it with DMM.

2. To find Q point:

Connect the circuit without Vin and capacitors. Set Vcc= 15V. Measure dc voltages at the

base VB1, VB2, collector Vc1, VC2 and Emitter VE1, VE2 with respect to ground. Determine

VCE1, VCE2 and IB1, IE2. The Q points are respectively Q1 (VCE1, IB1) and Q2 (VCE2,IE2).

3. Now connect the circuit as per the circuit diagram.

4. Mid-band Gain and Mid-band frequency:

a. Connect the signal generator and apply a sine wave of peak-to peak amplitude 1 V at 10

kHz.

b. Connect input (Vin) and first stage output VO1 and actual output VO of the circuit

separately to oscilloscope channels and observe the waveforms.

Electronic Circuit Design Lab Manual

c. Vary the frequency of the input signal (between 1 kHz till 1 MHz) till the output signal

VO maximizes.

d. If the output signal becomes distorted, reduce the input signal amplitude till the output

signal is free of distortion.

e. Once maximum is achieved, note down the peak to peak amplitude of Vin, VO1 and VO.

f. Calculate Mid-band voltage gain of both amplifier stages using the values evaluated in

last step AV1 = VO1/Vin and AV2 = VO/ VO1 and overall voltage gain GV= AV1 x AV2.

g. The frequency at which maximum gain is achieved is the mid-band frequency.

5. Input impedance:

POT

Vo

Vin

Fig 5.2: Input impedance finding technique.

a. Connect a Potentiometer (POT) between input voltage source and the base of the

transistor (series connection).

Set Potentiometer (POT) to zero.

Keep Input sine wave amplitude to the one evaluated in step 4(e).

Keep Input sine wave frequency to any mid band frequency evaluated in step

4(f).

b. Connect AC voltmeter (Range: 0-10V) across the biasing resistor R2.

c. Vary the value of Potentiometer such that the AC voltmeter reads a voltage half of the

input signal value.

d. Measure the value of the potentiometer with a multimeter. This is the Input Impedance at

mid-band frequency.

6. Output impedance:

Pot Vo

Vin

Fig 5.3: Output impedance finding technique.

Electronic Circuit Design Lab Manual

a. Connect a Potentiometer between input voltage source and the base of the transistor

(series connection)

b. Set the following:

Potentiometer to maximum value.

Keep Input sine wave amplitude to the one evaluated in step 4(e).

Keep Input sine wave frequency to any mid band frequency evaluated in step

4(f).

c. Connect AC voltmeter (Range: 0-10 V) across the biasing resistor RC and measure

Output Voltage.

d. Decrease Potentiometer till output voltage reduces to one half of the one achieved in

step 6(c).

e. Measure the value of the potentiometer with a multimeter. This is the Output Impedance

at mid-band frequency.

6. Theoretical Calculations:

a. Solve the circuit using a pen and paper and evaluate the theoretical values of the mid-

band gain, input and output impedance.

7. Observations:

a. Write down your observations in the Conclusions portion.

RESULTS & CALCULATIONS

Table 5.1: Measured Circuit Parameter

Parameter Measured Parameter Measured

Name Value Name Value

Cb1 0.1 uF I1 0.11 mA

R1 68 KΩ I2 0.11 mA

R2 68 KΩ IB1 40.738uA

Re 680 Ω IE2 9.078 mA

Ce2 100 uF β1 150

VCC 15 V β2 150

VCE1 8.104 V

VCE2 8.827 V

Electronic Circuit Design Lab Manual

Table 5.2: Representation of Mid-band gain and frequency

Input Output Output

Freq. Voltage Voltage Voltage Av1= GV = GV (dB) =

Av2=

(Hz) AV! * AV2 20log AV

(Vi ) (VO1) (VO) VO1/Vin VO2/VO1

10 K 1 Vp 0.995 Vp 0.99 Vp 0.995 0.994 0.989 -0.096 db

Table 5.3: Comparison of theoretical and practical values

practical

Input impedance 484.07 microvolt

Output impedance 478.399microvolt

midband 0.989

CONCLUSION:

I Construct an RC coupled Multistage Amplifier with two Common Collector amplifiers .I calculate

its performance in terms of gain, input and output impedance.

Electronic Circuit Design Lab Manual

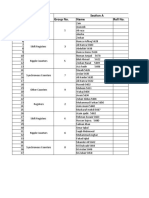

Activity Name Experiment No 5

Group No. 1 Section A

Student Roll No. 5611

C P Domain Awarded Score (out of 4 for each cell)

L L + Beg in ning Developing Exe mplary

O O Taxonomy (1) (2) Accomplished (4)

Student is With (3) Student is

unable to instructor/ With able to

design supervisor’s instructor/ independentl

systems, guidance, supervisor’s y design

guidance, systems,

No. Criteria components student is able

and/or to partially student is able components

processes to design to fully design and/or

meet systems, systems, processes to

specificatio components components meet

ns despite and/or and/or specification

instructor/ processes to processes to s without

supervisor’s meet meet instructor/

specifications. supervisor’s

guidance. specifications.

guidance.

1 4 2 P4 Design systems, components and/or processes to

me e t specifications

2 5 10 A3 Effe ctively document/ communicate performed

activities

Signature With Date: ____ _

Electronic Circuit Design Lab Manual

You might also like

- Experiment No. 04: RC Coupled Multistage CE-CC Cascade AmplifierDocument5 pagesExperiment No. 04: RC Coupled Multistage CE-CC Cascade Amplifier5611 M.Mubeen M.yaseenNo ratings yet

- Experiment No. 05: RC Coupled Multistage CE-CC Cascade AmplifierDocument5 pagesExperiment No. 05: RC Coupled Multistage CE-CC Cascade AmplifierM. Ahmad RazaNo ratings yet

- Experiment No. 02: RC Coupled Single Stage BJT Common Collector AmplifierDocument5 pagesExperiment No. 02: RC Coupled Single Stage BJT Common Collector AmplifierSajawal AliNo ratings yet

- RC Coupled BJT Common Collector Amplifier ExperimentDocument5 pagesRC Coupled BJT Common Collector Amplifier Experiment5611 M.Mubeen M.yaseenNo ratings yet

- Experiment No. 02: RC Coupled Single Stage BJT Common Collector AmplifierDocument5 pagesExperiment No. 02: RC Coupled Single Stage BJT Common Collector Amplifier5611 M.Mubeen M.yaseenNo ratings yet

- Ae Exp 9 Student ManualDocument4 pagesAe Exp 9 Student ManualAINo ratings yet

- ECD1223 ANALOGUE ELECTRONICS LAB 1: COMMON-EMITTER AMPLIFIER BIASING & GAINDocument10 pagesECD1223 ANALOGUE ELECTRONICS LAB 1: COMMON-EMITTER AMPLIFIER BIASING & GAINSam LiangNo ratings yet

- Electronics Circuit Lab ManualDocument50 pagesElectronics Circuit Lab ManualkrajenderreddyNo ratings yet

- Laboratory Report on Integrator and Differentiator CircuitDocument22 pagesLaboratory Report on Integrator and Differentiator CircuitHrivu Dasmunshi (RA1911004010566)No ratings yet

- UEEA1333 Operational Amplifier Lab SimulationDocument4 pagesUEEA1333 Operational Amplifier Lab SimulationKiritoNo ratings yet

- Expt No. 2 (B) Common Base AmplifierDocument11 pagesExpt No. 2 (B) Common Base Amplifierrani kumarNo ratings yet

- Lab Mannual PDFDocument26 pagesLab Mannual PDFssptc Magazine100% (1)

- EmtDocument115 pagesEmtRaj SharmaNo ratings yet

- FET Amplifier Frequency ResponseDocument30 pagesFET Amplifier Frequency ResponseANo ratings yet

- Electronic Devices Lab - Exp - 7 - Student - Manual (Summer 18-19)Document4 pagesElectronic Devices Lab - Exp - 7 - Student - Manual (Summer 18-19)MD MONIM ISLAMNo ratings yet

- RC Coupled Amplifier Design and AnalysisDocument7 pagesRC Coupled Amplifier Design and AnalysisShweta GadgayNo ratings yet

- ME2143 Linear Circuits Lab ManualDocument20 pagesME2143 Linear Circuits Lab ManualQiao YuNo ratings yet

- Eee334 Lab#1 Ltspice and Lab Orientation - Instruments and MeasurementsDocument9 pagesEee334 Lab#1 Ltspice and Lab Orientation - Instruments and Measurementsplaystation0% (1)

- Analog Electronics Workbook PDFDocument43 pagesAnalog Electronics Workbook PDFGokul GNo ratings yet

- Electronics I (EECE 3110) Lab 5: MosfetsDocument9 pagesElectronics I (EECE 3110) Lab 5: Mosfetswaqas akramNo ratings yet

- AEC LabManualDocument30 pagesAEC LabManualPrateek PaliwalNo ratings yet

- Eca Lab-Min PDFDocument87 pagesEca Lab-Min PDFAkashita SharmaNo ratings yet

- Common Emitter Amplifier: S.No Name of The Component/ Equipment Specifications QtyDocument0 pagesCommon Emitter Amplifier: S.No Name of The Component/ Equipment Specifications Qtyagama1188No ratings yet

- EEE 111 lab manual 2Document6 pagesEEE 111 lab manual 2SHADOW manNo ratings yet

- Electronic Principles and Circuits Lab Manual - BEC303 - 18-11-2023Document69 pagesElectronic Principles and Circuits Lab Manual - BEC303 - 18-11-2023Maithira H0% (1)

- Optical & Microwave Lab ManualDocument31 pagesOptical & Microwave Lab ManualAnvar NazarNo ratings yet

- Long Report Lab 7Document15 pagesLong Report Lab 7Saragadam Naga Shivanath RauNo ratings yet

- Optical Lab - RECDocument26 pagesOptical Lab - RECGiri KanyakumariNo ratings yet

- Ae Exp 5 Student ManualDocument4 pagesAe Exp 5 Student ManualAINo ratings yet

- Ae Hardware PDFDocument55 pagesAe Hardware PDFIshani JhaNo ratings yet

- Analog Circuits Lab Manual: Atria Institute of TechnologyDocument60 pagesAnalog Circuits Lab Manual: Atria Institute of TechnologyTháHäKâduvàyîLzNo ratings yet

- Lab 2 Basic CMOS AmplifiersDocument5 pagesLab 2 Basic CMOS AmplifiersJatinKumarNo ratings yet

- DEVICE EXP 2 Student - 2Document4 pagesDEVICE EXP 2 Student - 2Pablo ChanNo ratings yet

- Ex05 Lim OpampDocument9 pagesEx05 Lim OpampLIM Sheryl M.No ratings yet

- ECA HARDWARE ManualDocument44 pagesECA HARDWARE ManualKiranmai KonduruNo ratings yet

- ELEC3106 Lab 1 - Op-Amp MeasurementsDocument3 pagesELEC3106 Lab 1 - Op-Amp MeasurementsRuben CollinsNo ratings yet

- Optical & Microwave Lab ManualDocument31 pagesOptical & Microwave Lab ManualAnvar NazarNo ratings yet

- Experiment 4: Limiter and Clamper CircuitsDocument9 pagesExperiment 4: Limiter and Clamper CircuitsKamal AhmadNo ratings yet

- Name: Date:: Experiment 08 BJT High Frequency ResponseDocument5 pagesName: Date:: Experiment 08 BJT High Frequency ResponseJuay Mae RianoNo ratings yet

- Ec2405 Optical and Microwave Ece Lab ManualDocument26 pagesEc2405 Optical and Microwave Ece Lab ManualVasu Manikandan100% (2)

- Ecd LR - 8Document10 pagesEcd LR - 8Faaran Ahmed Zaheer AhmedNo ratings yet

- Lab 4 - Differentiator & IntegratorDocument14 pagesLab 4 - Differentiator & IntegratorVickneswaran KalerwananNo ratings yet

- AEC Lab ManualDocument70 pagesAEC Lab ManualRohan BoseNo ratings yet

- ADE Lab Manual - Analog Part PDFDocument21 pagesADE Lab Manual - Analog Part PDFJk RinkuNo ratings yet

- UEEA1333 Practical 1QDocument5 pagesUEEA1333 Practical 1QDorcas cosmasNo ratings yet

- Analog Integrated Circuits Lab ManualDocument133 pagesAnalog Integrated Circuits Lab Manualprabhu4scribdNo ratings yet

- Laboratory Experiment 4 Rectifiers and FiltersDocument16 pagesLaboratory Experiment 4 Rectifiers and FiltersPajayNo ratings yet

- IC and ECAD LabDocument88 pagesIC and ECAD LabVeerayya JavvajiNo ratings yet

- Ex #8 Emitter FolleowerDocument5 pagesEx #8 Emitter FolleowermanishNo ratings yet

- Finalo CDSL ManualDocument86 pagesFinalo CDSL ManualSteny SimsonNo ratings yet

- RF Lab 2 Short (Final)Document7 pagesRF Lab 2 Short (Final)Lee Boon YeeNo ratings yet

- EC1256-Lab ManualDocument67 pagesEC1256-Lab Manualjeyaganesh86% (7)

- Lab 05Document3 pagesLab 05Juan TarquiNo ratings yet

- Electromagnetic Compatibility (EMC) Design and Test Case AnalysisFrom EverandElectromagnetic Compatibility (EMC) Design and Test Case AnalysisNo ratings yet

- Nonlinear Electronics 1: Nonlinear Dipoles, Harmonic Oscillators and Switching CircuitsFrom EverandNonlinear Electronics 1: Nonlinear Dipoles, Harmonic Oscillators and Switching CircuitsNo ratings yet

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsFrom EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNo ratings yet

- Control: Course Lecture SeriesDocument6 pagesControl: Course Lecture Series5611 M.Mubeen M.yaseenNo ratings yet

- Lecture 1.1 Introduction to Control SystemsDocument9 pagesLecture 1.1 Introduction to Control Systems5611 M.Mubeen M.yaseenNo ratings yet

- Lab ScreenDocument4 pagesLab Screen5611 M.Mubeen M.yaseenNo ratings yet

- Control: Course Lecture SeriesDocument10 pagesControl: Course Lecture Series5611 M.Mubeen M.yaseenNo ratings yet

- Experiment No. 14: Laboratory Hand Book Implementation of Siso, Sipo, Piso and Pipo Shift RegisterDocument9 pagesExperiment No. 14: Laboratory Hand Book Implementation of Siso, Sipo, Piso and Pipo Shift Register5611 M.Mubeen M.yaseenNo ratings yet

- SR.# Topics Section A Group No. Name Roll NoDocument2 pagesSR.# Topics Section A Group No. Name Roll No5611 M.Mubeen M.yaseenNo ratings yet

- Digital Logic Design (DLD) : Lecturer: Engr. Ali IqbalDocument18 pagesDigital Logic Design (DLD) : Lecturer: Engr. Ali Iqbal5611 M.Mubeen M.yaseenNo ratings yet

- Experiment No. 12: Implementation & Verification of Line Multiplexer & Demultiplexer ODocument30 pagesExperiment No. 12: Implementation & Verification of Line Multiplexer & Demultiplexer O5611 M.Mubeen M.yaseenNo ratings yet

- Circuit diagram guide: Finding IC, VCE & impedanceDocument4 pagesCircuit diagram guide: Finding IC, VCE & impedance5611 M.Mubeen M.yaseenNo ratings yet

- Experiment No. 12: Implementation & Verification of Line Multiplexer & Demultiplexer ODocument27 pagesExperiment No. 12: Implementation & Verification of Line Multiplexer & Demultiplexer O5611 M.Mubeen M.yaseenNo ratings yet

- Experiment No. 12: Implementation & Verification of Line Multiplexer & Demultiplexer ODocument30 pagesExperiment No. 12: Implementation & Verification of Line Multiplexer & Demultiplexer O5611 M.Mubeen M.yaseenNo ratings yet

- Hi. I Am MubeenDocument1 pageHi. I Am Mubeen5611 M.Mubeen M.yaseenNo ratings yet

- Experiment No. 12: Implementation & Verification of Line Multiplexer & Demultiplexer ODocument30 pagesExperiment No. 12: Implementation & Verification of Line Multiplexer & Demultiplexer O5611 M.Mubeen M.yaseenNo ratings yet

- Rclamp 7535 MDocument9 pagesRclamp 7535 MAlan jorgeNo ratings yet

- L 2 DrivetrainDocument34 pagesL 2 Drivetraincristiannnnnnnnnn50% (2)

- Fabrication of Multi Purpose Machine Drilling Cutting Milling ShapingDocument73 pagesFabrication of Multi Purpose Machine Drilling Cutting Milling ShapingKrishna Mouli KasimiNo ratings yet

- 1986 87 Autosleeper MagazineWMDocument45 pages1986 87 Autosleeper MagazineWMPaul ChurchNo ratings yet

- Manuar Rectificador de BateriasDocument7 pagesManuar Rectificador de BateriasPedrito OrangeNo ratings yet

- D6H SERIE 4RC02557 DESARMADO Y ARMADO DE GRUPOS DE EMBRAGUES DE DIRECCION Y FRENO Guayaquil Ecuador.Document11 pagesD6H SERIE 4RC02557 DESARMADO Y ARMADO DE GRUPOS DE EMBRAGUES DE DIRECCION Y FRENO Guayaquil Ecuador.Jean Carlos CalderonNo ratings yet

- Clutch Line Install Guide 2.0Document5 pagesClutch Line Install Guide 2.0Hybrid RacingNo ratings yet

- Room Air Conditioner: Service ManualDocument68 pagesRoom Air Conditioner: Service ManualjhonnyNo ratings yet

- 002-PDS-CON-007 Method Statement For FOC Installation, Splicing & TestingDocument15 pages002-PDS-CON-007 Method Statement For FOC Installation, Splicing & TestingMalik Zaman100% (1)

- Manual INT69 FRYL® Diagnose - Fbul-0033-EnDocument3 pagesManual INT69 FRYL® Diagnose - Fbul-0033-EnDouradoNo ratings yet

- 8.0 Inch IPS MIPI 800x1280 AML08021016-31DDocument13 pages8.0 Inch IPS MIPI 800x1280 AML08021016-31DcalvinkleinwuNo ratings yet

- Automotive Electrical Systems Course OverviewDocument6 pagesAutomotive Electrical Systems Course OverviewkannanchammyNo ratings yet

- 51 52 25 123 enDocument2 pages51 52 25 123 enNicole StewartNo ratings yet

- Tahseen Team Apple Glossary Part 1Document13 pagesTahseen Team Apple Glossary Part 1Abdulrahman AlabdanNo ratings yet

- HIMAX Electric Screwdriver InstructionDocument12 pagesHIMAX Electric Screwdriver Instructiontaili-himaxNo ratings yet

- Donaldson Torit - Easy Duct Master Cataloguel PDFDocument32 pagesDonaldson Torit - Easy Duct Master Cataloguel PDFtylerstearnsNo ratings yet

- Class 6-Computer Question AnswersDocument11 pagesClass 6-Computer Question AnswersCH MUBASHER MAQSOOD ALAMNo ratings yet

- SPLW 1281 08 0Document1 pageSPLW 1281 08 0Adiel Zipperer da SilvaNo ratings yet

- 3.0 Central Processing Unit: ITE 1922 - ICT ApplicationsDocument7 pages3.0 Central Processing Unit: ITE 1922 - ICT ApplicationsShine InstituteNo ratings yet

- Air Blowing Procedure 2Document4 pagesAir Blowing Procedure 2mostafaNo ratings yet

- Power Transformer Protection Relaying (Overcurrent, Restricted Earth Fault & Differential) - EEPDocument30 pagesPower Transformer Protection Relaying (Overcurrent, Restricted Earth Fault & Differential) - EEPDurgeshkumar RajputNo ratings yet

- Canon CXDI-31 X-Ray - Service Manual PDFDocument209 pagesCanon CXDI-31 X-Ray - Service Manual PDFTony Nava0% (1)

- PREVENTA™ XPS Safety Relays: Emergency Stop and Limit Switch MonitoringDocument24 pagesPREVENTA™ XPS Safety Relays: Emergency Stop and Limit Switch MonitoringPapahnya Qiana MaulinaNo ratings yet

- EC206 CO Modelqn2 Ktustudents - inDocument3 pagesEC206 CO Modelqn2 Ktustudents - ingpuonlineNo ratings yet

- Dyson Cyclone V10 Absolute (Copper) - User Manual (Original File Name - ''Dyson-stick-V10-Absolute-Vacuum-user-guide - PDF'')Document16 pagesDyson Cyclone V10 Absolute (Copper) - User Manual (Original File Name - ''Dyson-stick-V10-Absolute-Vacuum-user-guide - PDF'')TalNo ratings yet

- Rayburn 460-499KB Serv 05-14 EINS 511642Document44 pagesRayburn 460-499KB Serv 05-14 EINS 511642ChristopherJones100% (2)

- ServerOn - QCT Server SpecDocument2 pagesServerOn - QCT Server SpecMas Ahmad Safwan MasbahNo ratings yet

- Manual de Usuario Stihl 009 (53 Páginas)Document1 pageManual de Usuario Stihl 009 (53 Páginas)toyioriginalNo ratings yet

- Sensors and Instrumentation ProjectDocument9 pagesSensors and Instrumentation ProjectSai Sandeep RayanuthalaNo ratings yet

- E-11 - 4 TRX Vhf-Am Ground To Air (Gta)Document3 pagesE-11 - 4 TRX Vhf-Am Ground To Air (Gta)Andre AryaNo ratings yet