Professional Documents

Culture Documents

Azc199 02S

Uploaded by

HamzaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Azc199 02S

Uploaded by

HamzaCopyright:

Available Formats

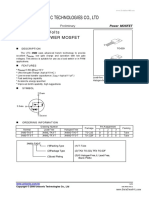

AZC199-02S

Low Capacitance High ESD Level Protection Array

For High Speed I/O Port

Features Description

ESD Protect for 2 high-speed I/O lines AZC199-02S is a design which includes ESD

Provide ESD protection for each line to rated diode arrays to protect high speed data

IEC 61000-4-2,(ESD) (contact/air) ±16kV interfaces. The AZC199-02S has been

IEC 61000-4-4 (EFT) Level-3, 55A (5/50ns) specifically designed to protect sensitive

IEC 61000-4-5 (Lightning) 5A (8/20µs) components which are connected to data and

For low operating voltage applications: 5V, transmission lines from over-voltage caused by

4.2V, 3.3V, 2.5V etc. Electrostatic Discharging (ESD).

Low capacitance : 1.6pF typical AZC199-02S is a unique design which includes

Fast turn-on and Low clamping voltage ESD rated, low capacitance steering diodes and

Array of ESD rated diodes with internal a unique design of clamping cell which is an

equivalent TVS diode equivalent TVS diode in a single package. During

Solid-state silicon-avalanche and active circuit transient conditions, the steering diodes direct

triggering technology the transient to ground line. The internal unique

Green part design of clamping cell prevents over-voltage on

the data line, protecting any downstream

Applications components.

Video Graphics Cards AZC199-02S may be used to meet the ESD

Digital Visual Interface (DVI) immunity requirements of IEC 61000-4-2, Level 4

USB2.0 Power and Data lines protection

(±15kV air, ±8kV contact discharge).

Notebook and PC Computers

Monitors and Flat Panel Displays

Circuit Diagram Pin Configuration

GND

1 2 3

3 1 2

I/O I/O

JEDEC SOT23-3L (Top View)

Revision 2016/06/21 ©2016 Amazing Micro. 1 www.amazingIC.com

AZC199-02S

Low Capacitance High ESD Level Protection Array

For High Speed I/O Port

SPECIFICATIONS

ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL RATING UNITS

Peak Pulse Current (tp =8/20µs) IPP 5 A

Operating Supply Voltage VDC 6 V

ESD per IEC 61000-4-2 (Air/Contact) VESD ±16 kV

o

Lead Soldering Temperature TSOL 260 (10 sec.) C

o

Operating Temperature TOP -55 to +85 C

o

Storage Temperature TSTO -55 to +150 C

DC Voltage at any I/O pin VIO (GND – 0.5) to 5.5 V

ELECTRICAL CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Reverse Stand-Off

VRWM Pin 1/2 to Pin3, T=25 oC 5 V

Voltage

Leakage Current ILeak Vpin1 or pin2 = 5V, VPin3 = 0V, T=25 oC 1 µA

Reverse Breakdown

VBV IBV = 1mA, T=25 oC, Pin 1/2 to Pin 3 7 10 V

Voltage

Forward Voltage VF IF = 15mA, T=25 oC, Pin 3 to Pin1/2 0.85 1.1 V

o

ESD Clamping IEC 61000-4-2 +6kV, T=25 C, Contact

Vclamp 11 V

Voltage mode, Pin 1/2 to Pin 3

ESD Dynamic Turn on IEC 61000-4-2 0~+6kV,T=25 oC, Contact

Rdynamic 0.3 Ω

Resistance mode, Pin 1/2 to Pin 3

Lightning Clamping Vlightning IPP=5A, tp=8/20µs, T=25 oC 8.5 V

Voltage Pin 1/2 to Pin 3

Channel Input Vpin3=0V,Vpin1 or 2=2.5V, f=1MHz,T=25oC,

CIN 1.6 1.9 pF

Capacitance Pin 1/2 to Pin 3

Channel to Channel Vpin3 =0V, Vpin1 or 2=2.5V, f=1MHz,

CCROSS 0.23 0.28 pF

Input Capacitance T=25oC, Between Pin 1 and Pin 2

Variation of Channel Vpin3 =0V, Vpin1 or 2=2.5V, f=1MHz,

△CIN 0.06 0.08 pF

Input Capacitance T=25oC, (Pin 1 to Pin 3)–(Pin 2 to Pin 3)

Revision 2016/06/21 ©2016 Amazing Micro. 2 www.amazingIC.com

AZC199-02S

Low Capacitance High ESD Level Protection Array

For High Speed I/O Port

Typical Characteristics

Typical Variation of CIN vs. VIN Typical Variation of CIO-to-IO vs. VIN

2.4 0.50

2.1 0.45

0.40

Input Capacitance (pF)

Input Capacitance (pF)

1.8

0.35

1.5 0.30

1.2 0.25

0.9 0.20

0.15

0.6

f = 1MHz, T=25 oC, 0.10 f = 1MHz, T=25 oC,

0.3 0.05

0.0 0.00

0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0

Input Voltage (V) Input Voltage (V)

Clamping Voltage vs. Peak Pulse Current

Forward Clamping Voltage vs. Peak Pulse Current

12

5

11

Forward Clamping Voltage (V)

10

4

Clamping Voltage (V)

9

8

7 3

6

5

4 2

Waveform

3 Parameters: Waveform

2 tr=8µs Parameters:

1 tr=8µs

td=20µs

1 td=20µs

0

4.5 5.0 5.5 6.0 6.5 7.0 0

4.5 5.0 5.5 6.0 6.5 7.0 7.5 8.0 8.5

Peak pulse Current (A)

Peak pulse Current (A)

Transmission Line Pulsing (TLP) Measurement

Transmission Line Pulsing (TLP) Current (A)

18

16

14

V_pulse

12 Pulse from a

transmission line

TLP_I

10 100ns +

TLP_V DUT

8 -

4

I/O to GND

2

0

0 2 4 6 8 10 12

Transmission Line Pulsing (TLP) Voltage (V)

Revision 2016/06/21 ©2016 Amazing Micro. 3 www.amazingIC.com

AZC199-02S

Low Capacitance High ESD Level Protection Array

For High Speed I/O Port

Applications Information In order to obtain enough suppression of ESD

induced transient, good circuit board is critical.

The AZC199-02S is designed to protect two lines Thus, the following guidelines are recommended:

against System ESD/EFT/Lightning pulses by Minimize the path length between the

clamping them to an acceptable reference. protected lines and the AZC199-02S.

Place the AZC199-02S near the input

The usage of the AZC199-02S is shown in Fig. 1. terminals or connectors to restrict transient

Protected lines, such as data lines, control lines, coupling.

or power lines, are connected at pin 1 and 2. The The ESD current return path to ground

pin 3 should be connected directly to a ground should be kept as short as possible.

plane on the board. All path lengths connected to Use ground planes whenever possible.

the pins of AZC199-02S should be kept as short NEVER route critical signals near board

as possible to minimize parasitic inductance in edges and near the lines which the ESD

the board traces. transient easily injects to.

VDD

IC to be protected

data-1

Connector

High

Speed IO data-2

Ports

Control-1

GND

2 1 2 1

AZC199-02S

AZC199-02S

3 3

Fig. 1

Revision 2016/06/21 ©2016 Amazing Micro. 4 www.amazingIC.com

AZC199-02S

Low Capacitance High ESD Level Protection Array

For High Speed I/O Port

Fig. 2 shows another simplified example of using transient stress.

AZC199-02S to protect the control lines, high

speed data lines, and power lines from ESD

VDD

VCC

High Speed Control Line 2 1

Data Line

Chip-B

AZC199-02S

Chip-A

High Speed Control Line

Data Line

Chip-C 3

2 1

2 1

AZC199-02S

AZC199-02S

3

3

GND

Fig. 2

Revision 2016/06/21 ©2016 Amazing Micro. 5 www.amazingIC.com

AZC199-02S

Low Capacitance High ESD Level Protection Array

For High Speed I/O Port

Mechanical Details

SOT23-3L PACKAGE DIAGRAMS

TOP VIEW

END VIEW

SIDE VIEW

PACKAGE DIMENSIONS

Revision 2016/06/21 ©2016 Amazing Micro. 6 www.amazingIC.com

AZC199-02S

Low Capacitance High ESD Level Protection Array

For High Speed I/O Port

LAND LAYOUT

0.9mm

1.4mm

0.7mm 3.5mm

0.95mm 0.95mm

1.4mm

0.9mm 1.0mm 0.9mm

Notes:

This LAND LAYOUT is for reference purposes only. Please consult your manufacturing

partners to ensure your company’s PCB design guidelines are met.

MARKING CODE

3

Part Number Marking Code

C11XY

AZC199-02S

C11XY

1 2 (Green Part)

C11 = Device Code Note. Green means Pb-free, RoHS, and

X = Date Code Halogen free compliant.

Y = Control Code

Ordering Information

PN# Material Type Reel size MOQ/internal box MOQ/carton

AZC199-02S.R7G Green T/R 7 inch 4 reel=12,000/box 6 box=72,000/carton

Revision 2016/06/21 ©2016 Amazing Micro. 7 www.amazingIC.com

AZC199-02S

Low Capacitance High ESD Level Protection Array

For High Speed I/O Port

Revision History

Revision Modification Description

Revision 2009/03/12 Initial Formal Release.

1. Update the Company Logo.

Revision 2011/07/30

2. Add the Ordering Information.

Revision 2016/06/21 Add the Reverse Stand-Off Voltage.

Revision 2016/06/21 ©2016 Amazing Micro. 8 www.amazingIC.com

You might also like

- ESD Protection AZC099-04S PDFDocument12 pagesESD Protection AZC099-04S PDFChrist TianNo ratings yet

- For Operating Voltage of 5V and Below Ultra Low Capacitance: 0.5pF TypicalDocument10 pagesFor Operating Voltage of 5V and Below Ultra Low Capacitance: 0.5pF TypicalTri Nguyen Real EstateNo ratings yet

- Protect USB Data and Charging with Low Capacitance TVS ArrayDocument10 pagesProtect USB Data and Charging with Low Capacitance TVS ArrayhernanNo ratings yet

- Railclamp Low Capacitance Tvs Array: Protection Products - Railclamp Description FeaturesDocument10 pagesRailclamp Low Capacitance Tvs Array: Protection Products - Railclamp Description FeaturesEinson SepulvedaNo ratings yet

- Low Capacitance TVS For LVDS Interfaces: Protection Products - Railclamp Description FeaturesDocument8 pagesLow Capacitance TVS For LVDS Interfaces: Protection Products - Railclamp Description FeaturesAnibal Tantalean SarmientoNo ratings yet

- Railclamp Low Capacitance Tvs Array: Protection Products - Railclamp Description FeaturesDocument8 pagesRailclamp Low Capacitance Tvs Array: Protection Products - Railclamp Description FeaturesHemantkumarNo ratings yet

- IEC 61000-4-2 (ESD) 20kV (Air), 12kV (Contact) IEC 61000-4-4 (EFT) 40A (5/50ns) IEC 61000-4-5 (Lightning) 7A (8/20 S) Cable Discharge Event (CDE)Document6 pagesIEC 61000-4-2 (ESD) 20kV (Air), 12kV (Contact) IEC 61000-4-4 (EFT) 40A (5/50ns) IEC 61000-4-5 (Lightning) 7A (8/20 S) Cable Discharge Event (CDE)cafosokNo ratings yet

- Az5b0s 01FDocument6 pagesAz5b0s 01FJC CNo ratings yet

- 1.6mm X 1.0mm DFN Package Saves Board: Transient Voltage Suppressing Device For ESD and Surge ProtectionDocument7 pages1.6mm X 1.0mm DFN Package Saves Board: Transient Voltage Suppressing Device For ESD and Surge ProtectionxXMythicalRoseXNo ratings yet

- For Operating Voltage of 3.3V and Below Ultra Low Capacitance: 0.45pF TypicalDocument9 pagesFor Operating Voltage of 3.3V and Below Ultra Low Capacitance: 0.45pF TypicalFábio MenezesNo ratings yet

- TVL ST23 04 Ad0Document9 pagesTVL ST23 04 Ad0coulsonpfilNo ratings yet

- INPAQ Transient Voltage Suppressor TVLST2304BD0 Specification A0Document8 pagesINPAQ Transient Voltage Suppressor TVLST2304BD0 Specification A0Isaac CostaNo ratings yet

- Slvu2 8Document10 pagesSlvu2 8hadiNo ratings yet

- ESDSRVLC05-4: DescriptionDocument5 pagesESDSRVLC05-4: DescriptionelminerocapmaNo ratings yet

- ESD5302N-WillSEMIDocument7 pagesESD5302N-WillSEMIRenato Luiz TécnicoNo ratings yet

- 0402 Small DFN Package Saves Board SpaceDocument7 pages0402 Small DFN Package Saves Board Spacecarlos rumboNo ratings yet

- Low Capacitance TVS For LVDS Interfaces: Protection Products - Railclamp Description FeaturesDocument7 pagesLow Capacitance TVS For LVDS Interfaces: Protection Products - Railclamp Description FeaturesFakhri AliNo ratings yet

- CDDFN10-2574N - Surface Mount TVS Diode Array: Features ApplicationsDocument6 pagesCDDFN10-2574N - Surface Mount TVS Diode Array: Features ApplicationsAlexNo ratings yet

- IEC 61000-4-2 (ESD) 20kV (Air), 15kV (Contact) IEC 61000-4-4 (EFT) 50A (5/50ns) Cable Discharge Event (CDE)Document6 pagesIEC 61000-4-2 (ESD) 20kV (Air), 15kV (Contact) IEC 61000-4-4 (EFT) 50A (5/50ns) Cable Discharge Event (CDE)Ion PetruscaNo ratings yet

- 3N80Document6 pages3N80hectorsevillaNo ratings yet

- DatasheetDocument14 pagesDatasheetJagopati Jr.No ratings yet

- AC-DC LED Driver MT7930Document8 pagesAC-DC LED Driver MT7930Daniel GonzálezNo ratings yet

- Data SheetDocument10 pagesData SheetRaphael Silveira de SouzaNo ratings yet

- WILLSEMI Will Semicon ESD5311N 2 TR - C153721 PDFDocument5 pagesWILLSEMI Will Semicon ESD5311N 2 TR - C153721 PDFPippoNo ratings yet

- Ka78Mxx: 3-Terminal 0.5A Positive Voltage RegulatorDocument14 pagesKa78Mxx: 3-Terminal 0.5A Positive Voltage RegulatorTinwin HtutNo ratings yet

- RCLAMP0503NDocument7 pagesRCLAMP0503NAisya NurcahyaNo ratings yet

- LOW POWER QUAD OP AMPSDocument11 pagesLOW POWER QUAD OP AMPSАлександрNo ratings yet

- TVS Diode Array WE-TVS Specification SheetDocument5 pagesTVS Diode Array WE-TVS Specification SheetAlex LuzNo ratings yet

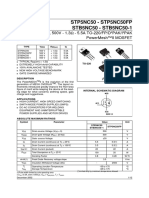

- STP 16 NF 06 FPDocument14 pagesSTP 16 NF 06 FPjoverjover1No ratings yet

- Stp5Nc50 - Stp5Nc50Fp Stb5Nc50 - Stb5Nc50-1: N-Channel 500V - 1.3 - 5.5A To-220/Fp/D Pak/I Pak Powermesh Ii MosfetDocument12 pagesStp5Nc50 - Stp5Nc50Fp Stb5Nc50 - Stb5Nc50-1: N-Channel 500V - 1.3 - 5.5A To-220/Fp/D Pak/I Pak Powermesh Ii MosfetJavier55No ratings yet

- Low Voltage Clamp For ESD and CDE Protection: Protection Products Protection Products - Microclamp Description FeaturesDocument6 pagesLow Voltage Clamp For ESD and CDE Protection: Protection Products Protection Products - Microclamp Description FeaturesAmirNo ratings yet

- Datasheet Acs 120 PDFDocument11 pagesDatasheet Acs 120 PDFyudi heriyantoNo ratings yet

- P2NC60FP-ST Microelectronics PDFDocument9 pagesP2NC60FP-ST Microelectronics PDFtherangerinNo ratings yet

- STP11NK50ZDocument13 pagesSTP11NK50ZWilliam OliveiraNo ratings yet

- DatasheetDocument10 pagesDatasheetMikael BarboNo ratings yet

- STP 10 NK 70 ZFPDocument13 pagesSTP 10 NK 70 ZFPOsama Bin AtaNo ratings yet

- TS1935BCX5: Taiwan SemiconductorDocument9 pagesTS1935BCX5: Taiwan Semiconductorn tanevarNo ratings yet

- MC78M12Document14 pagesMC78M12Radio AtelierNo ratings yet

- Dual Channel TVS Diode: ESD8V0L..Document6 pagesDual Channel TVS Diode: ESD8V0L..psujith_87No ratings yet

- Datasheet SFP50N06 PDFDocument7 pagesDatasheet SFP50N06 PDFAdeniltonNo ratings yet

- 20N60M2EP_mark_STP20N60M2-EP_600V_13A_FETDocument14 pages20N60M2EP_mark_STP20N60M2-EP_600V_13A_FETRuslanNo ratings yet

- SU0524 - Datasheet: 4-Channel Low Capacitance Esd Protection Diodes ArrayDocument10 pagesSU0524 - Datasheet: 4-Channel Low Capacitance Esd Protection Diodes ArrayPavel Martínez GonzálezNo ratings yet

- SU0524 - Datasheet: 4-Channel Low Capacitance Esd Protection Diodes ArrayDocument9 pagesSU0524 - Datasheet: 4-Channel Low Capacitance Esd Protection Diodes Arraytemp001100% (1)

- Railclamp Low Capacitance Tvs Diode Array: Protection Products Description FeaturesDocument13 pagesRailclamp Low Capacitance Tvs Diode Array: Protection Products Description Featuresrishi sagarNo ratings yet

- DatasheetDocument12 pagesDatasheetErwin Rolando EscobarNo ratings yet

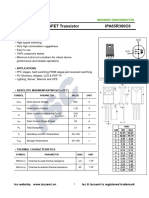

- Isc N-Channel MOSFET Transistor IPA65R380C6: INCHANGE SemiconductorDocument2 pagesIsc N-Channel MOSFET Transistor IPA65R380C6: INCHANGE SemiconductorVitor Andrade FonsecaNo ratings yet

- Acs 102Document8 pagesAcs 102Alexis RamonNo ratings yet

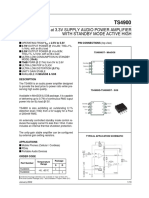

- 300Mw at 3.3V Supply Audio Power Amplifier With Standby Mode Active HighDocument19 pages300Mw at 3.3V Supply Audio Power Amplifier With Standby Mode Active HighPanagiotis PanagosNo ratings yet

- 1008AE Specification SummaryDocument11 pages1008AE Specification Summarynovram novNo ratings yet

- CESD3V3D3Document6 pagesCESD3V3D3Seung Hyun KoNo ratings yet

- 497 2334 5 DatasheetzDocument17 pages497 2334 5 DatasheetzanandaeizzNo ratings yet

- P6NK90ZFP STMicroelectronicsDocument12 pagesP6NK90ZFP STMicroelectronics15265562No ratings yet

- MTP3055V Power MOSFET 12 Amps, 60 Volts: N Channel TO 220Document7 pagesMTP3055V Power MOSFET 12 Amps, 60 Volts: N Channel TO 220Hectór DavidNo ratings yet

- Datasheet TN6Q04 PDFDocument4 pagesDatasheet TN6Q04 PDFDaniel AvecillaNo ratings yet

- Datasheet5641 ZenerDocument6 pagesDatasheet5641 ZenerDoppler ElectronicaNo ratings yet

- RDS(on) 0.4Ω N-Channel MOSFETDocument2 pagesRDS(on) 0.4Ω N-Channel MOSFETSitarda WantonoNo ratings yet

- Stp9Nk65Z Stp9Nk65Zfp: N-Channel 650V - 1 - 6.4A To-220/To-220Fp Zener-Protected Supermesh™Power MosfetDocument11 pagesStp9Nk65Z Stp9Nk65Zfp: N-Channel 650V - 1 - 6.4A To-220/To-220Fp Zener-Protected Supermesh™Power Mosfetnestor1209No ratings yet

- Maximum Ratings: Symbol Parameter Value UnitDocument1 pageMaximum Ratings: Symbol Parameter Value UnitGabriel EisenachNo ratings yet

- TRANSMISSION LINES - CHARACTERISTICS, EQUATIONS AND IMPEDANCE MATCHINGDocument5 pagesTRANSMISSION LINES - CHARACTERISTICS, EQUATIONS AND IMPEDANCE MATCHINGMunni 1123No ratings yet

- EM Fields Lecture NotesDocument104 pagesEM Fields Lecture NotesmwanjessNo ratings yet

- Practice Problems:: a b λ= c fDocument11 pagesPractice Problems:: a b λ= c fHazellynn TobiasNo ratings yet

- Transmission, Question 8Document7 pagesTransmission, Question 8Diether Dave IngcoNo ratings yet

- SciTech 2008 CatalogDocument16 pagesSciTech 2008 CatalogMohadig Widha RousstiaNo ratings yet

- 6628 LocatingFaults ES 20140210 Web PDFDocument18 pages6628 LocatingFaults ES 20140210 Web PDFbudipppNo ratings yet

- Radar Absorbing Materials - Mechanisms and Materials: February 1989Document37 pagesRadar Absorbing Materials - Mechanisms and Materials: February 1989Thanh Giang TrầnNo ratings yet

- RF BasicsDocument51 pagesRF BasicsIrshad HaqNo ratings yet

- Electromagnetic Waves and TransmissionDocument2 pagesElectromagnetic Waves and TransmissionAparna LakshmiNo ratings yet

- Microwave CommunicationsDocument6 pagesMicrowave CommunicationsAkhil AhmedNo ratings yet

- Identification of Catenary Harmonics 3kV DCDocument4 pagesIdentification of Catenary Harmonics 3kV DCIlan AtamanNo ratings yet

- Introduction to coaxial cables: Coaxial Cables, For Rf - Μwave - Various pag J1Document27 pagesIntroduction to coaxial cables: Coaxial Cables, For Rf - Μwave - Various pag J1AmithNo ratings yet

- Pmt200 Series Dehydrator User Manual: Bulletin AE01B-A0468-001 Rev: B 7 DEC 04Document20 pagesPmt200 Series Dehydrator User Manual: Bulletin AE01B-A0468-001 Rev: B 7 DEC 04vilnei menegottoNo ratings yet

- Transmission Line and Cables v6Document20 pagesTransmission Line and Cables v6Ezeldeen AgoryNo ratings yet

- Antenna FundamentalsDocument37 pagesAntenna FundamentalsMarco Aurelio PereiraNo ratings yet

- Sensors 12 15841 PDFDocument17 pagesSensors 12 15841 PDFLuis Mario De La PazNo ratings yet

- Measuring Coaxial Microwave SignalsDocument169 pagesMeasuring Coaxial Microwave Signalspravin maliNo ratings yet

- Gazi University Microwave Power Measurement LabDocument12 pagesGazi University Microwave Power Measurement LabemreNo ratings yet

- R16 ECE 3rd Year Digital Signal Processing SyllabusDocument7 pagesR16 ECE 3rd Year Digital Signal Processing SyllabusMallikarjunNo ratings yet

- 195 - EE8402, EE6402 Transmission and Distribution - Question Bank 2Document11 pages195 - EE8402, EE6402 Transmission and Distribution - Question Bank 2KrishNo ratings yet

- IEEE Transactions on Power Systems teaching transientsDocument5 pagesIEEE Transactions on Power Systems teaching transientsLucas EduardoNo ratings yet

- Lecture Notes - Microwaves PDFDocument18 pagesLecture Notes - Microwaves PDFSatish KumarNo ratings yet

- D.E.I. Technical College Network Analysis SyllabusDocument7 pagesD.E.I. Technical College Network Analysis SyllabusShivam Thakur AkhandNo ratings yet

- Microstrip Patch AntennaDocument15 pagesMicrostrip Patch AntennaSubhanjali MyneniNo ratings yet

- And 1he ''Phii - Adelphia Expfriment': Negative TimeDocument94 pagesAnd 1he ''Phii - Adelphia Expfriment': Negative TimegospodarmunjaNo ratings yet

- Impulse EMI Generator Generates Broadband InterferenceDocument4 pagesImpulse EMI Generator Generates Broadband InterferenceManish BairagiNo ratings yet

- III Year SyllabusDocument68 pagesIII Year SyllabusFaiz KarobariNo ratings yet

- Advanced Transmission Line Modeling TechniquesDocument12 pagesAdvanced Transmission Line Modeling TechniquesDushyant VaghelaNo ratings yet

- PSAs : Questions from Ch-1 Current and Voltage Relations on a Transmission LineDocument14 pagesPSAs : Questions from Ch-1 Current and Voltage Relations on a Transmission Linemsthacker0% (1)

- Homework 3Document3 pagesHomework 3Houseman74No ratings yet