Professional Documents

Culture Documents

CMOS Fabrication and Layout: Inverter Cross-Section

Uploaded by

Carlos Saavedra0 ratings0% found this document useful (0 votes)

6 views1 pageThis document discusses CMOS fabrication and layout. It begins by explaining that transistors are fabricated on silicon wafers which serve as both a mechanical support and electrical common point called the substrate. It then describes how the layout of transistors can be viewed from a top view looking down on the wafer or a cross-sectional view by slicing through the wafer. The document provides details on the cross-sectional view of a CMOS inverter, showing the p-type substrate and n-well region for the pMOS transistor. Fabrication is controlled through masks that define the size of transistors and wires based on the manufacturing process resolution.

Original Description:

Original Title

CMOS-VLSI-design-46

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document discusses CMOS fabrication and layout. It begins by explaining that transistors are fabricated on silicon wafers which serve as both a mechanical support and electrical common point called the substrate. It then describes how the layout of transistors can be viewed from a top view looking down on the wafer or a cross-sectional view by slicing through the wafer. The document provides details on the cross-sectional view of a CMOS inverter, showing the p-type substrate and n-well region for the pMOS transistor. Fabrication is controlled through masks that define the size of transistors and wires based on the manufacturing process resolution.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

6 views1 pageCMOS Fabrication and Layout: Inverter Cross-Section

Uploaded by

Carlos SaavedraThis document discusses CMOS fabrication and layout. It begins by explaining that transistors are fabricated on silicon wafers which serve as both a mechanical support and electrical common point called the substrate. It then describes how the layout of transistors can be viewed from a top view looking down on the wafer or a cross-sectional view by slicing through the wafer. The document provides details on the cross-sectional view of a CMOS inverter, showing the p-type substrate and n-well region for the pMOS transistor. Fabrication is controlled through masks that define the size of transistors and wires based on the manufacturing process resolution.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

1.

5 CMOS Fabrication and Layout 19

constructed. A collection of D flip-flops sharing a common clock input is called a register.

A register is often drawn as a flip-flop with multi-bit D and Q busses.

In Section 10.2.5 we will see that flip-flops may experience hold-time failures if the

system has too much clock skew, i.e., if one flip-flop triggers early and another triggers late

because of variations in clock arrival times. In industrial designs, a great deal of effort is

devoted to timing simulations to catch hold-time problems. When design time is more

important (e.g., in class projects), hold-time problems can be avoided altogether by dis-

tributing a two-phase nonoverlapping clock. Figure 1.33 shows the flip-flop clocked with

two nonoverlapping phases. As long as the phases never overlap, at least one latch will be

opaque at any given time and hold-time problems cannot occur.

1.5 CMOS Fabrication and Layout

Now that we can design logic gates and registers from transistors, let us consider how the

transistors are built. Designers need to understand the physical implementation of circuits

because it has a major impact on performance, power, and cost.

Transistors are fabricated on thin silicon wafers that serve as both a mechanical sup-

port and an electrical common point called the substrate. We can examine the physical lay-

out of transistors from two perspectives. One is the top view, obtained by looking down on

a wafer. The other is the cross-section, obtained by slicing the wafer through the middle of

a transistor and looking at it edgewise. We begin by looking at the cross-section of a com-

plete CMOS inverter. We then look at the top view of the same inverter and define a set

of masks used to manufacture the different parts of the inverter. The size of the transistors

and wires is set by the mask dimensions and is limited by the resolution of the manufac-

turing process. Continual advancements in this resolution have fueled the exponential

growth of the semiconductor industry.

1.5.1 Inverter Cross-Section

Figure 1.34 shows a cross-section and corresponding schematic of an inverter. (See the

inside front cover for a color cross-section.) In this diagram, the inverter is built on a

p-type substrate. The pMOS transistor requires an n-type body region, so an n-well is dif-

fused into the substrate in its vicinity. As described in Section 1.3, the nMOS transistor

φ2 φ1

QM

D Q

φ2 φ1

φ2 φ1

φ2 φ1

φ1

φ2

FIGURE 1.33 CMOS flip-flop with two-phase nonoverlapping clocks

You might also like

- CMOS Logic StructuresDocument23 pagesCMOS Logic StructuressuprabhuNo ratings yet

- X100V TranslatedDocument4 pagesX100V TranslatedFourthirds Rumors100% (2)

- Transistor Switching and Sequential CircuitsFrom EverandTransistor Switching and Sequential CircuitsRating: 5 out of 5 stars5/5 (1)

- Const-1 FM TransmitterDocument3 pagesConst-1 FM TransmitterJoy MukhNo ratings yet

- Cmos Vlsi Design 184Document1 pageCmos Vlsi Design 184Carlos SaavedraNo ratings yet

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- VLSI RamDocument18 pagesVLSI RamrAM100% (4)

- Unit # 5 Dynamic Cmos and ClockingDocument15 pagesUnit # 5 Dynamic Cmos and ClockingKiran KumariNo ratings yet

- DWDM Theory: ZTE University Transmission Course TeamDocument51 pagesDWDM Theory: ZTE University Transmission Course TeamWubie NegaNo ratings yet

- CMOS Transistor Layout KungFuDocument39 pagesCMOS Transistor Layout KungFuAyo Iji100% (5)

- b9. Instrumentation - Murphy Vs2 Shock-Vibration ControlDocument24 pagesb9. Instrumentation - Murphy Vs2 Shock-Vibration ControlNicolii RamonNo ratings yet

- Megger TestDocument1 pageMegger Testecruz_yhwhNo ratings yet

- Layout ExamplesDocument13 pagesLayout Examplesnazibhd786No ratings yet

- Enercon Super Seal Series ManualDocument63 pagesEnercon Super Seal Series ManualJeffri Galih S100% (2)

- WelchAllyn CP-100,200 ECG - Service ManualDocument96 pagesWelchAllyn CP-100,200 ECG - Service ManualHan ReylagnasNo ratings yet

- A Seminar On A Seminar On: HPLC Detectors HPLC DetectorsDocument36 pagesA Seminar On A Seminar On: HPLC Detectors HPLC DetectorsVivek SagarNo ratings yet

- Schematic Design and Layout of Flip Op Using CMOS TechnologyDocument4 pagesSchematic Design and Layout of Flip Op Using CMOS TechnologySatyam MishraNo ratings yet

- Ec1461 Vlsi DesignDocument17 pagesEc1461 Vlsi DesignArunkumarNo ratings yet

- Two Phase Non-Overlapping Clock DriverDocument9 pagesTwo Phase Non-Overlapping Clock DriverVictor ChangNo ratings yet

- Unit 3: Cmos Logic StructuresDocument14 pagesUnit 3: Cmos Logic StructuresPraveen AndrewNo ratings yet

- CMOS Question Bank 1Document3 pagesCMOS Question Bank 1Sameer R. KhanNo ratings yet

- Mtech Vlsi Short Answer QuestionsDocument8 pagesMtech Vlsi Short Answer QuestionsRachit NemaNo ratings yet

- Sub-System Design 5Document177 pagesSub-System Design 5Abdullah Gubbi100% (1)

- CMOS (Disambiguation) : For Other Uses, SeeDocument6 pagesCMOS (Disambiguation) : For Other Uses, SeeManas NagNo ratings yet

- CH 04 Delay Part 01Document25 pagesCH 04 Delay Part 01muneeb.abrarNo ratings yet

- Cmos Logic Families For Vlsi DesignDocument12 pagesCmos Logic Families For Vlsi DesignRishav YadavNo ratings yet

- 2023 Ch4-Elmore DelayDocument38 pages2023 Ch4-Elmore DelayAn NguyenNo ratings yet

- Cmos Dec 2019Document2 pagesCmos Dec 2019Prabhodh KulkarniNo ratings yet

- 5 2 10 While The Width of Nmos Transistor Is 6 . The Length of The Channel For Both Pmos and Nmos TransistorDocument14 pages5 2 10 While The Width of Nmos Transistor Is 6 . The Length of The Channel For Both Pmos and Nmos TransistorChiranth M PatilNo ratings yet

- ASSIGNMENTiiiDocument1 pageASSIGNMENTiiiVarun ParasharNo ratings yet

- Working of C MOS (Single Edge Triggered)Document4 pagesWorking of C MOS (Single Edge Triggered)Avinash BaldiNo ratings yet

- VLSI Design (Online Lectures) Assignment-1Document3 pagesVLSI Design (Online Lectures) Assignment-1TarushiNo ratings yet

- VLSI Design Subsystem Design and Architectural IssuesDocument26 pagesVLSI Design Subsystem Design and Architectural IssuesSanjana M PNo ratings yet

- Ade Exp 5 Bhuvan BeeraDocument6 pagesAde Exp 5 Bhuvan BeeraBhuvan BeeraNo ratings yet

- CMOS Inverter propagation delayDocument6 pagesCMOS Inverter propagation delayshashwatNo ratings yet

- Combinational Logic Circuits DesignDocument47 pagesCombinational Logic Circuits DesignHussein HasenNo ratings yet

- CMOS VLSI Design Chapter 4 Introduction to Delay CalculationsDocument54 pagesCMOS VLSI Design Chapter 4 Introduction to Delay CalculationsHuy TranNo ratings yet

- Designing Combinational Logic Gates in CMOSDocument125 pagesDesigning Combinational Logic Gates in CMOSArqam Ali KhanNo ratings yet

- Complementary Metal-Oxide-Semiconductor (CMOS) (PronouncedDocument7 pagesComplementary Metal-Oxide-Semiconductor (CMOS) (PronouncedArchana SadanandanNo ratings yet

- Wiki Loves Love: Documenting Festivals and Celebrations of Love On Commons. Help Wikimedia and Win Prizes by Sending PhotosDocument10 pagesWiki Loves Love: Documenting Festivals and Celebrations of Love On Commons. Help Wikimedia and Win Prizes by Sending PhotosraoNo ratings yet

- General Instructions To The CandidateDocument4 pagesGeneral Instructions To The Candidateapurv shuklaNo ratings yet

- Full Custom Mask Layout DesignDocument15 pagesFull Custom Mask Layout DesignBharathNo ratings yet

- CMOS Logic DesignDocument35 pagesCMOS Logic DesignsomosreeNo ratings yet

- CMOS Transistor Layout KungFu Preliminary ReleaseDocument35 pagesCMOS Transistor Layout KungFu Preliminary ReleaseBabu ChintapalliNo ratings yet

- Lect1 1Document22 pagesLect1 1Nitin SonuNo ratings yet

- UNIT-05-Advanced Techniques by BRRDocument27 pagesUNIT-05-Advanced Techniques by BRRBhargavi NarisettiNo ratings yet

- Welcome To International Journal of Engineering Research and Development (IJERD)Document8 pagesWelcome To International Journal of Engineering Research and Development (IJERD)IJERDNo ratings yet

- CMOS Transistor Layout KungFu Preliminary Release-1Document35 pagesCMOS Transistor Layout KungFu Preliminary Release-1someone9310No ratings yet

- Ec6111 - Vlsi DesignDocument9 pagesEc6111 - Vlsi DesignMegha SrivastavaNo ratings yet

- Vlsi 1 Chapter 111111111Document15 pagesVlsi 1 Chapter 111111111Dinesh PalavalasaNo ratings yet

- For Other Uses, See .: CMOS (Disambiguation)Document11 pagesFor Other Uses, See .: CMOS (Disambiguation)Smitha KollerahithluNo ratings yet

- Question Bank Fundamentals of CMOS VLSI-10EC56 15-16Document10 pagesQuestion Bank Fundamentals of CMOS VLSI-10EC56 15-16Pranav KpNo ratings yet

- CMOS Logic Circuits: DR S. C. WongDocument28 pagesCMOS Logic Circuits: DR S. C. WongMuni Sankar MatamNo ratings yet

- VlsiDocument16 pagesVlsiVishnu Vijay SNo ratings yet

- CMOS Logic Gates Speed Power CharacteristicsDocument34 pagesCMOS Logic Gates Speed Power CharacteristicsZiad Mohmed FawzyNo ratings yet

- Lecture 6aDocument24 pagesLecture 6aBernard Mkumbwa Jr.No ratings yet

- Analysis of CMOS 45nm Transmission Gate Based Pulsed Latch AbstractDocument12 pagesAnalysis of CMOS 45nm Transmission Gate Based Pulsed Latch AbstractbaluNo ratings yet

- Lect1 CktlayDocument45 pagesLect1 CktlayTân MinhNo ratings yet

- Zipper Cmos Logic CircuitDocument15 pagesZipper Cmos Logic CircuitShreerama Samartha G BhattaNo ratings yet

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipFrom EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo ratings yet

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsFrom EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsRating: 1 out of 5 stars1/5 (1)

- Token Ring Technology ReportFrom EverandToken Ring Technology ReportNo ratings yet

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsFrom EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsNo ratings yet

- Cmos Vlsi Design 203Document1 pageCmos Vlsi Design 203Carlos SaavedraNo ratings yet

- Cmos Vlsi Design 198Document1 pageCmos Vlsi Design 198Carlos SaavedraNo ratings yet

- Cmos Vlsi Design 208Document1 pageCmos Vlsi Design 208Carlos SaavedraNo ratings yet

- 4.4.6.4 Voltage Dependence: Chapter 4 DelayDocument1 page4.4.6.4 Voltage Dependence: Chapter 4 DelayCarlos SaavedraNo ratings yet

- Cmos Vlsi Design 186Document1 pageCmos Vlsi Design 186Carlos SaavedraNo ratings yet

- Pitfalls and Fallacies: Targeting A Bleeding-Edge ProcessDocument1 pagePitfalls and Fallacies: Targeting A Bleeding-Edge ProcessCarlos SaavedraNo ratings yet

- CMOS VLSI Design 191Document1 pageCMOS VLSI Design 191Carlos SaavedraNo ratings yet

- Cmos Vlsi Design 207Document1 pageCmos Vlsi Design 207Carlos SaavedraNo ratings yet

- Manufacturing Issues: Antenna RulesDocument1 pageManufacturing Issues: Antenna RulesCarlos SaavedraNo ratings yet

- Logical Effort of Paths: A and C Begin To Rise (Figure 4.28 (C) ) - at First, Both Nodes See ApproximatelyDocument1 pageLogical Effort of Paths: A and C Begin To Rise (Figure 4.28 (C) ) - at First, Both Nodes See ApproximatelyCarlos SaavedraNo ratings yet

- 3.4.1.5 Plastic Transistors: InterconnectDocument1 page3.4.1.5 Plastic Transistors: InterconnectCarlos SaavedraNo ratings yet

- Cmos Vlsi Design 162Document1 pageCmos Vlsi Design 162Carlos SaavedraNo ratings yet

- CMOS VLSI Design 192Document1 pageCMOS VLSI Design 192Carlos SaavedraNo ratings yet

- Circuit Extraction: CONNECT Layer1 Layer2Document1 pageCircuit Extraction: CONNECT Layer1 Layer2Carlos SaavedraNo ratings yet

- 3.4.3.7 Non-Volatile Memory: P+ Diode N+ Well Contact Collector Base EmitterDocument1 page3.4.3.7 Non-Volatile Memory: P+ Diode N+ Well Contact Collector Base EmitterCarlos SaavedraNo ratings yet

- Layer Density Rules: Chapter 3 CMOS Processing TechnologyDocument1 pageLayer Density Rules: Chapter 3 CMOS Processing TechnologyCarlos SaavedraNo ratings yet

- (A) Diffusion Barrier Etch Stop (B) Via Dielectric (C) Line Dielectric (D) Anti-Reflective LayerDocument1 page(A) Diffusion Barrier Etch Stop (B) Via Dielectric (C) Line Dielectric (D) Anti-Reflective LayerCarlos SaavedraNo ratings yet

- 3.4 CMOS Process Enhancements: 3.4.3.3 InductorsDocument1 page3.4 CMOS Process Enhancements: 3.4.3.3 InductorsCarlos SaavedraNo ratings yet

- CMOS Processing Technology ChapterDocument1 pageCMOS Processing Technology ChapterCarlos SaavedraNo ratings yet

- CMOS Processing Technology Design RulesDocument1 pageCMOS Processing Technology Design RulesCarlos SaavedraNo ratings yet

- 3.4.1.2 Silicon On Insulator: Chapter 3 CMOS Processing TechnologyDocument1 page3.4.1.2 Silicon On Insulator: Chapter 3 CMOS Processing TechnologyCarlos SaavedraNo ratings yet

- Chapter 3 CMOS Processing Technology: 3.4.3.4 Transmission LinesDocument1 pageChapter 3 CMOS Processing Technology: 3.4.3.4 Transmission LinesCarlos SaavedraNo ratings yet

- Cmos Vlsi Design 149Document1 pageCmos Vlsi Design 149Carlos SaavedraNo ratings yet

- 3.4.1.4 Higher Mobility: High-K Gate Stack TEM (© IEEE 2007.)Document1 page3.4.1.4 Higher Mobility: High-K Gate Stack TEM (© IEEE 2007.)Carlos SaavedraNo ratings yet

- MOSIS Scalable CMOS Design RulesDocument1 pageMOSIS Scalable CMOS Design RulesCarlos SaavedraNo ratings yet

- Layout Design Rules for Integrated CircuitsDocument1 pageLayout Design Rules for Integrated CircuitsCarlos SaavedraNo ratings yet

- CMOS Processing Technology Chapter Details SRAM Cell Size ReductionDocument1 pageCMOS Processing Technology Chapter Details SRAM Cell Size ReductionCarlos SaavedraNo ratings yet

- CMOS Process Enhancements: Layer Rule Description 65 NM Rule (M) TABLE 3.1Document1 pageCMOS Process Enhancements: Layer Rule Description 65 NM Rule (M) TABLE 3.1Carlos SaavedraNo ratings yet

- Mask Summary: The Only Mask Involved With Contacts To Active or PolyDocument1 pageMask Summary: The Only Mask Involved With Contacts To Active or PolyCarlos SaavedraNo ratings yet

- Pioneer Deh p8650mp EspDocument154 pagesPioneer Deh p8650mp Espjupablo23No ratings yet

- Solar Water Pump DC Controller ManualDocument13 pagesSolar Water Pump DC Controller ManualAgustynho MagimbaNo ratings yet

- Interface Cables: Testing To PerfectionDocument3 pagesInterface Cables: Testing To PerfectionOmar Eduardo Corredor GómezNo ratings yet

- W342 E1 11+CS CJ CP+ReferenceManualDocument277 pagesW342 E1 11+CS CJ CP+ReferenceManualRyan Yudha AdhityaNo ratings yet

- Power at AC given by P = VI cosθDocument4 pagesPower at AC given by P = VI cosθJohn Paul BaquiranNo ratings yet

- A800 F800 EthernertDocument88 pagesA800 F800 EthernertAlberto Suazo BasaezNo ratings yet

- FC2060Document10 pagesFC2060esnNo ratings yet

- Flow Imaging Cardiac Ultrasound System: by Larry Miller PHDDocument28 pagesFlow Imaging Cardiac Ultrasound System: by Larry Miller PHDumarizkhNo ratings yet

- Split System Air Conditioner: KHS1822 / CH1822Document17 pagesSplit System Air Conditioner: KHS1822 / CH1822Marlou RabinaNo ratings yet

- 250XWE0000 (22 - 09 - 2016) MaximDocument201 pages250XWE0000 (22 - 09 - 2016) MaximcristiNo ratings yet

- Resume 1 Page RamDocument1 pageResume 1 Page RamRamnarayan ShreyasNo ratings yet

- BT 1500 PDFDocument54 pagesBT 1500 PDFnadeem hameedNo ratings yet

- Change region codes on multiple DVD player modelsDocument4 pagesChange region codes on multiple DVD player modelsJose Miguel Rodriguez CarreñoNo ratings yet

- OT100WUNV800C2DIMLT2P6Document10 pagesOT100WUNV800C2DIMLT2P6Ezequiel FregaNo ratings yet

- Pneumatics Module 4 Student VersionDocument12 pagesPneumatics Module 4 Student Versionziko23No ratings yet

- Student Verilog HDL LAB MANUAL FOR BE/B.TECH ECE STUDENTSDocument84 pagesStudent Verilog HDL LAB MANUAL FOR BE/B.TECH ECE STUDENTSSrikanth ImmaReddy100% (1)

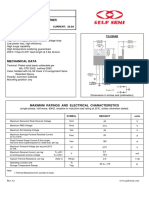

- SB2045CT: Schottky Barrier RectifierDocument2 pagesSB2045CT: Schottky Barrier RectifierNickol HardwayNo ratings yet

- 23-Page PLDocument20 pages23-Page PLmaharshahzadNo ratings yet

- Igbt Ltds Note eDocument1 pageIgbt Ltds Note eAndrew MaverickNo ratings yet

- Thin Film Deposition TechniquesDocument13 pagesThin Film Deposition TechniquesGaganpreetSinghNo ratings yet

- 0605 - Optimization of Spanning Tree AddersDocument39 pages0605 - Optimization of Spanning Tree AddersRaji PillalamarriNo ratings yet

- Playmates Tricorder Upgrade Instruction Manual-2020-01a (1)Document28 pagesPlaymates Tricorder Upgrade Instruction Manual-2020-01a (1)Rodger WeirNo ratings yet