Professional Documents

Culture Documents

Project 3-Differential CMOS Amplifier

Uploaded by

Hajra Swati0 ratings0% found this document useful (0 votes)

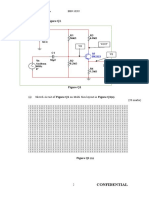

10 views2 pagesThis document provides instructions for designing a two-stage CMOS operational amplifier using MOSFETs with a power supply ranging from +/- 2.5V to +/- 0.9V depending on technology. A current mirror formed by Q5-Q8 supplies the differential pair Q1-Q2. Q3-Q4 are the active load for the first stage. The second stage is a common source amplifier Q6 with current source Q7. Feedback capacitor Cc is included for compensation. Simulation graphs are required for transistor Id vs Vg, voltage gains of each stage, CMRR, and output resistance along with design and summary tables.

Original Description:

Original Title

2 stage cmos amp

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document provides instructions for designing a two-stage CMOS operational amplifier using MOSFETs with a power supply ranging from +/- 2.5V to +/- 0.9V depending on technology. A current mirror formed by Q5-Q8 supplies the differential pair Q1-Q2. Q3-Q4 are the active load for the first stage. The second stage is a common source amplifier Q6 with current source Q7. Feedback capacitor Cc is included for compensation. Simulation graphs are required for transistor Id vs Vg, voltage gains of each stage, CMRR, and output resistance along with design and summary tables.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

10 views2 pagesProject 3-Differential CMOS Amplifier

Uploaded by

Hajra SwatiThis document provides instructions for designing a two-stage CMOS operational amplifier using MOSFETs with a power supply ranging from +/- 2.5V to +/- 0.9V depending on technology. A current mirror formed by Q5-Q8 supplies the differential pair Q1-Q2. Q3-Q4 are the active load for the first stage. The second stage is a common source amplifier Q6 with current source Q7. Feedback capacitor Cc is included for compensation. Simulation graphs are required for transistor Id vs Vg, voltage gains of each stage, CMRR, and output resistance along with design and summary tables.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 2

Project 3- Differential CMOS Amplifier

READ -HANDOUT on CHAPTER 8.

-Design a two-stage CMOS Op Amplifier with IC MOSFETs. Use a

two-stage configuration with two power supplies which can range from +/- 2.5 V for L= 0.8 μm

technology (to +/- 0.9 V for 0.18 μm technology).

IREF is generated either externally (or using on-chip CKT).

Current mirror formed by Q5-Q8 supplies differential pair Q1-Q2 with bias current.

The W/L of Q5 is selected to control I.

The diff pair is actively loaded by current mirror Q3-Q4.

Second stage is Q6 which is a CS amplifier for which Q7 is the current source.

A capacitor Cc is included for negative feedback to enhance the Miller effect through Q6 compensation.

This op amp does not have a low output impedance and is thus not suited for driving a low-impedance

load.

Design Table-hand calculations

The W/L ratios and other design values are given and listed below:

GRADING – ORCAD SIMULATION ONLY- graphs/probes must be original- no duplicate work. Use a separate

graph for each part:

A) Id and VG (V) for all transistors

B) Voltage gain at first stage

C) Voltage gain at second stage

D) CMRR of 2-statge amplifier

E) Rout

F) Summary Table I

G) Summery Table II

Table I

Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8

Id (uA)

VG (V)

Table II

Voltage Gain Voltage Gain CMRR Rout

at First Stage at Second Stage

Value

You might also like

- ENG 571 - Lecture - Notes - Weeks - 10 - 11Document23 pagesENG 571 - Lecture - Notes - Weeks - 10 - 11Md. Atiqul Haque ,160021010No ratings yet

- Week 4 Ch15 NotesDocument10 pagesWeek 4 Ch15 NotesDesan ScientistNo ratings yet

- Ea 1Document20 pagesEa 1SutantoNo ratings yet

- Electronic Circuit AnalysisDocument23 pagesElectronic Circuit AnalysisAnonymous uspYoqENo ratings yet

- Power Electronics Lab Manual PDFDocument16 pagesPower Electronics Lab Manual PDFBiradar ShivshankerNo ratings yet

- Power ElectronicsDocument16 pagesPower ElectronicsPerumal NamasivayamNo ratings yet

- Chapter-10 OP CircuitsDocument78 pagesChapter-10 OP CircuitsDebo LafuenteNo ratings yet

- Multistage AmplifiersDocument22 pagesMultistage AmplifiersParvinder SinghNo ratings yet

- BEC Question BankDocument5 pagesBEC Question BankDayanand NaikNo ratings yet

- 18EEL58Document39 pages18EEL58Rajendra VirajendraNo ratings yet

- R.D. Enggineering College, Duhai, GZB: Deptt. of Electronics & Communication EnggDocument3 pagesR.D. Enggineering College, Duhai, GZB: Deptt. of Electronics & Communication EnggMohan SinghNo ratings yet

- Lecture 3 Multistage AmplifiersDocument9 pagesLecture 3 Multistage AmplifiersAbdul SheikhNo ratings yet

- V, V, K U C W/L, V I, I, G, R: Unless Given SpecificallyDocument2 pagesV, V, K U C W/L, V I, I, G, R: Unless Given SpecificallyraghavbhatiaNo ratings yet

- Power Electronics Lab Manual For ECE (Vtu)Document87 pagesPower Electronics Lab Manual For ECE (Vtu)Sathish KumarNo ratings yet

- Modul Elda Ii Sem - 6 - 1Document7 pagesModul Elda Ii Sem - 6 - 1Jai YansenNo ratings yet

- TOBB University of Economics and TechnologyDocument4 pagesTOBB University of Economics and TechnologyBugrahan UstundagNo ratings yet

- EEEB273 N09 - Output Stages x6Document13 pagesEEEB273 N09 - Output Stages x6v6656No ratings yet

- A 7-Decades Tuning Range CMOS OTA-C Sinusoidal VCO: Teresa Serrano-Gotarredona and Bernabé Linares-BarrancoDocument4 pagesA 7-Decades Tuning Range CMOS OTA-C Sinusoidal VCO: Teresa Serrano-Gotarredona and Bernabé Linares-Barrancokaran007_mNo ratings yet

- Class BDocument5 pagesClass BAnonymous eWMnRr70qNo ratings yet

- PART A: Power Factor CorrectionDocument5 pagesPART A: Power Factor CorrectionShajedur RahmanNo ratings yet

- Power Electronics Lab ManualDocument72 pagesPower Electronics Lab Manualrajeshbv056135100% (3)

- Pe Lab Manual E&c Dept DsceDocument45 pagesPe Lab Manual E&c Dept DsceJeevan PreethuNo ratings yet

- John Mark A. Carpio Industrial Electronics Bsee-4A JANUARY 9, 2018Document14 pagesJohn Mark A. Carpio Industrial Electronics Bsee-4A JANUARY 9, 2018John Mark CarpioNo ratings yet

- Lab 3Document4 pagesLab 3J SarduaNo ratings yet

- Applied Electronics CH2Document7 pagesApplied Electronics CH2mesfin snowNo ratings yet

- TOBB ETU Department of ELE ELE 224L Electronic Circuits Experiment 3 - BJT AmplifiersDocument5 pagesTOBB ETU Department of ELE ELE 224L Electronic Circuits Experiment 3 - BJT AmplifiersBugrahan UstundagNo ratings yet

- Power Electronics Lab ManualDocument51 pagesPower Electronics Lab ManualArun DasNo ratings yet

- A Low-Power Decibel-Linear CMOS Automatiac Gain ControlDocument4 pagesA Low-Power Decibel-Linear CMOS Automatiac Gain ControlAlexandru StateNo ratings yet

- Power Electronics Lab ManualDocument28 pagesPower Electronics Lab ManualManjunath KalkutagiNo ratings yet

- Lab 5: Digital To Analog and Analog To Digital Converter: Telecommunication Electronics Laboratory Exercise 5Document7 pagesLab 5: Digital To Analog and Analog To Digital Converter: Telecommunication Electronics Laboratory Exercise 5Nilesh BhardwajNo ratings yet

- EE 202 Electronic Circuits Ii Experiment - 2 RC Coupled Two Stage BJT AmplifierDocument2 pagesEE 202 Electronic Circuits Ii Experiment - 2 RC Coupled Two Stage BJT AmplifiercancetinNo ratings yet

- A. DC Operation I. ObjectiveDocument9 pagesA. DC Operation I. ObjectivedummyNo ratings yet

- Confidential: Refer To Figure Q1Document3 pagesConfidential: Refer To Figure Q1Zhamir ZhakwanNo ratings yet

- Chap 6Document14 pagesChap 6YidnekachewNo ratings yet

- UC3848Document9 pagesUC3848Sergio Daniel BarretoNo ratings yet

- Ac MergedDocument486 pagesAc Mergedsanket panchalNo ratings yet

- 74aup2g79 Q100Document16 pages74aup2g79 Q100DaniNo ratings yet

- Lab 9 Common Emitter Amplifier: Department of Electrical EngineeringDocument7 pagesLab 9 Common Emitter Amplifier: Department of Electrical EngineeringKainat KhalidNo ratings yet

- Power Amplifier (Part 1)Document45 pagesPower Amplifier (Part 1)Ahmad FadliNo ratings yet

- Operating Manual For: Dual Source MeterDocument23 pagesOperating Manual For: Dual Source MeterilaaNo ratings yet

- ElectronicsII - Part I PDFDocument25 pagesElectronicsII - Part I PDFGlenn Paul PaceteNo ratings yet

- ElectronicsII Part IDocument25 pagesElectronicsII Part INaz KhanNo ratings yet

- BJTDocument18 pagesBJTMohd Nasrul Shafiq MnsNo ratings yet

- Power Electronics Lab Manual PDFDocument72 pagesPower Electronics Lab Manual PDFGopinath B L NaiduNo ratings yet

- MOS Op-Amp DesignDocument36 pagesMOS Op-Amp DesignPraseetha TvmNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Power Systems-On-Chip: Practical Aspects of DesignFrom EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNo ratings yet

- Advanced Control of AC / DC Power Networks: System of Systems Approach Based on Spatio-temporal ScalesFrom EverandAdvanced Control of AC / DC Power Networks: System of Systems Approach Based on Spatio-temporal ScalesNo ratings yet

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsFrom EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsNo ratings yet

- Exercises in Electronics: Operational Amplifier CircuitsFrom EverandExercises in Electronics: Operational Amplifier CircuitsRating: 3 out of 5 stars3/5 (1)

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsFrom EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsNo ratings yet

- ECA-2 Lab - 8 PDFDocument8 pagesECA-2 Lab - 8 PDFHajra SwatiNo ratings yet

- Manual Complex Engineering Problem: COMSATS University Islamabad Abbottabad CampusDocument35 pagesManual Complex Engineering Problem: COMSATS University Islamabad Abbottabad CampusHajra SwatiNo ratings yet

- Name:M.Umer Bin Tariq Registration No: FA19-EEE-070: - Experimental Proof of Thevenin's Theorem ObjectiveDocument7 pagesName:M.Umer Bin Tariq Registration No: FA19-EEE-070: - Experimental Proof of Thevenin's Theorem ObjectiveHajra SwatiNo ratings yet

- Math 351 Homework Problems Spring 2021, Professor RamrasDocument2 pagesMath 351 Homework Problems Spring 2021, Professor RamrasHajra SwatiNo ratings yet

- Wifi Motion Intelligence: The Fundamentals.: A Case Study by Telef Onica, Quantenna, and Aerial TechnologiesDocument7 pagesWifi Motion Intelligence: The Fundamentals.: A Case Study by Telef Onica, Quantenna, and Aerial TechnologiesHajra SwatiNo ratings yet

- Literature Review: 2.1 Hardware Oriented SecurityDocument43 pagesLiterature Review: 2.1 Hardware Oriented SecurityHajra SwatiNo ratings yet

- Chapter 9 Newton's MethodDocument27 pagesChapter 9 Newton's MethodHajra SwatiNo ratings yet

- Switch Parasitic Array Antenna For 5G Communication: COMSATS University Islamabad Abbottabad Campus-PakistanDocument55 pagesSwitch Parasitic Array Antenna For 5G Communication: COMSATS University Islamabad Abbottabad Campus-PakistanHajra SwatiNo ratings yet