Professional Documents

Culture Documents

60V Complementary Powertrench Mosfet: General Description Features

60V Complementary Powertrench Mosfet: General Description Features

Uploaded by

Eugene JayOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

60V Complementary Powertrench Mosfet: General Description Features

60V Complementary Powertrench Mosfet: General Description Features

Uploaded by

Eugene JayCopyright:

Available Formats

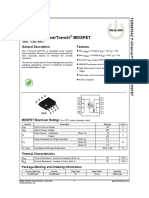

FDS4559

April 2002

FDS4559

60V Complementary PowerTrenchMOSFET

General Description Features

This complementary MOSFET device is produced using • Q1: N-Channel

Fairchild’s advanced PowerTrench process that has

been especially tailored to minimize the on-state 4.5 A, 60 V RDS(on) = 55 mΩ @ VGS = 10V

resistance and yet maintain low gate charge for RDS(on) = 75 mΩ @ VGS = 4.5V

superior switching performance.

• Q2: P-Channel

Applications

–3.5 A, –60 V RDS(on) = 105 mΩ @ VGS = –10V

• DC/DC converter

RDS(on) = 135 mΩ @ VGS = –4.5V

• Power management

• LCD backlight inverter

Q2

DD2 5 4

DD2

DD1 6 3

D1

D

Q1

7 2

SO-8 G2

S2 G

G1 S 8 1

S1 S

Pin 1 SO-8 S

Absolute Maximum Ratings TA = 25°C unless otherwise noted

Symbol Parameter Q1 Q2 Units

VDSS Drain-Source Voltage 60 –60 V

VGSS Gate-Source Voltage ±20 ±20 V

ID Drain Current - Continuous (Note 1a) 4.5 –3.5 A

- Pulsed 20 –20

PD Power Dissipation for Dual Operation 2 W

Power Dissipation for Single Operation (Note 1a) 1.6

(Note 1b) 1.2

(Note 1c) 1

TJ, TSTG Operating and Storage Junction Temperature Range -55 to +175 °C

Thermal Characteristics

RθJA Thermal Resistance, Junction-to-Ambient (Note 1a) 78 °C/W

RθJC Thermal Resistance, Junction-to-Case (Note 1) 40 °C/W

Package Marking and Ordering Information

Device Marking Device Reel Size Tape width Quantity

FDS4559 FDS4559 13” 12mm 2500 units

2000 Fairchild Semiconductor Corporation FDS4559 Rev C1(W)

FDS4559

Electrical Characteristics TA = 25°C unless otherwise noted

Symbol Parameter Test Conditions Type Min Typ Max Units

Drain-Source Avalanche Ratings (Note 1)

W DSS Single Pulse Drain-Source VDD = 30 V, ID = 4.5 A Q1 90 mJ

Avalanche Energy

IAR Maximum Drain-Source Q1 4.5 A

Avalanche Current

Off Characteristics

BVDSS Drain-Source Breakdown VGS = 0 V, ID = 250 µA Q1 60 V

Voltage VGS = 0 V, ID = –250 µA Q2 –60

∆BVDSS Breakdown Voltage ID = 250 µA, Referenced to 25°C Q1 58 mV/°C

∆TJ Temperature Coefficient ID = –250 µA, Referenced to 25°C Q2 –49

IDSS Zero Gate Voltage Drain VDS = 48 V, VGS = 0 V Q1 1 µA

Current VDS = –48 V, VGS = 0 V Q2 –1

IGSS Gate-Body Leakage VGS = +20 V, VDS = 0 V Q1 +100 nA

VGS = +20 V, VDS = 0 V Q2 +100

On Characteristics (Note 2)

VGS(th) Gate Threshold Voltage VDS = VGS, ID = 250 µA Q1 1 2.2 3 V

VDS = VGS, ID = –250 µA Q2 –1 –1.6 –3

∆VGS(th) Gate Threshold Voltage ID = 250 µA, Referenced to 25°C Q1 –5.5 mV/°C

∆TJ Temperature Coefficient ID = –250 µA, Referenced to 25°C Q2 4

RDS(on) Static Drain-Source VGS = 10 V, ID = 4.5 A Q1 42 55 mΩ

On-Resistance VGS = 10 V, ID = 4.5 A, TJ = 125°C 72 94

VGS = 4.5 V, ID = 4 A 55 75

VGS = –10 V, ID = –3.5 A Q2 82 105

VGS = –10 V, ID = –3.5 A, TJ = 125°C 130 190

VGS = –4.5 V, ID = –3.1 A 105 135

ID(on) On-State Drain Current VGS = 10 V, VDS = 5 V Q1 20 A

VGS = –10 V, VDS = –5 V Q2 –20

gFS Forward Transconductance VDS = 10 V, ID = 4.5 A Q1 14 S

VDS = –5 V, ID = –3 5 A Q2 9

Dynamic Characteristics

Ciss Input Capacitance Q1 Q1 650 pF

VDS = 25 V, VGS = 0 V, Q2 759

Coss Output Capacitance f = 1.0 MHz Q1 80 pF

Q2 Q2 90

Crss Reverse Transfer VDS = –30 V, VGS = 0 V, Q1 35 pF

Capacitance f = 1.0 MHz Q2 39

Switching Characteristics (Note 2)

td(on) Turn-On Delay Time Q1 Q1 11 20 ns

VDD = 30 V, ID = 1 A, Q2 7 14

tr Turn-On Rise Time VGS = 10V, RGEN = 6 Ω Q1 8 18 ns

Q2 10 20

td(off) Turn-Off Delay Time Q2 Q1 19 35 ns

VDD = –30 V, ID = –1 A, Q2 19 34

tf Turn-Off Fall Time VGS = –10 V, RGEN = 6 Ω Q1 6 15 ns

Q2 12 22

Qg Total Gate Charge Q1 Q1 12.5 18 nC

VDS = 30 V, ID = 4.5 A, VGS = 10 V Q2 15 21

Qgs Gate-Source Charge Q1 2.4 nC

Q2 Q2 2.5

Qgd Gate-Drain Charge VDS = –30 V, ID = –3.5 A, VGS = –10V Q1 2.6 nC

Q2 3.0

FDS4559 Rev C1(W)

FDS4559

Electrical Characteristics (continued) TA = 25°C unless otherwise noted

Symbol Parameter Test Conditions Type Min Typ Max Units

Drain-Source Diode Characteristics and Maximum Ratings

IS Maximum Continuous Drain-Source Diode Forward Current Q1 1.3 A

Q2 –1.3

VSD Drain-Source Diode Forward VGS = 0 V, IS = 1.3 A (Note 2) Q1 0.8 1.2 V

Voltage VGS = 0 V, IS = –1.3 A (Note 2) Q2 –0.8 –1.2

Notes:

1. RθJA is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of

the drain pins. RθJC is guaranteed by design while RθCA is determined by the user's board design.

a) 78°C/W when b) 125°C/W when c) 135°C/W when mounted on a

mounted on a mounted on a .02 in2 minimum pad.

0.5 in2 pad of 2 oz pad of 2 oz copper

copper

Scale 1 : 1 on letter size paper

2. Pulse Test: Pulse Width < 300µs, Duty Cycle < 2.0%

FDS4559 Rev C1(W)

FDS4559

Typical Characteristics: Q2

15 1.8

VGS = -10V

DRAIN-SOURCE ON-RESISTANCE

-6.0V -4.5V

VGS = -3.5V

12 -5.0V -4.0V 1.6

-ID, DRAIN CURRENT (A)

RDS(ON), NORMALIZED

-3.5V -4.0V

9 1.4

-4.5V

-5.0V

6 1.2

-6.0V

-3.0V -7.0V

-8.0V

-10V

3 1

-2.5V

0 0.8

0 1 2 3 4 5 0 2 4 6 8 10

-VDS, DRAIN-SOURCE VOLTAGE (V) -ID, DRAIN CURRENT (A)

Figure 1. On-Region Characteristics. Figure 2. On-Resistance Variation with

Drain Current and Gate Voltage.

2 0.4

DRAIN-SOURCE ON-RESISTANCE

ID = -3.5A

1.8

RDS(ON), ON-RESISTANCE (OHM)

VGS = -10V ID = -1.5A

1.6

RDS(ON), NORMALIZED

0.3

1.4

TA = 125oC

1.2 0.2

0.8 0.1

TA = 25oC

0.6

0.4 0

-50 -25 0 25 50 75 100 125 150 175 2 4 6 8 10

o

TJ, JUNCTION TEMPERATURE ( C) -VGS, GATE TO SOURCE VOLTAGE (V)

Figure 3. On-Resistance Variation with Figure 4. On-Resistance Variation with

Temperature. Gate-to-Source Voltage.

15 100

VDS = -5V TA = -55oC VGS = 0V

-IS, REVERSE DRAIN CURRENT (A)

25oC

12 10

-ID, DRAIN CURRENT (A)

125oC TA = 125oC

9 1 25oC

-55oC

6 0.1

3 0.01

0 0.001

1 2 3 4 5 0 0.2 0.4 0.6 0.8 1 1.2 1.4

-VGS, GATE TO SOURCE VOLTAGE (V) -VSD, BODY DIODE FORWARD VOLTAGE (V)

Figure 5. Transfer Characteristics. Figure 6. Body Diode Forward Voltage Variation

with Source Current and Temperature.

FDS4559 Rev C1(W)

FDS4559

Typical Characteristics: Q2

10 1200

ID = -3.0A VDS = 10V

-VGS, GATE-SOURCE VOLTAGE (V)

20V f = 1 MHz

1000 V GS = 0 V

8

30V

CAPACITANCE (pF)

800

6 C ISS

600

4

400

2

200

C RSS C OSS

0 0

0 4 8 12 16 0 10 20 30 40 50 60

Qg, GATE CHARGE (nC) -V DS , DRAIN TO SOURCE VOLTAGE (V)

Figure 7. Gate Charge Characteristics. Figure 8. Capacitance Characteristics.

100 40

P(pk), PEAK TRANSIENT POWER (W)

SINGLE PULSE

RθJA = 135°C/W

100µs

TA = 25°C

RDS(ON) LIMIT

ID, DRAIN CURRENT (A)

10 30

10ms

100ms

1 20

1s

10s

VGS = -10V

DC

SINGLE PULSE

0.1 10

RθJA = 135oC/W

TA = 25oC

0.01 0

0.1 1 10 100 0.01 0.1 1 10 100 1000

-VDS, DRAIN-SOURCE VOLTAGE (V) t1, TIME (sec)

Figure 9. Maximum Safe Operating Area. Figure 10. Single Pulse Maximum

Power Dissipation.

FDS4559 Rev C1(W)

FDS4559

Typical Characteristics: Q1

20 1.8

VGS = 10V

DRAIN-SOURCE ON-RESISTANCE

ID, DRAIN-SOURCE CURRENT (A)

6.0V 4.5V

16 1.6

RDS(ON), NORMALIZED

5.0V

VGS = 4.0V

4.0V

12 1.4

4.5V

5.0V

8 1.2

6.0V

8.0V

3.5V 10V

4 1

0 0.8

0 1 2 3 4 0 4 8 12 16 20

VDS, DRAIN-SOURCE VOLTAGE (V) ID, DRAIN CURRENT (A)

Figure 11. On-Region Characteristics. Figure 12. On-Resistance Variation with

Drain Current and Gate Voltage.

2.2 0.14

ID = 2.3A

ID = 4.5A

DRAIN-SOURCE ON-RESISTANCE

2 0.12

RDS(ON), ON-RESISTANCE (OHM)

VGS = 10V

1.8

RDS(ON), NORMALIZED

0.1

1.6

TA = 125oC

1.4 0.08

1.2 0.06

1

0.04 TA = 25oC

0.8

0.6 0.02

0.4

0

-50 -25 0 25 50 75 100 125 150 175

2 4 6 8 10

o

TJ, JUNCTION TEMPERATURE ( C) VGS, GATE TO SOURCE VOLTAGE (V)

Figure 13. On-Resistance Variation with Figure 14. On-Resistance Variation with

Temperature. Gate-to-Source Voltage.

20 100

TA = -55oC VGS = 0V

VDS = 5V 25oC

IS, REVERSE DRAIN CURRENT (A)

10

o

16 125 C

ID, DRAIN CURRENT (A)

TA = 125oC

1

12 25oC

0.1

-55oC

8

0.01

4 0.001

0.0001

0

0 0.2 0.4 0.6 0.8 1 1.2

1 2 3 4 5 6

VSD, BODY DIODE FORWARD VOLTAGE (V)

VGS, GATE TO SOURCE VOLTAGE (V)

Figure 15. Transfer Characteristics. Figure 16. Body Diode Forward Voltage Variation

with Source Current and Temperature.

FDS4559 Rev C1(W)

FDS4559

Typical Characteristics: Q1

10

ID = 4.5A VDS = 10V 900

VGS, GATE-SOURCE VOLTAGE (V)

f = 1MHz

20V 800

8 30V VGS = 0 V

700

CISS

CAPACITANCE (pF)

6 600

500

4 400

300

2 200

COSS

100

CRSS

0 0

0 2 4 6 8 10 12 14 0 10 20 30 40 50 60

Qg, GATE CHARGE (nC) VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 17. Gate Charge Characteristics. Figure 18. Capacitance Characteristics.

100 40

SINGLE PULSE

RDS(ON) LIMIT RθJA = 135oC/W

TA = 25oC

ID, DRAIN CURRENT (A)

10 100µs 30

1m

POWER (W)

10ms

1 100ms 20

1s

VGS= 10V DC

SINGLE PULSE

0.1 RθJA= 135oC/W 10

TA= 25oC

0.01 0

0.1 1 10 100 0.01 0.1 1 10 100 1000

VDS, DRAIN-SOURCE VOLTAGE (V) SINGLE PULSE TIME (SEC)

Figure 19. Maximum Safe Operating Area. Figure 20. Single Pulse Maximum

Power Dissipation.

TRANSIENT THERMAL RESISTANCE

1

r(t), NORMALIZED EFFECTIVE

D = 0.5

0.2

RθJA(t) = r(t) + RθJA

RθJA = 135°C/W

0.1 0.1

0.05

P(pk)

0.02

t1

0.01

0.01 t2

SINGLE PULSE

TJ - TA = P * RθJA(t)

Duty Cycle, D = t1 / t2

0.001

0.0001 0.001 0.01 0.1 1 10 100 1000

t1, TIME (sec)

Figure 21. Transient Thermal Response Curve.

Thermal characterization performed using the conditions described in Note 1c.

Transient thermal response will change depending on the circuit board design.

FDS4559 Rev C1(W)

TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is

not intended to be an exhaustive list of all such trademarks.

ACEx FAST â MICROWIRE SILENT SWITCHER â UHC

Bottomless FASTr OPTOLOGIC â SMART START UltraFET â

CoolFET FRFET OPTOPLANAR SPM VCX

CROSSVOLT GlobalOptoisolator PACMAN STAR*POWER

DenseTrench GTO POP Stealth

DOME HiSeC Power247 SuperSOT-3

EcoSPARK I2C PowerTrench â SuperSOT-6

E2CMOSTM ISOPLANAR QFET SuperSOT-8

EnSignaTM LittleFET QS SyncFET

FACT MicroFET QT Optoelectronics TinyLogic

FACT Quiet Series MicroPak Quiet Series TruTranslation

STAR*POWER is used under license

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER

NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD

DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT

OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT

RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or 2. A critical component is any component of a life

systems which, (a) are intended for surgical implant into support device or system whose failure to perform can

the body, or (b) support or sustain life, or (c) whose be reasonably expected to cause the failure of the life

failure to perform when properly used in accordance support device or system, or to affect its safety or

with instructions for use provided in the labeling, can be effectiveness.

reasonably expected to result in significant injury to the

user.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or This datasheet contains the design specifications for

In Design product development. Specifications may change in

any manner without notice.

Preliminary First Production This datasheet contains preliminary data, and

supplementary data will be published at a later date.

Fairchild Semiconductor reserves the right to make

changes at any time without notice in order to improve

design.

No Identification Needed Full Production This datasheet contains final specifications. Fairchild

Semiconductor reserves the right to make changes at

any time without notice in order to improve design.

Obsolete Not In Production This datasheet contains specifications on a product

that has been discontinued by Fairchild semiconductor.

The datasheet is printed for reference information only.

Rev. H5

You might also like

- NT Siemens Sid902 Ford 1033Document3 pagesNT Siemens Sid902 Ford 1033Roni Socompi100% (1)

- Checklist For Internal Safety Audit - OISD-145Document4 pagesChecklist For Internal Safety Audit - OISD-145jai-shriram100% (1)

- Dual 30V P-Channel Powertrench Mosfet: General Description FeaturesDocument5 pagesDual 30V P-Channel Powertrench Mosfet: General Description FeaturesLuis AntunesNo ratings yet

- FDS8958Document8 pagesFDS8958Fabio NevesNo ratings yet

- c9945 TermokingDocument7 pagesc9945 TermokingNelson CabelloNo ratings yet

- Fdw9926A: Dual N-Channel 2.5V Specified Powertrench MosfetDocument5 pagesFdw9926A: Dual N-Channel 2.5V Specified Powertrench MosfetbilarodrigoNo ratings yet

- 4435 FairchildSemiconductorDocument6 pages4435 FairchildSemiconductorYared TarikuNo ratings yet

- Fds 9953 ADocument6 pagesFds 9953 AМирослава НиколенкоNo ratings yet

- Fds 9933 ADocument5 pagesFds 9933 Aasasdassdfdf asdfasdsdfsfsdNo ratings yet

- FDS7296N3 - 30V N-Channel PowerTrench MOSFETDocument7 pagesFDS7296N3 - 30V N-Channel PowerTrench MOSFETLangllyNo ratings yet

- Dual P-Channel Powertrench Mosfet: November 2008Document6 pagesDual P-Channel Powertrench Mosfet: November 2008Gedealdo TorresNo ratings yet

- Datasheet - HK Fds9431a10 4643859Document5 pagesDatasheet - HK Fds9431a10 4643859jim campbellNo ratings yet

- Nds 9435 ADocument5 pagesNds 9435 Ajonathan ramos lopezNo ratings yet

- Si4435Dy: 30V P-Channel Powertrench MosfetDocument5 pagesSi4435Dy: 30V P-Channel Powertrench MosfetBedjo TjahmricanNo ratings yet

- Fds6679Az P-Channel Powertrench Mosfet: - 30V, - 13A, 9M General Description FeaturesDocument6 pagesFds6679Az P-Channel Powertrench Mosfet: - 30V, - 13A, 9M General Description FeaturesEdgxr DxnielNo ratings yet

- P-Channel 2.5V Specified Powertrench Mosfet: General Description FeaturesDocument5 pagesP-Channel 2.5V Specified Powertrench Mosfet: General Description FeaturesNagaraju NSNo ratings yet

- FDS9435A FairchildSemiconductorDocument6 pagesFDS9435A FairchildSemiconductormuhammad FikriNo ratings yet

- FDC6312PDocument5 pagesFDC6312PsbrhomeNo ratings yet

- FDS6990ASDocument8 pagesFDS6990ASal.aliefzainiiNo ratings yet

- Ic Dual Channel - FDS6982-79262Document10 pagesIc Dual Channel - FDS6982-79262BryanJermyHendrikNo ratings yet

- FDS6930 PDFDocument5 pagesFDS6930 PDFTut MorisNo ratings yet

- Asymmetric Dual N-Channel MOSFET FDMS3606SDocument16 pagesAsymmetric Dual N-Channel MOSFET FDMS3606SopenstorebussinesNo ratings yet

- Fds6690As: 30V N-Channel Powertrench SyncfetDocument8 pagesFds6690As: 30V N-Channel Powertrench SyncfetManuel LeaNo ratings yet

- FDMS3600S FairchildSemiconductorDocument16 pagesFDMS3600S FairchildSemiconductorvinuNo ratings yet

- Fds6690A: Single N-Channel, Logic-Level, Powertrench MosfetDocument6 pagesFds6690A: Single N-Channel, Logic-Level, Powertrench MosfetDenis SilvaNo ratings yet

- Fds6690A: Single N-Channel, Logic-Level, Powertrench MosfetDocument6 pagesFds6690A: Single N-Channel, Logic-Level, Powertrench Mosfetmuhammad atifNo ratings yet

- Fdd5614P: 60V P-Channel Powertrench MosfetDocument6 pagesFdd5614P: 60V P-Channel Powertrench MosfetAmaury jrNo ratings yet

- Fds6612A: Single N-Channel, Logic-Level, Powertrench MosfetDocument8 pagesFds6612A: Single N-Channel, Logic-Level, Powertrench MosfetCarlos Manuel PeraltaNo ratings yet

- Fds6680as 106791Document9 pagesFds6680as 106791Mhd DamNo ratings yet

- Onsemiconductor Nds8410a Datasheets 3577Document5 pagesOnsemiconductor Nds8410a Datasheets 3577Google EyeNo ratings yet

- FDS6679AZ DatasheetDocument6 pagesFDS6679AZ DatasheetMarivaldo NascimentoNo ratings yet

- Fdd6680 / Fdu6680: 30V N-Channel Powertrench MosfetDocument6 pagesFdd6680 / Fdu6680: 30V N-Channel Powertrench Mosfetmarcelo giussaniNo ratings yet

- Fds 6875Document5 pagesFds 6875dreyes3773No ratings yet

- Fds6982S: Dual Notebook Power Supply N-Channel Powertrench SyncfetDocument9 pagesFds6982S: Dual Notebook Power Supply N-Channel Powertrench SyncfetManuel LeaNo ratings yet

- Onsemiconductor Fds6679az Datasheets 0664Document6 pagesOnsemiconductor Fds6679az Datasheets 0664Yohandris FernandezNo ratings yet

- Fds6676As: 30V N-Channel Powertrench SyncfetDocument8 pagesFds6676As: 30V N-Channel Powertrench SyncfetManuel LeaNo ratings yet

- 161 5 003187 FDD6685Document6 pages161 5 003187 FDD6685Marcos Paulo FariaNo ratings yet

- ST p14nf12 PDFDocument15 pagesST p14nf12 PDFwertingoNo ratings yet

- Fairchild - Semiconductor FDC5614P DatasheetDocument5 pagesFairchild - Semiconductor FDC5614P DatasheetStelian DobreNo ratings yet

- Fds6975 Dual P-Channel, Logic Level, Powertrench MosfetDocument8 pagesFds6975 Dual P-Channel, Logic Level, Powertrench MosfetAbdul KurniadiNo ratings yet

- FDS6975Document5 pagesFDS6975sweet boy play boyNo ratings yet

- 294937Document8 pages294937พ่อโกรธ พ่อต้องยิ้มNo ratings yet

- Fds6575 Single P-Channel, Logic Level, Powertrench MosfetDocument8 pagesFds6575 Single P-Channel, Logic Level, Powertrench MosfetsilictronicNo ratings yet

- Si4925Dy Dual P-Channel, Logic Level, Powertrench Mosfet: January 2001Document6 pagesSi4925Dy Dual P-Channel, Logic Level, Powertrench Mosfet: January 2001Julio Hernandez MateoNo ratings yet

- Mosfet: NTD5802N, NVD5802N - Power, Single, N-Channel, DPAKDocument7 pagesMosfet: NTD5802N, NVD5802N - Power, Single, N-Channel, DPAKPusong BatoNo ratings yet

- General Description Product Summary: 30V Dual Asymmetric N-Channel MOSFETDocument10 pagesGeneral Description Product Summary: 30V Dual Asymmetric N-Channel MOSFETseborgNo ratings yet

- Fdms3660S: Powertrench Power StageDocument15 pagesFdms3660S: Powertrench Power StageMax Assistência TécnicaNo ratings yet

- P06VDocument7 pagesP06VMauro BusciglioNo ratings yet

- FDD6680ADocument6 pagesFDD6680AEdson HenriqueNo ratings yet

- NDS9955 Dual N-Channel Enhancement Mode Field Effect TransistorDocument9 pagesNDS9955 Dual N-Channel Enhancement Mode Field Effect TransistorMahdi RayNo ratings yet

- Fds6681Z: 30 Volt P-Channel Powertrench MosfetDocument6 pagesFds6681Z: 30 Volt P-Channel Powertrench MosfetShamim DhaliNo ratings yet

- fdw2506p RC FairchildDocument6 pagesfdw2506p RC FairchildMaxNo ratings yet

- APM4546Document13 pagesAPM4546Ridho MawardiNo ratings yet

- Is Now Part ofDocument11 pagesIs Now Part offefoheavymetalNo ratings yet

- Fdms7698: N-Channel Powertrench MosfetDocument7 pagesFdms7698: N-Channel Powertrench MosfetAdrian Kim BabelaNo ratings yet

- Fdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MDocument5 pagesFdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MfaberjetNo ratings yet

- Fds6690A Single N-Channel, Logic Level, Powertrench MosfetDocument8 pagesFds6690A Single N-Channel, Logic Level, Powertrench MosfetEsmir MarinNo ratings yet

- General Description Product Summary: 30V Dual Asymmetric N-Channel MOSFETDocument10 pagesGeneral Description Product Summary: 30V Dual Asymmetric N-Channel MOSFETErnesto PuenteNo ratings yet

- FQB5N60CDocument9 pagesFQB5N60CadilsonmagnNo ratings yet

- N-Channel Powertrench Mosfet: 30V, 7A, 23M General Description FeaturesDocument6 pagesN-Channel Powertrench Mosfet: 30V, 7A, 23M General Description FeaturesLuis CarlosNo ratings yet

- 4511GM-Advanced Power ElectronicsDocument7 pages4511GM-Advanced Power ElectronicsShames ElhoryaNo ratings yet

- Lmx24-N, Lm2902-N Low-Power, Quad-Operational Amplifiers: 1 Features 3 DescriptionDocument38 pagesLmx24-N, Lm2902-N Low-Power, Quad-Operational Amplifiers: 1 Features 3 DescriptionRoni SocompiNo ratings yet

- Body Control System: SectionDocument51 pagesBody Control System: SectionRoni SocompiNo ratings yet

- D1264Document2 pagesD1264Roni SocompiNo ratings yet

- Engine Cooling System: SectionDocument61 pagesEngine Cooling System: SectionRoni SocompiNo ratings yet

- Toshiba: TC551001BPL/BFL/BFTL/BTRL-70L/85LDocument13 pagesToshiba: TC551001BPL/BFL/BFTL/BTRL-70L/85LRoni SocompiNo ratings yet

- U 1520 Cat DiodeDocument2 pagesU 1520 Cat DiodeRoni SocompiNo ratings yet

- 256/128 Kbit Serial I C Bus EEPROM Without Chip Enable LinesDocument16 pages256/128 Kbit Serial I C Bus EEPROM Without Chip Enable LinesRoni Socompi100% (1)

- HM628128D Series: 1 M SRAM (128-Kword 8-Bit)Document20 pagesHM628128D Series: 1 M SRAM (128-Kword 8-Bit)Roni SocompiNo ratings yet

- Scaneo Ecu d13Document3 pagesScaneo Ecu d13Roni Socompi100% (1)

- MHDocument132 pagesMHRoni Socompi100% (1)

- PV776-88951780 - Mid 144 PDFDocument22 pagesPV776-88951780 - Mid 144 PDFRoni Socompi100% (2)

- GFT 87aDocument6 pagesGFT 87aRoni SocompiNo ratings yet

- Tecmo World Cup SoccerDocument11 pagesTecmo World Cup SoccerRoni SocompiNo ratings yet

- Service Manual Trucks: Windshield Wiper System VN, VHDDocument56 pagesService Manual Trucks: Windshield Wiper System VN, VHDRoni SocompiNo ratings yet

- Motorola M930/M930NAV In-Vehicle Phone: User GuideDocument64 pagesMotorola M930/M930NAV In-Vehicle Phone: User GuideRoni SocompiNo ratings yet

- Service Manual Trucks: Windshield Wiper System VN, VHDDocument56 pagesService Manual Trucks: Windshield Wiper System VN, VHDRoni SocompiNo ratings yet

- Effects of Temperature On Diode ApplicationsDocument15 pagesEffects of Temperature On Diode ApplicationsWilliam OtabilNo ratings yet

- NYY 0.6/1 (1.2) KV: SPLN 43-1/IEC 60502-1Document1 pageNYY 0.6/1 (1.2) KV: SPLN 43-1/IEC 60502-1FerdiNo ratings yet

- Panasonic TX-29PM1 - CP521Document21 pagesPanasonic TX-29PM1 - CP521Florin CostinNo ratings yet

- Comprehensive Review and Comparison of Single-Phase Grid-Tied Photovoltaic MicroinvertersDocument19 pagesComprehensive Review and Comparison of Single-Phase Grid-Tied Photovoltaic MicroinvertersJesus Alonso DiazNo ratings yet

- Stick Diagrams by S.N.bhat, Lecturer, Dept of EC Engg., M.I.T ...Document19 pagesStick Diagrams by S.N.bhat, Lecturer, Dept of EC Engg., M.I.T ...arthy_mariappan3873No ratings yet

- Electrical Machines IDocument6 pagesElectrical Machines IKrishna Reddy SvvsNo ratings yet

- DC 12V To 220V Ac Inverter Making by Using Ic CD4047Document19 pagesDC 12V To 220V Ac Inverter Making by Using Ic CD4047Amartya RoyNo ratings yet

- OW - Indoor Disconnector: Safety and Protection of Personnel and AssetsDocument2 pagesOW - Indoor Disconnector: Safety and Protection of Personnel and AssetsSFGRISELDA SANCHEZNo ratings yet

- DVD SmpsDocument3 pagesDVD SmpsGendil FatheNo ratings yet

- ACG StarterDocument9 pagesACG StarterAnggi RustandiNo ratings yet

- Ent Microdebrider 24v b0512n4080 SpecificationsDocument1 pageEnt Microdebrider 24v b0512n4080 SpecificationsIman AzrbjNo ratings yet

- Electrical Machines Lab Manual (DC Machines and Transformer)Document34 pagesElectrical Machines Lab Manual (DC Machines and Transformer)AmulyaNo ratings yet

- Design of Motor Control CenterDocument8 pagesDesign of Motor Control CenterbhaveshbhoiNo ratings yet

- HLB1VHYJHFXXXXbtXpXX PRXFXXXPDocument10 pagesHLB1VHYJHFXXXXbtXpXX PRXFXXXPTauseef AlamNo ratings yet

- Transistors ApplicationsDocument28 pagesTransistors ApplicationsShahir Afif IslamNo ratings yet

- Feeder Protection Relay FormatDocument4 pagesFeeder Protection Relay FormatUmapathiNo ratings yet

- DC MotorDocument54 pagesDC MotorGerard AlfonsoNo ratings yet

- 10 ElectricityDocument22 pages10 Electricity이다연No ratings yet

- Sinamics g120 Ac DrivesDocument10 pagesSinamics g120 Ac DrivesPandu Birumakovela0% (1)

- Micrilogic 2.0 5.0 6.0 PDFDocument24 pagesMicrilogic 2.0 5.0 6.0 PDFJohan MayaNo ratings yet

- Zephyr 20S Spare Parts ManualDocument42 pagesZephyr 20S Spare Parts Manualmircomirco100% (1)

- Brilliance Air 6-10-16 Manual 3Document27 pagesBrilliance Air 6-10-16 Manual 3Karthick BalakrishnanNo ratings yet

- Finder Relays Series 60 PDFDocument6 pagesFinder Relays Series 60 PDFElenilson SampaioNo ratings yet

- Inspection Sheet GensetDocument2 pagesInspection Sheet GensetDwiNo ratings yet

- Max. 18 W: AC/DC Power Supplies - Linear - RegulatedDocument1 pageMax. 18 W: AC/DC Power Supplies - Linear - RegulatedPeterNo ratings yet

- Interactive Schematic: This Document Is Best Viewed at A Screen Resolution of 1024 X 768Document26 pagesInteractive Schematic: This Document Is Best Viewed at A Screen Resolution of 1024 X 768Luis EnriqueNo ratings yet

- 132 KV GSS Training ReportDocument35 pages132 KV GSS Training ReportTREGIC FUN100% (2)

- Restricted Earth Fault Relay-AHQDocument4 pagesRestricted Earth Fault Relay-AHQEnpak ArsalanNo ratings yet

- Avea 20190627Document2 pagesAvea 20190627Blue StacksNo ratings yet