Professional Documents

Culture Documents

FDC6312P

Uploaded by

sbrhomeCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

FDC6312P

Uploaded by

sbrhomeCopyright:

Available Formats

FDC6312P

January 2001

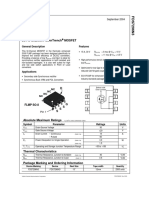

FDC6312P

Dual P-Channel 1.8V PowerTrench Specified MOSFET

General Description Features

These P-Channel 1.8V specified MOSFETs are • –2.3 A, –20 V. RDS(ON) = 115 mΩ @ VGS = –4.5 V

produced using Fairchild Semiconductor's advanced

PowerTrench process that has been especially tailored RDS(ON) = 155 mΩ @ VGS = –2.5 V

to minimize on-state resistance and yet maintain low RDS(ON) = 225 mΩ @ VGS = –1.8 V

gate charge for superior switching performance.

• High performance trench technology for extremely

Applications low RDS(ON)

• Power management

• SuperSOTTM-6 package: small footprint (72%

• Load switch smaller than standard SO-8); low profile (1mm thick)

D2

S1 4 3

D1

5 2

G2

S2 6 1

TM

SuperSOT -6 G1

Absolute Maximum Ratings TA=25oC unless otherwise noted

Symbol Parameter Ratings Units

VDSS Drain-Source Voltage –20 V

VGSS Gate-Source Voltage ±8 V

ID Drain Current – Continuous (Note 1a) –2.3 A

– Pulsed –7

PD Power Dissipation for Single Operation (Note 1a) 0.96 W

(Note 1b) 0.9

(Note 1c) 0.7

TJ, TSTG Operating and Storage Junction Temperature Range -55 to +150 °C

Thermal Characteristics

RθJA Thermal Resistance, Junction-to-Ambient (Note 1a) 130 °C/W

RθJC Thermal Resistance, Junction-to-Case (Note 1) 60 °C/W

Package Marking and Ordering Information

Device Marking Device Reel Size Tape width Quantity

.312 FDC6312P 13’’ 12mm 3000 units

2001 Fairchild Semiconductor Corporation FDC6312P Rev C (W)

FDC6312P

Electrical Characteristics TA = 25°C unless otherwise noted

Symbol Parameter Test Conditions Min Typ Max Units

Off Characteristics

BVDSS Drain–Source Breakdown Voltage VGS = 0 V, ID = –250 µA –20 V

∆BVDSS Breakdown Voltage Temperature

ID = –250 µA,Referenced to 25°C –11 mV/°C

∆TJ Coefficient

IDSS Zero Gate Voltage Drain Current VDS = –16 V, VGS = 0 V –1 µA

IGSSF Gate–Body Leakage, Forward VGS = 8 V, VDS = 0 V 100 nA

IGSSR Gate–Body Leakage, Reverse VGS = –8 V, VDS = 0 V –100 nA

On Characteristics (Note 2)

VGS(th) Gate Threshold Voltage VDS = VGS, ID = –250 µA –0.4 –0.9 –1.5 V

∆VGS(th) Gate Threshold Voltage ID = –250 µA,Referenced to 25°C

2 mV/°C

∆TJ Temperature Coefficient

RDS(on) Static Drain–Source VGS = –4.5 V, ID = –2.3 A 92 115 mΩ

On–Resistance VGS = –2.5 V, ID = –1.9 A 116 155

VGS = –1.8 V, ID = –1.6 A 166 225

VGS=–4.5 V, ID =–2.3A, TJ=125°C 112 150

ID(on) On–State Drain Current VGS = –4.5 V, VDS = –5 V –7 A

gFS Forward Transconductance VDS = –5 V, ID = –3.5 A 5.3 S

Dynamic Characteristics

Ciss Input Capacitance VDS = –10 V, V GS = 0 V, 467 pF

Coss Output Capacitance f = 1.0 MHz 85 pF

Crss Reverse Transfer Capacitance 38 pF

Switching Characteristics (Note 2)

td(on) Turn–On Delay Time VDD = –10 V, ID = –1 A, 8 16 ns

tr Turn–On Rise Time VGS = –4.5 V, RGEN = 6 Ω 13 23 ns

td(off) Turn–Off Delay Time 18 32 ns

tf Turn–Off Fall Time 8 16 ns

Qg Total Gate Charge VDS = –10 V, ID = –2.3 A, 4.4 7 nC

Qgs Gate–Source Charge VGS = –4.5 V 1.0 nC

Qgd Gate–Drain Charge 0.8 nC

Drain–Source Diode Characteristics and Maximum Ratings

IS Maximum Continuous Drain–Source Diode Forward Current –0.8 A

Drain–Source Diode Forward

VSD VGS = 0 V, IS = –0.8 A (Note 2) –0.7 –1.2 V

Voltage

Notes:

1. RθJA is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of

the drain pins. RθJC is guaranteed by design while RθCA is determined by the user's board design.

a) 130 °C/W when

b) 140°/W when mounted

mounted on a 0.125 c) 180°/W when mounted on a

on a .004 in2 pad of 2 oz

in2 pad of 2 oz. minimum pad.

copper

copper.

Scale 1 : 1 on letter size paper

2. Pulse Test: Pulse Width < 300µs, Duty Cycle < 2.0%

FDC6312P Rev C (W)

FDS6312P

Typical Characteristics

6 2.5

VGS = -4.5V

DRAIN-SOURCE ON-RESISTANCE

-3.0V 2.25

5 -3.5V VGS = -1.8V

-ID, DRAIN CURRENT (A)

RDS(ON), NORMALIZED

-2.5V

2

4

-2.0V

1.75

-2.0V

3

1.5

-1.8V

-2.5V

2 1.25 -3.0V

-3.5V

1 1 -4.5V

-1.5V

0.75

0

0 1 2 3 4 5 6

0 0.5 1 1.5 2 2.5

-ID, DRAIN CURRENT (A)

-VDS, DRAIN-SOURCE VOLTAGE (V)

Figure 1. On-Region Characteristics. Figure 2. On-Resistance Variation with

Drain Current and Gate Voltage.

1.6 0.35

ID = -2.3A

ID = -0.8 A

DRAIN-SOURCE ON-RESISTANCE

VGS =-4.5V

RDS(ON), ON-RESISTANCE (OHM)

0.3

1.4

RDS(ON), NORMALIZED

0.25

1.2

0.2

1 TA = 125oC

0.15

0.8

0.1

TA = 25oC

0.6

0.05

-50 -25 0 25 50 75 100 125 150

1 2 3 4 5

TJ, JUNCTION TEMPERATURE (oC) -VGS, GATE TO SOURCE VOLTAGE (V)

Figure 3. On-Resistance Variation with Figure 4. On-Resistance Variation with

Temperature. Gate-to-Source Voltage.

6 10

VGS = 0V

TA = -55oC

-IS, REVERSE DRAIN CURRENT (A)

VDS = 5V 25oC

5 1

TA = 125oC

-ID, DRAIN CURRENT (A)

125oC

4 25oC

0.1

-55oC

3

0.01

2

0.001

1

0.0001

0

0 0.2 0.4 0.6 0.8 1 1.2

0.5 1 1.5 2 2.5 3

-VSD, BODY DIODE FORWARD VOLTAGE (V)

-VGS, GATE TO SOURCE VOLTAGE (V)

Figure 5. Transfer Characteristics. Figure 6. Body Diode Forward Voltage Variation

with Source Current and Temperature.

FDC6312P Rev C (W)

FDS6312P

Typical Characteristics

5 700

ID = -2.3A VDS = -5V f = 1MHz

-VGS, GATE-SOURCE VOLTAGE (V)

-10V 600 VGS = 0 V

4

-15V

CAPACITANCE (pF)

500

CISS

3

400

300

2

200

1

100 COSS

CRSS

0 0

0 1 2 3 4 5 6 0 5 10 15 20

Qg, GATE CHARGE (nC) -VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 7. Gate Charge Characteristics. Figure 8. Capacitance Characteristics.

100 5

P(pk), PEAK TRANSIENT POWER (W)

SINGLE PULSE

4 RθJA = 180°C/W

-ID, DRAIN CURRENT (A)

10 1ms TA = 25°C

RDS(ON) LIMIT

10ms

100ms 3

1s

1

10s

DC 2

VGS = -4.5V

SINGLE PULSE

0.1

RθJA = 180oC/W 1

TA = 25oC

0.01 0

0.1 1 10 100 0.01 0.1 1 10 100 1000

-VDS, DRAIN-SOURCE VOLTAGE (V) t1, TIME (sec)

Figure 9. Maximum Safe Operating Area. Figure 10. Single Pulse Maximum

Power Dissipation.

1

TRANSIENT THERMAL RESISTANCE

D = 0.5

r(t), NORMALIZED EFFECTIVE

0.2 RθJA(t) = r(t) + RθJA

RθJA = 180°C/W

0.1 0.1

0.05

0.02

P(pk)

0.01 t1

0.01 t2

SINGLE PULSE

TJ - TA = P * RθJA(t)

Duty Cycle, D = t1 / t2

0.001

0.0001 0.001 0.01 0.1 1 10 100 1000

t1, TIME (sec)

Figure 11. Transient Thermal Response Curve.

Thermal characterization performed using the conditions described in Note 1c.

Transient thermal response will change depending on the circuit board design.

FDC6312P Rev C (W)

TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is

not intended to be an exhaustive list of all such trademarks.

ACEx™ FAST OPTOLOGIC™ SMART START™ VCX™

Bottomless™ FASTr™ OPTOPLANAR™ STAR*POWER™

CoolFET™ FRFET™ PACMAN™ Stealth™

CROSSVOLT™ GlobalOptoisolator™ POP™ SuperSOT™-3

DenseTrench™ GTO™ Power247™ SuperSOT™-6

DOME™ HiSeC™ PowerTrench SuperSOT™-8

EcoSPARK™ ISOPLANAR™ QFET™ SyncFET™

E2CMOSTM LittleFET™ QS™ TinyLogic™

EnSignaTM MicroFET™ QT Optoelectronics™ TruTranslation™

FACT™ MicroPak™ Quiet Series™ UHC™

FACT Quiet Series™ MICROWIRE™ SILENT SWITCHER UltraFET

STAR*POWER is used under license

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER

NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD

DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT

OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT

RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or 2. A critical component is any component of a life

systems which, (a) are intended for surgical implant into support device or system whose failure to perform can

the body, or (b) support or sustain life, or (c) whose be reasonably expected to cause the failure of the life

failure to perform when properly used in accordance support device or system, or to affect its safety or

with instructions for use provided in the labeling, can be effectiveness.

reasonably expected to result in significant injury to the

user.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or This datasheet contains the design specifications for

In Design product development. Specifications may change in

any manner without notice.

Preliminary First Production This datasheet contains preliminary data, and

supplementary data will be published at a later date.

Fairchild Semiconductor reserves the right to make

changes at any time without notice in order to improve

design.

No Identification Needed Full Production This datasheet contains final specifications. Fairchild

Semiconductor reserves the right to make changes at

any time without notice in order to improve design.

Obsolete Not In Production This datasheet contains specifications on a product

that has been discontinued by Fairchild semiconductor.

The datasheet is printed for reference information only.

Rev. H4

You might also like

- fdw2506p RC FairchildDocument6 pagesfdw2506p RC FairchildMaxNo ratings yet

- Fdw9926A: Dual N-Channel 2.5V Specified Powertrench MosfetDocument5 pagesFdw9926A: Dual N-Channel 2.5V Specified Powertrench MosfetbilarodrigoNo ratings yet

- Fdc658P Single P-Channel, Logic Level, Powertrench Mosfet: General Description FeaturesDocument5 pagesFdc658P Single P-Channel, Logic Level, Powertrench Mosfet: General Description Featuresgabriel6276No ratings yet

- P-Channel 2.5V Specified Powertrench Mosfet: General Description FeaturesDocument5 pagesP-Channel 2.5V Specified Powertrench Mosfet: General Description FeaturesNagaraju NSNo ratings yet

- Onsemiconductor Fds6679az Datasheets 0664Document6 pagesOnsemiconductor Fds6679az Datasheets 0664Yohandris FernandezNo ratings yet

- FDS6975Document5 pagesFDS6975sweet boy play boyNo ratings yet

- Fds6975 Dual P-Channel, Logic Level, Powertrench MosfetDocument8 pagesFds6975 Dual P-Channel, Logic Level, Powertrench MosfetAbdul KurniadiNo ratings yet

- Fds6679Az P-Channel Powertrench Mosfet: - 30V, - 13A, 9M General Description FeaturesDocument6 pagesFds6679Az P-Channel Powertrench Mosfet: - 30V, - 13A, 9M General Description FeaturesEdgxr DxnielNo ratings yet

- Fds 6875Document5 pagesFds 6875dreyes3773No ratings yet

- Fdc642P: Single P-Channel 2.5V Specified Powertrench MosfetDocument5 pagesFdc642P: Single P-Channel 2.5V Specified Powertrench MosfetdistefanoNo ratings yet

- NDS9955 Dual N-Channel Enhancement Mode Field Effect TransistorDocument9 pagesNDS9955 Dual N-Channel Enhancement Mode Field Effect TransistorMahdi RayNo ratings yet

- Fairchild - Semiconductor FDC5614P DatasheetDocument5 pagesFairchild - Semiconductor FDC5614P DatasheetStelian DobreNo ratings yet

- Si4925Dy Dual P-Channel, Logic Level, Powertrench Mosfet: January 2001Document6 pagesSi4925Dy Dual P-Channel, Logic Level, Powertrench Mosfet: January 2001Julio Hernandez MateoNo ratings yet

- Fds6681Z: 30 Volt P-Channel Powertrench MosfetDocument6 pagesFds6681Z: 30 Volt P-Channel Powertrench MosfetShamim DhaliNo ratings yet

- FDS6679AZ DatasheetDocument6 pagesFDS6679AZ DatasheetMarivaldo NascimentoNo ratings yet

- Fdn358P: Single P-Channel, Logic Level, Powertrench MosfetDocument5 pagesFdn358P: Single P-Channel, Logic Level, Powertrench MosfetAlex KarimNo ratings yet

- N-Channel Powertrench Mosfet: 30V, 7A, 23M General Description FeaturesDocument6 pagesN-Channel Powertrench Mosfet: 30V, 7A, 23M General Description FeaturesLuis CarlosNo ratings yet

- 294937Document8 pages294937พ่อโกรธ พ่อต้องยิ้มNo ratings yet

- Fds6575 Single P-Channel, Logic Level, Powertrench MosfetDocument8 pagesFds6575 Single P-Channel, Logic Level, Powertrench MosfetsilictronicNo ratings yet

- Fds6612A: Single N-Channel, Logic-Level, Powertrench MosfetDocument8 pagesFds6612A: Single N-Channel, Logic-Level, Powertrench MosfetCarlos Manuel PeraltaNo ratings yet

- c9945 TermokingDocument7 pagesc9945 TermokingNelson CabelloNo ratings yet

- Fds6690A Single N-Channel, Logic Level, Powertrench MosfetDocument8 pagesFds6690A Single N-Channel, Logic Level, Powertrench MosfetEsmir MarinNo ratings yet

- Fds6690A: Single N-Channel, Logic-Level, Powertrench MosfetDocument6 pagesFds6690A: Single N-Channel, Logic-Level, Powertrench Mosfetmuhammad atifNo ratings yet

- Fds6690A: Single N-Channel, Logic-Level, Powertrench MosfetDocument6 pagesFds6690A: Single N-Channel, Logic-Level, Powertrench MosfetDenis SilvaNo ratings yet

- Datasheet - HK Fds9431a10 4643859Document5 pagesDatasheet - HK Fds9431a10 4643859jim campbellNo ratings yet

- Dual 30V P-Channel Powertrench Mosfet: General Description FeaturesDocument5 pagesDual 30V P-Channel Powertrench Mosfet: General Description FeaturesLuis AntunesNo ratings yet

- FDS6930 PDFDocument5 pagesFDS6930 PDFTut MorisNo ratings yet

- FDS7088N3Document6 pagesFDS7088N3kamil.smolinski.1980No ratings yet

- Fdn339An: N-Channel 2.5V Specified Powertrench MosfetDocument5 pagesFdn339An: N-Channel 2.5V Specified Powertrench MosfetKevinAlexisVelascoPeraltaNo ratings yet

- Fds 9933 ADocument5 pagesFds 9933 Aasasdassdfdf asdfasdsdfsfsdNo ratings yet

- Fds6982S: Dual Notebook Power Supply N-Channel Powertrench SyncfetDocument9 pagesFds6982S: Dual Notebook Power Supply N-Channel Powertrench SyncfetManuel LeaNo ratings yet

- 9960GM SiliconStandardDocument6 pages9960GM SiliconStandardzakie wahyuNo ratings yet

- STP14NF12 STP14NF12FP: N-CHANNEL 120V - 0.16 - 14A TO-220/TO-220FP Low Gate Charge Stripfet™ Power MosfetDocument9 pagesSTP14NF12 STP14NF12FP: N-CHANNEL 120V - 0.16 - 14A TO-220/TO-220FP Low Gate Charge Stripfet™ Power MosfetDavid Duarte VeraNo ratings yet

- D12NF06L_FET_STD12NF06LDocument14 pagesD12NF06L_FET_STD12NF06LRuslanNo ratings yet

- Fdd5614P: 60V P-Channel Powertrench MosfetDocument6 pagesFdd5614P: 60V P-Channel Powertrench MosfetAmaury jrNo ratings yet

- FDS7296N3 - 30V N-Channel PowerTrench MOSFETDocument7 pagesFDS7296N3 - 30V N-Channel PowerTrench MOSFETLangllyNo ratings yet

- FDN352 ApDocument5 pagesFDN352 ApTecnicos SlotsNo ratings yet

- NDT456 1Document10 pagesNDT456 1Kike VillasurNo ratings yet

- On Semiconductor - mtd20p06hdl-dDocument8 pagesOn Semiconductor - mtd20p06hdl-dshohratNo ratings yet

- Onsemiconductor Nds8410a Datasheets 3577Document5 pagesOnsemiconductor Nds8410a Datasheets 3577Google EyeNo ratings yet

- 4435 FairchildSemiconductorDocument6 pages4435 FairchildSemiconductorYared TarikuNo ratings yet

- ST p14nf12 PDFDocument15 pagesST p14nf12 PDFwertingoNo ratings yet

- Fdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MDocument5 pagesFdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MKakatuar KakatuaNo ratings yet

- Is Now Part ofDocument10 pagesIs Now Part ofMatias GonzalezNo ratings yet

- Ao4801 PDFDocument5 pagesAo4801 PDFlujorebNo ratings yet

- Mt2301 Mos TechDocument8 pagesMt2301 Mos Techdoraemon007No ratings yet

- RoHS-compliant dual P-channel MOSFET in SO-8 packageDocument5 pagesRoHS-compliant dual P-channel MOSFET in SO-8 packageJheremy Sebastian TorresNo ratings yet

- CBE6030LDocument8 pagesCBE6030LgdiliogNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument4 pagesAdvanced Power Electronics Corp.: DescriptionJorje FranciscoNo ratings yet

- N-Channel Enhancement Mode Field Effect Transistor: FeaturesDocument7 pagesN-Channel Enhancement Mode Field Effect Transistor: Features5a DOHCNo ratings yet

- NDS332PDocument6 pagesNDS332PmitrakaryaNo ratings yet

- General Description Product Summary: 30V P-Channel MOSFETDocument5 pagesGeneral Description Product Summary: 30V P-Channel MOSFETGioVoTamNo ratings yet

- Schema TranzistorDocument10 pagesSchema Tranzistormunteanu872No ratings yet

- A1SHBDocument6 pagesA1SHBJoelmoÉvoraNo ratings yet

- J105 / J106 / J107 N-Channel Switch: DescriptionDocument6 pagesJ105 / J106 / J107 N-Channel Switch: Descriptionfarlocco23No ratings yet

- STP62NS04Z: N-Channel Clamped 12.5 M, 62 A, TO-220 Fully Protected MESH OVERLAY™ Power MOSFETDocument12 pagesSTP62NS04Z: N-Channel Clamped 12.5 M, 62 A, TO-220 Fully Protected MESH OVERLAY™ Power MOSFETmartinNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument5 pagesAdvanced Power Electronics Corp.: DescriptionEngahMo MosaNo ratings yet

- FDD6680ADocument6 pagesFDD6680AEdson HenriqueNo ratings yet

- fdc658p-d 58axDocument6 pagesfdc658p-d 58axTECNOLOGIA GLOBAL EN COMPUTACION Y SISTEMAS C.ANo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- AN460_P82B96Document8 pagesAN460_P82B96sbrhomeNo ratings yet

- AN460_P82B96Document8 pagesAN460_P82B96sbrhomeNo ratings yet

- AN1119 Application Note: Correct Power-On and Power-Off For The M93Cxx and M93SxxDocument6 pagesAN1119 Application Note: Correct Power-On and Power-Off For The M93Cxx and M93SxxJuan HernándezNo ratings yet

- AQV216ADocument4 pagesAQV216AsbrhomeNo ratings yet

- Sabatair: Task4: Lithium Ion Cell Exposure To An On-Board External Fire: Test ProgramDocument15 pagesSabatair: Task4: Lithium Ion Cell Exposure To An On-Board External Fire: Test ProgramsbrhomeNo ratings yet

- Guidance On Hazard IdentificationDocument20 pagesGuidance On Hazard IdentificationtimminNo ratings yet

- TPS54160 1.5-A, 60-V, Step-Down DC/DC Converter With Eco-Mode™Document57 pagesTPS54160 1.5-A, 60-V, Step-Down DC/DC Converter With Eco-Mode™sbrhomeNo ratings yet

- mp610-sm Manuel Reparateur PDFDocument45 pagesmp610-sm Manuel Reparateur PDFMilanPr3No ratings yet

- CS-29 Amendment 3 Explanatory Note SummaryDocument3 pagesCS-29 Amendment 3 Explanatory Note SummarysbrhomeNo ratings yet

- EASA CM-SWCEH-001 Development Assurance of Airborne Electronic HardwareDocument66 pagesEASA CM-SWCEH-001 Development Assurance of Airborne Electronic HardwaresbrhomeNo ratings yet

- Cambridge International AS & A Level: PHYSICS 9702/42Document24 pagesCambridge International AS & A Level: PHYSICS 9702/42Gulnur KenzheevaNo ratings yet

- Performance Evaluation of GeneratorTransformer Unit Overall Differential ProtectionDocument9 pagesPerformance Evaluation of GeneratorTransformer Unit Overall Differential ProtectionAdam IbnuNo ratings yet

- Accellerometer FAQ 092003Document107 pagesAccellerometer FAQ 092003Phillip_vaziri1832No ratings yet

- Control PanelDocument9 pagesControl PanelPEMELIHARAAN LISTRIKNo ratings yet

- Eaton 1670 KW DataSheetDocument4 pagesEaton 1670 KW DataSheetEhsanNo ratings yet

- Fabrication and Analysis of Portable Spot Welding MachineDocument7 pagesFabrication and Analysis of Portable Spot Welding MachineCrispNo ratings yet

- 400+ TOP ELECTRICAL Engineering Interview Questions & Answers PDFDocument1 page400+ TOP ELECTRICAL Engineering Interview Questions & Answers PDFZedo ZedoNo ratings yet

- AWG Catalog PDFDocument412 pagesAWG Catalog PDFgerrzen64No ratings yet

- DHA Sileo 500dv 3ph400vDocument3 pagesDHA Sileo 500dv 3ph400vPavle PerovicNo ratings yet

- Spindle Motor Troubleshooting GuideDocument7 pagesSpindle Motor Troubleshooting GuideIsrael Martinez AlonsoNo ratings yet

- Capacitance Hazards in E-Mobility v0.1bDocument9 pagesCapacitance Hazards in E-Mobility v0.1bStefNo ratings yet

- Kjm3110 Chapter 7 Electrode ReactionsDocument24 pagesKjm3110 Chapter 7 Electrode ReactionsMohammad Javad KamaliNo ratings yet

- Diagnostics SwitchDocument2 pagesDiagnostics SwitchGioalrizki GioalrizkiNo ratings yet

- XP6-R Six Relay ModuleDocument2 pagesXP6-R Six Relay ModuleDon HornbyNo ratings yet

- PHOTONICS COMMUNICATION: AN OVERVIEWDocument14 pagesPHOTONICS COMMUNICATION: AN OVERVIEWKavithaNo ratings yet

- J. Electrochem. Soc.-2017-Darling-E3081-91Document11 pagesJ. Electrochem. Soc.-2017-Darling-E3081-91Geovanny JaenzNo ratings yet

- Waves and Wave PropertiesDocument3 pagesWaves and Wave PropertiesUkiouwuNo ratings yet

- Grundos Ms6000 Motor 78185620 - Ms6000rest40Document10 pagesGrundos Ms6000 Motor 78185620 - Ms6000rest40Rizwan BaigNo ratings yet

- Physics 10Th Prepared By: Muhammad Naeem Unit 14: Spherical Mirrors and LensesDocument3 pagesPhysics 10Th Prepared By: Muhammad Naeem Unit 14: Spherical Mirrors and LensesMohammad NaeemNo ratings yet

- Cap 1298Document71 pagesCap 1298syyeung17No ratings yet

- Safety Precautions for G7F-ADHB ModuleDocument2 pagesSafety Precautions for G7F-ADHB Moduleatakan kurtcaNo ratings yet

- DSE4120 Installation InstructionsDocument2 pagesDSE4120 Installation InstructionsRahmat Nur IlhamNo ratings yet

- TDA2611Document3 pagesTDA2611Gandhi HammoudNo ratings yet

- E 02 CH 04Document1 pageE 02 CH 04Tariq Zuhluf100% (2)

- PH3007 Logic Families L 29 - 31Document33 pagesPH3007 Logic Families L 29 - 31Nethmi LokusuriyaNo ratings yet

- NFC 17 102 (Old 1995) PDFDocument64 pagesNFC 17 102 (Old 1995) PDFOmar VicenteNo ratings yet

- SR Fe Mo O As Anodes For Solid Oxide Fuel Cells: Journal of Power SourcesDocument4 pagesSR Fe Mo O As Anodes For Solid Oxide Fuel Cells: Journal of Power SourcesJosé Luis Rosas HuertaNo ratings yet

- Practical 25 - Temperature Coefficient of Resistance PDFDocument1 pagePractical 25 - Temperature Coefficient of Resistance PDFNasrin Sultana50% (2)

- LTBT TM BcmiogDocument170 pagesLTBT TM BcmiogRicardo RoblesNo ratings yet

- Wiring Diagram HFM-SFI Sequential Multiport Fuel Injection - Ignition SystemDocument5 pagesWiring Diagram HFM-SFI Sequential Multiport Fuel Injection - Ignition SystemKanishka Prasade0% (1)