Professional Documents

Culture Documents

Ade Lab

Uploaded by

Abhishek nOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ade Lab

Uploaded by

Abhishek nCopyright:

Available Formats

ANALOG AND DIGITAL ELECTRONICS LAB 18CSL37

Laboratory Programs

PART A (Analog Electronic Circuits)

1. Design an astable multivibrator circuit for three cases of duty cycle (50%, <50% and

>50%) using NE 555 timer IC. Simulate the same for any one duty cycle.

2. Using ua 741 Opamp, design a 1 kHz Relaxation Oscillator with 50% duty cycle. And

simulate the same.

3. Using ua-741 opamap, design a window comparator for any given UTP and LTP. And

simulate the same.

PART B (Digital Electronic Circuits)

4. Design and implement half adder, Full Adder, Half Subtractor, Full Subtractor using basic

gates. And implement the same in HDL.

5. Given a 4-variable logic expression, simplify it using appropriate technique and realize the

simplified logic expression using 8:1 multiplexer IC. And implement the same in HDL.

6. Realize a J-K Master / Slave Flip-Flop using NAND gates and verify its truth table. And

implement the same in HDL.

7. Design and implement code converter

I) Binary to Gray

(II) Gray to Binary Code using basic gates.

8. Design and implement a mod-n (n<8) synchronous up counter using J-K Flip-Flop ICs and

Demonstrate its working.

9. Design and implement an asynchronous counter using decade counter IC to count up from

0 to n (n<=9) and demonstrate on 7-segment display (using IC-7447)

ECE Dept. JVIT BIDADI Page 1

ANALOG AND DIGITAL ELECTRONICS LAB 18CSL37

8. Design and implement a mod-n (n<8) synchronous up counter using J-K Flip-Flop

ICs and Demonstrate its working.

Theory:

In digital logic and computing, a counter is a device which stores (and sometimes displays)

the number of times a particular event or process has occurred, often in relationship to a clock

signal.

A synchronous counter is one whose output bits change sate simultaneously. Such a

counter circuit can be built from JK flip-flop by connecting all the clock inputs together, so

that each and every flip- flop receives the exact same clock pulse at the exact same time. By

examining the four-bit binary count sequence, it noticed that just before a bit toggles, all pre-

ceding bits are "high".

That is a synchronous up-counter can be implemented by toggling the bit when all of

the less significant bits are at a logic high state. For example, bit 1 toggles when bit 0 is logic

high; bit 2 toggles when both bit 1 and bit 0 are logic high; bit 3 toggles when bit 2, bit 1 and

bit 0 are all high; and so on.

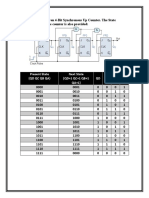

DESIGN TABLE

Present State Next state Flip flop inputs

QA QB QC QA+1 QB+1 QC+1 JA KA JB KB JC KC

0 0 0 0 0 1 0 X 0 X 1 X

0 0 1 0 1 0 0 X 1 X X 1

0 1 0 0 1 1 0 X X 0 1 X

0 1 1 1 0 0 1 X X 1 X 1

1 0 0 1 0 1 X 0 0 X 1 X

1 0 1 0 0 0 X 1 0 X X 1

1 1 0 X X X X X X X X X

1 1 1 X X X X X X X X X

JC KC

X X

JC=1 KC=1

ECE Dept. JVIT BIDADI Page 2

ANALOG AND DIGITAL ELECTRONICS LAB 18CSL37

0 X

JB= QAQC KB= QC

KB

JA

JA= QBQC KA= QC

MOD-5 COUNTER CIRCUIT DIAGRAM

ECE Dept. JVIT BIDADI Page 3

ANALOG AND DIGITAL ELECTRONICS LAB 18CSL37

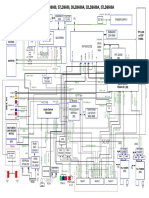

7476 IC PIN DIAGRAM

ECE Dept. JVIT BIDADI Page 4

You might also like

- DLD-Counters ExperiemntDocument6 pagesDLD-Counters Experiemnt123ad0006No ratings yet

- Wah Campus: Experiment No 12Document4 pagesWah Campus: Experiment No 12HALLIMA SADIANo ratings yet

- Sequential Circuits wk9Document18 pagesSequential Circuits wk9Matthew LewisNo ratings yet

- Experiment-10: AIM: Design and Implement 3 Bit Synchronous UP/Down Counter TheoryDocument9 pagesExperiment-10: AIM: Design and Implement 3 Bit Synchronous UP/Down Counter TheorySujith ReddyNo ratings yet

- ADE Exp.10Document8 pagesADE Exp.10Bhuvan BeeraNo ratings yet

- Experiment#11 Clocked Sequential Circuits and CountersDocument8 pagesExperiment#11 Clocked Sequential Circuits and CountersfahadNo ratings yet

- WORD File of 3-Bit CounterDocument4 pagesWORD File of 3-Bit CounterCh Usman JuttNo ratings yet

- Module 8b SynchDesign - SeqAnalysis - Cascade - ExtraDocument10 pagesModule 8b SynchDesign - SeqAnalysis - Cascade - ExtraTường TrươngNo ratings yet

- 10a 3 Bit Up Down Counter DoneDocument6 pages10a 3 Bit Up Down Counter DoneVenkatGollaNo ratings yet

- CombinepdfDocument12 pagesCombinepdfZakuan HassanNo ratings yet

- Laboratory Experiments Report File Computer Science & Engineering May/June 2018 SessionDocument26 pagesLaboratory Experiments Report File Computer Science & Engineering May/June 2018 SessionAnil RawatNo ratings yet

- State Design Gray CodeDocument3 pagesState Design Gray CodejeyanthvrNo ratings yet

- Experiment No 10Document5 pagesExperiment No 10Charan MandapakaNo ratings yet

- 3 Bit Synchronous Up Counter Mod 8Document4 pages3 Bit Synchronous Up Counter Mod 8Sujan ProdhanNo ratings yet

- CountersDocument17 pagesCountersUnknown GirlNo ratings yet

- Enel3ds Lab 1 ReportDocument12 pagesEnel3ds Lab 1 ReportLindokuhle CebekhuluNo ratings yet

- Digital Electronics Circuits: Experiment: 9Document4 pagesDigital Electronics Circuits: Experiment: 9movabNo ratings yet

- Experiment No.:9: ObjectiveDocument6 pagesExperiment No.:9: ObjectiveAditi MahendraNo ratings yet

- 3 Bit Synchronous CounterDocument5 pages3 Bit Synchronous CounterCHERISMA100% (1)

- Digital Logic Design: LectureDocument67 pagesDigital Logic Design: Lecturedream breakerNo ratings yet

- Lect Counter - EE208Document17 pagesLect Counter - EE208Anonymous 001No ratings yet

- Sequential Circuits - Gustavo 3Document27 pagesSequential Circuits - Gustavo 3Gustavo SánchezNo ratings yet

- Micro Project 3Document7 pagesMicro Project 3Dipin Preet SinghNo ratings yet

- Week 10Document43 pagesWeek 10lucifer 041No ratings yet

- 3 Bit Synchronous Up CounterDocument15 pages3 Bit Synchronous Up CounterMaruf MorshedNo ratings yet

- Results and Summary For Laboratory 2: Experiment 1Document8 pagesResults and Summary For Laboratory 2: Experiment 1Lau Lok BinNo ratings yet

- State Diagram:: Truth Table Relating S, R, T, Q (T) To Q (t+1) Q (T) S R T Q (t+1)Document6 pagesState Diagram:: Truth Table Relating S, R, T, Q (T) To Q (t+1) Q (T) S R T Q (t+1)Irtaza AkramNo ratings yet

- DLD Lab 03-Combinational LogicDocument6 pagesDLD Lab 03-Combinational LogicMuhammad RafayNo ratings yet

- 34-Design of Synchronous Counters-24!03!2023Document17 pages34-Design of Synchronous Counters-24!03!2023Back upNo ratings yet

- GA Puteri Dan Nur NabihahDocument11 pagesGA Puteri Dan Nur Nabihahnzirh 01No ratings yet

- Chapter 4 - Synchronous MOD CountersDocument8 pagesChapter 4 - Synchronous MOD CountersMinh PhúNo ratings yet

- Part2 Synchronous CountersDocument6 pagesPart2 Synchronous CountersLilya OuarabNo ratings yet

- Vlsi - Lab (1) - 1-39Document39 pagesVlsi - Lab (1) - 1-39Angel AlphaNo ratings yet

- Combinational Circuits - 2Document66 pagesCombinational Circuits - 2harshulyagnik.cseNo ratings yet

- Sisay AyalewDocument15 pagesSisay AyalewSISAy AyalewNo ratings yet

- Final-Exam Report: Subject: Ins3135Document15 pagesFinal-Exam Report: Subject: Ins3135Phạm NamNo ratings yet

- Lab 13 2022 2Document2 pagesLab 13 2022 2CuongNo ratings yet

- 302 AssignmentDocument7 pages302 AssignmentMuhammad ArslanNo ratings yet

- Group 11Document16 pagesGroup 11SISAy AyalewNo ratings yet

- School of Mechatronic Engineering University Malaysia PerlisDocument14 pagesSchool of Mechatronic Engineering University Malaysia PerlisJoseph VijayNo ratings yet

- Carrier Modulation: Version 2 ECE IIT, KharagpurDocument9 pagesCarrier Modulation: Version 2 ECE IIT, KharagpurRupaShaw100% (1)

- Team6 Combinational Logic Circuit 2Document46 pagesTeam6 Combinational Logic Circuit 2marycrisbanayNo ratings yet

- COEN 3137 - Experiment No. 7 - Synchronous Binary CountersDocument19 pagesCOEN 3137 - Experiment No. 7 - Synchronous Binary Countersjocansino4496No ratings yet

- Counters by AmthalDocument12 pagesCounters by AmthalxcNo ratings yet

- DigitalLogic 1563618006891 PDFDocument8 pagesDigitalLogic 1563618006891 PDFSagar GulatiNo ratings yet

- ResearchDocument9 pagesResearchDev SutariyaNo ratings yet

- 21 CP 04 Lab Report 5Document6 pages21 CP 04 Lab Report 5Aafaaq AmirNo ratings yet

- 21-Cp - 64 (Lab No 5)Document6 pages21-Cp - 64 (Lab No 5)Aafaaq AmirNo ratings yet

- 2019-01-23 - HiPEAC Tutorial - AritraDocument30 pages2019-01-23 - HiPEAC Tutorial - AritraAritra SarkarNo ratings yet

- MC200202349 Cs 302 SOLUTIONDocument5 pagesMC200202349 Cs 302 SOLUTIONDeen ki BatainNo ratings yet

- 0001 Introduction SpiceDocument9 pages0001 Introduction SpiceRimsha pervaizNo ratings yet

- GROUP2 LABACT8 CPEC301-301G 1stSEMESTER-SY2223Document10 pagesGROUP2 LABACT8 CPEC301-301G 1stSEMESTER-SY2223Celine Fernandez CelociaNo ratings yet

- CountersDocument26 pagesCountersamrit saudNo ratings yet

- Chapter 4 - Synchronous CountersDocument12 pagesChapter 4 - Synchronous CountersMinh PhúNo ratings yet

- Combinational Circuits LDICDocument129 pagesCombinational Circuits LDIChemanth ramireddyNo ratings yet

- Assignment 7 Solution 3rd EditionDocument5 pagesAssignment 7 Solution 3rd EditionAvi SinghNo ratings yet

- Stucor CS3351-GKDocument269 pagesStucor CS3351-GKNightdive StudiosNo ratings yet

- Stucor Cs3351-Dpco RemovedDocument99 pagesStucor Cs3351-Dpco RemovedTishbian MeshachNo ratings yet

- Lab ReportDocument14 pagesLab ReportZuhaib AhmadNo ratings yet

- 03 SPP 46S Proposal FormatDocument8 pages03 SPP 46S Proposal FormatAbhishek nNo ratings yet

- Frequncey 1 0.5 Square NRZDocument1 pageFrequncey 1 0.5 Square NRZAbhishek nNo ratings yet

- DC NotesDocument225 pagesDC NotesAbhishek nNo ratings yet

- 18CSL48 MergedDocument48 pages18CSL48 MergedAbhishek nNo ratings yet

- 555Document1 page555Abhishek nNo ratings yet

- Module 3: Transistor and Fet Frequency ResponseDocument35 pagesModule 3: Transistor and Fet Frequency ResponseAbhishek nNo ratings yet

- Mar 2022Document2 pagesMar 2022Abhishek nNo ratings yet

- Jnanavikas Institute of Technology: Mr. Shubas S.RDocument76 pagesJnanavikas Institute of Technology: Mr. Shubas S.RAbhishek nNo ratings yet

- Mwa NotesDocument224 pagesMwa NotesAbhishek nNo ratings yet

- DSDV 18ec644Document5 pagesDSDV 18ec644Abhishek nNo ratings yet

- Jnanavikas Institute of Technology: Mr. Shubas S.RDocument74 pagesJnanavikas Institute of Technology: Mr. Shubas S.RAbhishek nNo ratings yet

- 3rd Sem Edi Lab Manual (18ecl37) JvitDocument48 pages3rd Sem Edi Lab Manual (18ecl37) JvitAbhishek nNo ratings yet

- Simulate NRZ, RZ, Half-Sinusoid and Raised Cosine Pulses and Generate Eye Diagram For Binary Polar SignallingDocument10 pagesSimulate NRZ, RZ, Half-Sinusoid and Raised Cosine Pulses and Generate Eye Diagram For Binary Polar SignallingAbhishek nNo ratings yet

- Ade LabDocument4 pagesAde LabAbhishek nNo ratings yet

- Edge ComputingDocument5 pagesEdge ComputingAbhishek nNo ratings yet

- Civil V Transportation Engineering 1 U2Document11 pagesCivil V Transportation Engineering 1 U2Abhishek nNo ratings yet

- New Microsoft Word Document PDFDocument1 pageNew Microsoft Word Document PDFAbhishek nNo ratings yet

- Unit 8 HIGHWAY DRAINAGE PDFDocument27 pagesUnit 8 HIGHWAY DRAINAGE PDFAbhishek nNo ratings yet

- Paperlms (Ref) PDFDocument40 pagesPaperlms (Ref) PDFAbhishek nNo ratings yet

- ETEC 2301 Programmable Logic Devices: CountersDocument34 pagesETEC 2301 Programmable Logic Devices: CountersvmspraneethNo ratings yet

- 1 Install and Configure Computer SystemsDocument88 pages1 Install and Configure Computer SystemsJayvie RaquelNo ratings yet

- ECSE 548 - Electronic Design and Implementation of The Sine Function On 8-Bit MIPS Processor - ReportDocument4 pagesECSE 548 - Electronic Design and Implementation of The Sine Function On 8-Bit MIPS Processor - Reportpiohm100% (1)

- COA KCS-302 Model Question Paper: Computer Organization & Architecture (Dr. A.P.J. Abdul Kalam Technical University)Document3 pagesCOA KCS-302 Model Question Paper: Computer Organization & Architecture (Dr. A.P.J. Abdul Kalam Technical University)Piyush GuptaNo ratings yet

- HP StrategyDocument2 pagesHP StrategytcudorpNo ratings yet

- 26-37 Ld6600aDocument10 pages26-37 Ld6600aAnonymous h80fVWNo ratings yet

- Iwave Systems Technologies Pvt. LTDDocument42 pagesIwave Systems Technologies Pvt. LTDMagendran PKNo ratings yet

- Describe The Operation of Timing and Control BlockDocument4 pagesDescribe The Operation of Timing and Control BlockTamayo Arrianna MurielNo ratings yet

- 14 - NuMicro Supporting SoftwareDocument17 pages14 - NuMicro Supporting SoftwareThienNo ratings yet

- Pio16 Plugin Mach3Document2 pagesPio16 Plugin Mach3ramjoceNo ratings yet

- 0647.f28335 Flash Prog 0Document4 pages0647.f28335 Flash Prog 0UmairKhanNo ratings yet

- Unit-5 (Coa) NotesDocument33 pagesUnit-5 (Coa) NotesyashNo ratings yet

- Digital Design Through Verilog HDL Course Outcomes For LabDocument1 pageDigital Design Through Verilog HDL Course Outcomes For LabSyed AshmadNo ratings yet

- DLCDocument4 pagesDLCramNo ratings yet

- Labview Fpga ModuleDocument5 pagesLabview Fpga Modulevanhai_hvktqs41No ratings yet

- CS 321 Computer Organization & Assembly Language: Princes Nora Bint Abdul Rahman UniversityDocument14 pagesCS 321 Computer Organization & Assembly Language: Princes Nora Bint Abdul Rahman UniversityNurul Badriah Anwar AliNo ratings yet

- Intro To VLSI System DesignDocument46 pagesIntro To VLSI System DesignAmiruddin Mohd Arifuddin100% (1)

- Comparison of Multimedia SIMD, GPUs and VectorDocument13 pagesComparison of Multimedia SIMD, GPUs and VectorHarsh PrasadNo ratings yet

- Trouble Code List Sharp CodesDocument3 pagesTrouble Code List Sharp Codessalih1965No ratings yet

- CEG 2136 - Fall 2005 - FinalDocument12 pagesCEG 2136 - Fall 2005 - FinalAmin DhouibNo ratings yet

- Itec 100 ch7Document42 pagesItec 100 ch7HasNo ratings yet

- Bcn1043 - Computer Architecture & OrganizationDocument4 pagesBcn1043 - Computer Architecture & OrganizationYuku MashiNo ratings yet

- Timing in Digital CircuitsDocument18 pagesTiming in Digital Circuitsshrish9999No ratings yet

- Notes Cso Unit 2Document25 pagesNotes Cso Unit 2nishantsinNo ratings yet

- 100 Power Tips for FPGA Designers 초록 PDFDocument18 pages100 Power Tips for FPGA Designers 초록 PDFeunhye100% (1)

- Govindarajulu Computer ArchitectureDocument4 pagesGovindarajulu Computer ArchitectureLori0% (2)

- Manual Variador Allen Bradley 161Document50 pagesManual Variador Allen Bradley 161Cosmin BlagaNo ratings yet

- Exp 4Document5 pagesExp 4Muhammad SaeedNo ratings yet

- Best Known Methods For Using Cadence Conformal LECDocument13 pagesBest Known Methods For Using Cadence Conformal LECManu GopinathNo ratings yet