Professional Documents

Culture Documents

DSDV Question Bank for Digital System Design Using Verilog

Uploaded by

Abhishek nOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DSDV Question Bank for Digital System Design Using Verilog

Uploaded by

Abhishek nCopyright:

Available Formats

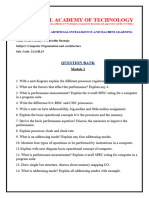

DSDV (18EC644) Question Bank Prepared by: Abhishek N, Asst Prof

DIGITAL SYSTEM DESIGN USING VERILOG

B.E., VI Semester (Open Elective)

[As per Choice Based Credit System (CBCS) Scheme]

Course Code: 18EC644 CIE Marks: 40

Number of Lecture Hours/Week: 03 SEE Marks: 60

Total Number of Lecture Hours: 40 (08 Hrs per module) Exam Hours: 03

CREDITS – 03

QUESTION BANK

Note: This question bank is prepared by referring to June/July 2018, Dec/ Jan 2019,

June/July 2019 and Dec/Jan 2020 VTU Semester End Exam (SEE) question papers for the

course 15EC663. Also, some important questions (apart from SEE QPs) have been added for

reference.

MODULE 1

1. Define the terms setup time, hold time and clock to output time of a flip flop and what are

the constraints imposed by these parameters on the circuit operations.

2. Develop verilog module for 7 segment decoder. Include an additional input „blank‟ that

overrides the BCD input and causes all segments not to be lit.

3. Explain functional verification and formal verification for a verilog module

4. What are the effects of capacitive loading and propagation delay on signal transitions

between logic levels?

5. Develop verilog module for 4:1 MUX.

6. Explain general view of digital system with data path & control section.

7. Explain with illustration, a simple design methodology followed in IC industries.

8. Explain the following constraints imposed in real world circuits:

(i) Noise margin (ii) Propagation delay (iii) Static Levels

(iv) Static and dynamic power consumption.

9. Develop a verilog module of a debouncer for a push button switvh that uses a debounce

interval of 10ns. Assume the system clock frequency is 50 MHz.

10. Design and develop a circuit and verilog module for modulo 10 counters.

11. What is the distinction between a Moore and Mealy finite state machine?

12. What are the two sources of power consumption in digital components? Explain.

Department of Electronics & Communication Engg. JVIT, BIDADI Page 1

DSDV (18EC644) Question Bank Prepared by: Abhishek N, Asst Prof

13. Design an encoder for the burglar alarm that has sensors for each of the 8 zones as a

priority encoder with zone 1 having highest priority down to zone 8 having lowest

priority.

14. Develop a datapath to perform complex multiplication of two complex number whose real

and imaginary parts are represented as signed fixed point numbers with 4-pre binary

points and 12 post binary points. Real and imaginary parts of the product are represented

with 8 pre-binary points and 24 post-binary points. Area is the main constraint. Also,

write the verilog model of the complex multiplier datapath.

15. Write a logic circuit and Verilog model for a Vat Buzzer circuit in a factory. The factory

has two vats onl one of which is used at a time he liquid in the vat in use needs to be

at the right temperature between and ach vat has two temperature sensors

indicating whether the temperature is above and above respectivel he vats

also have low level sensors. The supervisor needs to be woken up by a buzzer when the

temperature is too high or too low or the vat level is too low. He has a switch to select

which vat is in use.

16. Write a Verilog model for an encoder for use in a domestic burglar alarm that has sensors

for each of eight zones. Each sensor signal is 1 when an intrusion is detected in that zone,

and 0 otherwise. The encoder has three bits of output, encoding the zone as follows: Zone

1: 000, Zone 2: 001, Zone 3: 010, Zone 4: 011, Zone 5: 100, Zone 6: 101, Zone 7: 110 &

Zone 8: 111.

17. Explain the concept of verification of combinational circuits with suitable example.

18. Explain the constraints of clocked synchronous timing methodology with suitable

diagrams.

19. Write a Verilog model of complex multiplier Control Section FSM.

20. Describe the embedded system design methodology.

21. Describe the concept of Logic Levels and Noise Margin in Digital Circuits.

MODULE 2

1. Write a symbol for basic memory component and explain its parts.

2. Explain about the multiport memories.

3. Compute the 12-bit ECC word corresponding to the 8-bit data word “ 11 1”

4. Design a 64K x 16 bit composite memory using 16K x 8 bit components and also explain

how memory components with tristate data outputs simplify the construction of larger

memories.

Department of Electronics & Communication Engg. JVIT, BIDADI Page 2

DSDV (18EC644) Question Bank Prepared by: Abhishek N, Asst Prof

5. What is the difference between asynchronous static RAM and synchronous static RAM?

6. Using a Hamming code, how many check bits are required for single error correction and

double error detection for 4-bit data word?

7. Explain asynchronous static RAM with timing diagrams.

8. Write a note on multiport memories.

9. Explain error detection and correction with one example.

10. Design a 1M x 8 bit composite memory using 512 K x 8 bit memory components.

11. Design a 16K x 48 bit memory using 16K x 16 bit memory components.

12. Explain flow through and pipelined SSRAM with the help of timing diagram.

13. Determine whether there is an error in the ECC word 000111000100 and if so, correct it.

14. Develop a verilog model of a dual port 4K x 16 bit flow through SSRAM. One port

allows data to be written and read, while the other port allows data to be read.

15. Explain dynamic RAM operation.

16. Draw the circuit of a 64K*8-bit composite memory using four 16K*8-bit components.

Revise the circuit using bi-directional I/O ports.

17. Describe Read only memories.

18. Write a logic circuit that computes the function y = ci × x2, where x is a binary-coded

input value and ci is a coefficient stored in a flow-through SSRAM. x, ci and y are all

signed fixed-point values with 8 pre binary-point and 12 post-binary-point bits. The index

i is also an input to the circuit, encoded as a 12-bit unsigned integer. Values for x and i

arrive at the input during the cycle when a control input, start, is 1. The circuit should

minimize area by using single multiplier to multiply ci by x and then by x again.

19. Explain the common cause of soft errors in DRAMs. Compute the 12-bit ECC word

corresponding to the 8-bit data word 01100001.

20. Write a logic circuit a FIFO to store up to 256 data items of 16 bits each, using a 256x16-

bit dual-port SSRAM for the data storage. The FIFO should provide status outputs to

indicate when the FIFO is empty and full. Assume that the FIFO will not be read when it

is empty, nor be written to when it is full, and that the write and read ports share a

common clock.

MODULE 3

1. Explain briefly about the sequence of steps involved in IC manufacture.

2. Write and explain the internal organization of a CPLD.

3. What are the two main design and manufacturing techniques for ASICs? Explain

Department of Electronics & Communication Engg. JVIT, BIDADI Page 3

DSDV (18EC644) Question Bank Prepared by: Abhishek N, Asst Prof

4. Write and explain the internal organization of the FPGA.

5. What distinguishes a platform FPGA from a simple FPGA?

6. Explain differential signalling in detail.

7. What are the purposes of logic blocks and I/O blocks in FPGA?

8. Explain different types of PCB design.

9. Explain implementation fabrics for digital system based on integrated circuit.

10. What are EMI and cross talk?

11. Briefly explain programmable array logic (PAL).

12. Explain signal integrity issue in PCB design and also explain measures to reduce these

issues.

13. Use the following components to design a 4-digit decimal counter with a 7-segment LED

display: two 74LS390 dual decade counters, four 74LS47 BCD to 7-segment decoders,

four 7-segment displays, plus any additional gates required.

14. Explain signal integrity interconnection issue in PCB design.

MODULE 4

1. Show how a 64-bit data word can be transmitted serially between two parts of a system.

Assume that the transmitter and the receiver are both within the same clock domain, and

that the signal start is set to 1 on a clock cycle in which data is ready to be transmitted.

2. Explain any 4 analog sensors.

3. Explain the concept of multiplexed buses.

4. Explain the analog inputs used in input devices.

5. Explain any four serial interface standards.

6. Explain briefly the tristate buses and weak keepers.

7. Design and develop verilog code for an input controller that has 8-bit binary-coded input

from a sensor. The value can be read from an 8-bit input register. The controller should

interrupt the embedded Gumnut core when the input value changes. The controller is the

only interrupt source in the system.

8. What are the purposes of the following in an I/O controller:

(i) input register (ii) output register (iii) control register (iv) status register

9. With a neat diagram, explain R-string DAC and R/2R ladder DAC.

10. What are the serial input standards? Breifly explain each.

11. Explain flash ADC and successive approximation ADC with the help of necessary

diagrams.

Department of Electronics & Communication Engg. JVIT, BIDADI Page 4

DSDV (18EC644) Question Bank Prepared by: Abhishek N, Asst Prof

12. Write a Verilog model that represents a tri-state bus driver for an 8-bit bus. Also sketch

the logic circuit.

13. Describe the Interrupt Mechanism in I/O software.

14. Describe the concept of Polling in I/O software.

15. Develop a Verilog model of a display multiplexer and decoder for the 4-digit 7-segment

display. The circuit has four BCD inputs. The decimal point for the left-most digit should

be lit, and the remaining decimal points not lit. The system clock has a frequency of

10MHz.

MODULE 5

1. Explain the hardware and software co-design flow.

2. Explain the design optimizations that are must to meet the design constraints.

3. Write a short note on Scan design and boundary scan.

4. Write a short note Built-in Self Test (BIST)

5. Explain logical partitioning and physical partitioning of a transport monitoring system.

6. Explain fault model and fault simulation.

7. Explain a 4 bit LFSR and CFSR for generating pseudorandom test vectors.

8. Explain briefly area, power and timing optimization in digital circuits.

9. Briefly describe techniques used in power optimization.

10. Explain floorplan, placement and routing of ASIC physical design.

11. Describe the process of functional verification.

Department of Electronics & Communication Engg. JVIT, BIDADI Page 5

You might also like

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- Genus Quick Start Timing PDFDocument33 pagesGenus Quick Start Timing PDFShivasharan R Rajapur100% (2)

- Microcontrollers 2017-18 Lab ManualDocument58 pagesMicrocontrollers 2017-18 Lab ManualSUNIL KUMAR100% (1)

- Technological University of the Philippines College of Engineering Electronics Engineering DepartmentDocument13 pagesTechnological University of the Philippines College of Engineering Electronics Engineering DepartmentNicko Wick0% (1)

- COA question bank on computer organization and architectureDocument10 pagesCOA question bank on computer organization and architectureVenkat RamNo ratings yet

- Computer Organzation and Architecture Question BankDocument10 pagesComputer Organzation and Architecture Question Bankmichael100% (2)

- Embedded Lab: Kgisl Institute of Technology Department of Electronics and CommunicationDocument111 pagesEmbedded Lab: Kgisl Institute of Technology Department of Electronics and CommunicationJeeva NatarajanNo ratings yet

- Question Bank - M5 To M7Document2 pagesQuestion Bank - M5 To M7Pieter MarkerNo ratings yet

- Alexander Shuiskov - Microservices With Go-Packt Publising PVT LTD (2022)Document329 pagesAlexander Shuiskov - Microservices With Go-Packt Publising PVT LTD (2022)Nguyễn Thanh DưNo ratings yet

- EC334 Microcontrollers Lab-Manual FinalDocument52 pagesEC334 Microcontrollers Lab-Manual FinalSanjid ElahiNo ratings yet

- Digital Integrated Circuit Tester IeeeDocument5 pagesDigital Integrated Circuit Tester Ieeeashwin_nakman100% (2)

- Sri Venkateshwara College of EngineeringDocument3 pagesSri Venkateshwara College of EngineeringpavanNo ratings yet

- Question BankDocument4 pagesQuestion BankChetan GowdaNo ratings yet

- Digital Design VLSI Systems Question BankDocument4 pagesDigital Design VLSI Systems Question BankRamachandra TurkaniNo ratings yet

- Sample Questions: Chapter One: Digital Building BlocksDocument4 pagesSample Questions: Chapter One: Digital Building BlocksDonnNo ratings yet

- ECE 2003 ManualDocument79 pagesECE 2003 Manualannambaka satishNo ratings yet

- Digital System Design: Provided by Humayra JahanDocument5 pagesDigital System Design: Provided by Humayra JahanZabirNo ratings yet

- Ei2353:Digital System Design: Question BankDocument3 pagesEi2353:Digital System Design: Question BanknithyadeceNo ratings yet

- FPGA Lab 07Document14 pagesFPGA Lab 07Zain AlamgirNo ratings yet

- Question Bank UnitwiseDocument6 pagesQuestion Bank UnitwiseKunal KhandelwalNo ratings yet

- Electronics MPDocument8 pagesElectronics MPk lakshmi prasannaNo ratings yet

- CAO 2021 Assignment QuestionDocument9 pagesCAO 2021 Assignment Questiondawit tadewoseNo ratings yet

- 2629acomputer ArchitectureDocument15 pages2629acomputer ArchitectureSiddhant Jain SethNo ratings yet

- Embedded Systems Lab Manual: Atria Institute of Technology Anandanagar, Bangalore-24Document80 pagesEmbedded Systems Lab Manual: Atria Institute of Technology Anandanagar, Bangalore-24Swetha Rani MunirajuNo ratings yet

- COA_QBDocument6 pagesCOA_QBsourabha prasadNo ratings yet

- 9A04504 Digital IC ApplicationsDocument4 pages9A04504 Digital IC ApplicationssivabharathamurthyNo ratings yet

- DLDM Question BankDocument8 pagesDLDM Question BankMayur PatilNo ratings yet

- Embedded Processor QB by VPDocument4 pagesEmbedded Processor QB by VPVaishnavi BavalekarNo ratings yet

- ET7102-Microcontroller Based System DesignDocument10 pagesET7102-Microcontroller Based System Designanses1000No ratings yet

- Shivalik College of Engineering Question Bank Computer Organization B.Tech II Year (IV Semester)Document5 pagesShivalik College of Engineering Question Bank Computer Organization B.Tech II Year (IV Semester)Paras TilaraNo ratings yet

- 24AA254 Memory I2C With The XC8 C Compiler - AN1488ADocument24 pages24AA254 Memory I2C With The XC8 C Compiler - AN1488Aalexandre.oneill2479No ratings yet

- Sample DSD Lab ManualDocument125 pagesSample DSD Lab ManualRajuNo ratings yet

- Computer Organization and Architecture Model Question PaperDocument3 pagesComputer Organization and Architecture Model Question PaperPrateekMandiNo ratings yet

- MCSD Question Bank on 8051 and PIC Microcontroller Architecture and ProgrammingDocument10 pagesMCSD Question Bank on 8051 and PIC Microcontroller Architecture and ProgrammingJagadeesh100% (1)

- Semester Two Examinations - Summer 2007: Microprocessor Engineering 16-7210Document5 pagesSemester Two Examinations - Summer 2007: Microprocessor Engineering 16-7210amit panvekarNo ratings yet

- EC8711 Embedded Lab Manual FinalDocument258 pagesEC8711 Embedded Lab Manual FinalbloomeceNo ratings yet

- Embedded Sysytem FileDocument52 pagesEmbedded Sysytem FileGagan MaggoNo ratings yet

- 08.402 Digital Electronics and Logic Design (E)Document1 page08.402 Digital Electronics and Logic Design (E)anupvasuNo ratings yet

- 18CSL48 MergedDocument48 pages18CSL48 MergedAbhishek nNo ratings yet

- Embedded Systems 9168 - Sample Paper of MSBTE For Sixth Semester Final Year Computer Engineering Diploma (80 Marks)Document2 pagesEmbedded Systems 9168 - Sample Paper of MSBTE For Sixth Semester Final Year Computer Engineering Diploma (80 Marks)Sanjay DudaniNo ratings yet

- Microprocessor and Architecture Solution PDFDocument23 pagesMicroprocessor and Architecture Solution PDFKarmaveer Bhaurao Patil CollegeNo ratings yet

- 2 Marks Questions and Answers Ec65-Microprocessor and MicroconrollersDocument19 pages2 Marks Questions and Answers Ec65-Microprocessor and MicroconrollerstaksasNo ratings yet

- 2 Marks Questions and Answers Ec65-Microprocessor and MicroconrollersDocument19 pages2 Marks Questions and Answers Ec65-Microprocessor and MicroconrollersAnonymous 3XeTp7drNo ratings yet

- An52478 001-52478Document15 pagesAn52478 001-52478Đặng Văn TàiNo ratings yet

- Techincal Report Writing Short Project Report Section-ADocument7 pagesTechincal Report Writing Short Project Report Section-AMuhammad UmairNo ratings yet

- EE8681 Lab ManualDocument110 pagesEE8681 Lab ManualVasunthara DNo ratings yet

- MC Oral QuestionsDocument2 pagesMC Oral Questionschaitanyajadhav142004No ratings yet

- Digital Electronics Assignment on ROM, Memory Technologies & ADCsDocument2 pagesDigital Electronics Assignment on ROM, Memory Technologies & ADCsDenis MugiNo ratings yet

- Experiment #6 Input / Output DesignDocument11 pagesExperiment #6 Input / Output DesignFelipe DiasNo ratings yet

- K S Institution Microcontroller Lab SyllabusDocument44 pagesK S Institution Microcontroller Lab SyllabusMaxiteNo ratings yet

- Micro ProcessorDocument24 pagesMicro ProcessorPreeti KarkiNo ratings yet

- DEC Lab Experiments - 2017aDocument5 pagesDEC Lab Experiments - 2017aManjeet SinghNo ratings yet

- DCD QB Dec 2023 StudentDocument7 pagesDCD QB Dec 2023 StudentPranav VasudevNo ratings yet

- Ec2203 Digital ElectronicsDocument8 pagesEc2203 Digital ElectronicspappujayaNo ratings yet

- COA IMP QUESTIONS_32543434_2024_03_19_23_14Document6 pagesCOA IMP QUESTIONS_32543434_2024_03_19_23_14cofasi3281No ratings yet

- Cs6201-Digital Principles and System DesignDocument6 pagesCs6201-Digital Principles and System DesignAnonymous L4iu94ZIlwNo ratings yet

- CSC 204 - Final Study GuideDocument12 pagesCSC 204 - Final Study GuideFVCproductionsNo ratings yet

- 555Document1 page555Abhishek nNo ratings yet

- KSCST Student Project Proposal FormatDocument8 pagesKSCST Student Project Proposal FormatAbhishek nNo ratings yet

- DC NotesDocument225 pagesDC NotesAbhishek nNo ratings yet

- 18CSL48 MergedDocument48 pages18CSL48 MergedAbhishek nNo ratings yet

- Frequncey 1 0.5 Square NRZDocument1 pageFrequncey 1 0.5 Square NRZAbhishek nNo ratings yet

- Mwa NotesDocument224 pagesMwa NotesAbhishek nNo ratings yet

- Mar 2022Document2 pagesMar 2022Abhishek nNo ratings yet

- Module 3: Transistor and Fet Frequency ResponseDocument35 pagesModule 3: Transistor and Fet Frequency ResponseAbhishek nNo ratings yet

- Jnanavikas Institute of Technology: Mr. Shubas S.RDocument74 pagesJnanavikas Institute of Technology: Mr. Shubas S.RAbhishek nNo ratings yet

- Ade LabDocument4 pagesAde LabAbhishek nNo ratings yet

- JVIT Communication Lab ManualDocument76 pagesJVIT Communication Lab ManualAbhishek nNo ratings yet

- Simulate NRZ, RZ, Half-Sinusoid and Raised Cosine Pulses and Generate Eye Diagram For Binary Polar SignallingDocument10 pagesSimulate NRZ, RZ, Half-Sinusoid and Raised Cosine Pulses and Generate Eye Diagram For Binary Polar SignallingAbhishek nNo ratings yet

- 3rd Sem Edi Lab Manual (18ecl37) JvitDocument48 pages3rd Sem Edi Lab Manual (18ecl37) JvitAbhishek nNo ratings yet

- Ade LabDocument4 pagesAde LabAbhishek nNo ratings yet

- Edge ComputingDocument5 pagesEdge ComputingAbhishek nNo ratings yet

- New Microsoft Word Document PDFDocument1 pageNew Microsoft Word Document PDFAbhishek nNo ratings yet

- Paperlms (Ref) PDFDocument40 pagesPaperlms (Ref) PDFAbhishek nNo ratings yet

- Unit 8 HIGHWAY DRAINAGE PDFDocument27 pagesUnit 8 HIGHWAY DRAINAGE PDFAbhishek nNo ratings yet

- Civil V Transportation Engineering 1 U2Document11 pagesCivil V Transportation Engineering 1 U2Abhishek nNo ratings yet

- Asynchronous CountersDocument29 pagesAsynchronous CountersSelvasundar KumarNo ratings yet

- Block Diagram of The 8251 USART (Universal Synchronous Asynchronous Receiver Transmitter)Document9 pagesBlock Diagram of The 8251 USART (Universal Synchronous Asynchronous Receiver Transmitter)Radha MuraliNo ratings yet

- 3.2.4.B AsynchronousCounters - Now Serving Display - DMS-1Document6 pages3.2.4.B AsynchronousCounters - Now Serving Display - DMS-1HenryNo ratings yet

- Unit III Counter NotesDocument20 pagesUnit III Counter NotesR ChandrasekharNo ratings yet

- Government Engineering College Digital Logic Design Lab ManualDocument44 pagesGovernment Engineering College Digital Logic Design Lab ManualGECM85No ratings yet

- 09 Fifo SynchronizationDocument4 pages09 Fifo SynchronizationkoorapatisagarNo ratings yet

- 5.4 Moore Mealy ModelsDocument10 pages5.4 Moore Mealy ModelsPika ChuNo ratings yet

- Remove Glitches in Physical DesignDocument120 pagesRemove Glitches in Physical Designసుశీల్ శరత్No ratings yet

- PresentationDocument33 pagesPresentationYoftahiNo ratings yet

- MNL Avalon SpecDocument59 pagesMNL Avalon SpecAlexis Jonathan Bautista BaqueroNo ratings yet

- 6.004 Computation Structures: Mit OpencoursewareDocument8 pages6.004 Computation Structures: Mit OpencoursewareravindarsinghNo ratings yet

- US-NRC Document On QualificationDocument98 pagesUS-NRC Document On QualificationParidhi AggarwalNo ratings yet

- Input/Output Organization in Computer Organisation and ArchitectureDocument99 pagesInput/Output Organization in Computer Organisation and ArchitectureAnand YadavNo ratings yet

- Design of Asynchronous FIFO Using Verilog HDLDocument28 pagesDesign of Asynchronous FIFO Using Verilog HDLMani Bharath Nuti100% (1)

- Asynchronous Counters: Asynchronous 4-Bit UP CounterDocument13 pagesAsynchronous Counters: Asynchronous 4-Bit UP CounterAbhiNo ratings yet

- ACTIVITY PPT Exploring Sequential CircuitsDocument12 pagesACTIVITY PPT Exploring Sequential Circuitsks78874960% (1)

- History of DRAM and TypesDocument11 pagesHistory of DRAM and TypesVani SallyNo ratings yet

- 2302-24-Qalog CDC Fpga MCPDocument17 pages2302-24-Qalog CDC Fpga MCPramsampath78No ratings yet

- Asynchronous Sequential Logic FundamentalsDocument21 pagesAsynchronous Sequential Logic FundamentalsJohn Patrick CeldaNo ratings yet

- Lies, Damned Lies, and Coverage: Mark Litterick EmailDocument12 pagesLies, Damned Lies, and Coverage: Mark Litterick EmailQuý Trương QuangNo ratings yet

- A Comparison Between Synchronous and Asynchronous Counters: 4-Bit Ripple CounterDocument3 pagesA Comparison Between Synchronous and Asynchronous Counters: 4-Bit Ripple CounterAbhishek DasNo ratings yet

- Module 2Document42 pagesModule 2DhananjayaNo ratings yet

- Digital System Design LecturesDocument132 pagesDigital System Design LecturesAnmar Hasan50% (2)

- Microchip RTG4 Radiation Mitigated Clock and Reset Network Usage Application Note AC463 V2Document34 pagesMicrochip RTG4 Radiation Mitigated Clock and Reset Network Usage Application Note AC463 V2FalsoNo ratings yet

- Manual 7VE51Document104 pagesManual 7VE51MAURICIO GOMEZ OSORIONo ratings yet

- Combinational and Sequential CircuitsDocument12 pagesCombinational and Sequential Circuitsdomainname9No ratings yet

- Improved Velocity Estimation For Low-Speed and Transient Regimes Using Low-Resolution EncodersDocument8 pagesImproved Velocity Estimation For Low-Speed and Transient Regimes Using Low-Resolution EncodersLÊ ĐẠI HIỆPNo ratings yet