Professional Documents

Culture Documents

Chapter 7 Typical Troubles and Troubleshooting

Uploaded by

Luigi PortugalOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Chapter 7 Typical Troubles and Troubleshooting

Uploaded by

Luigi PortugalCopyright:

Available Formats

Chapter 7 Typical Troubles and Troubleshooting

1. Troubleshooting 7-2

2. IGBT Test Procedures 7-7

3. Typical Troubles and Troubleshooting 7-8

MT5F43750 © Fuji Electric Co., Ltd. All rights reserved. 7-1

This chapter describes typical troubles and how to deal with them.

1. Troubleshooting

When abnormalities such as device failure occurs, it is necessary to clarify the situation and determine the cause

before taking countermeasures. Referring to Table 7-1, please investigate the failure mode and analyze the

causes of abnormalities by observing the irregularities outside of the device. If the cause cannot be determined

by using Table 7-1, use the detailed diagram shown in Fig.7-1(a-f) to help your investigation.

Table.7-1 Device destruction mode and cause estimation

External abnormalities Cause Device failure mode Check point

SCSOA failure Matching of the operation locus and

Arm short After short circuit detection, when protection is applied (turn-off), the overvoltage exceeds

(overvoltage) device withstand capability during

circuit SCSOA and the device is destroyed

destruction arm short circuit

Overheat (short

toff increased due to insufficient -VGE, dead

Series arm Insufficient dead time circuit withstand Check that toff and dead time match

time setting error

short circuit capability) failure

(upper and dv/dt shoot through and causes short circuit

Short Insufficient -VGE, long gate wiring Check for dv/dt erroneous turn-on

lower arm failure

circuit

short

circuit) Gate drive circuit malfunction, logic circuit

Short circuit failure due to noise etc. Circuit malfunction check

malfunction SCSOA and

overheat failure

Output Check the conditions during failure,

Wiring mistake, abnormal wire contact, load short circuit

short circuit matching of device withstand

Ground capability and protection circuit,

Wiring mistake, abnormal wire contact.

fault ground fault wiring condition

Logic circuit malfunction Logic signal

Overload (overcurrent) Overcurrent flows Overheat

Review of overcurrent protection

Overcurrent protection setting error

setting value

Excessive input voltage

Excessive Overvoltage exceeding the device withstand Review of overvoltage protection

C-E overvoltage

DC voltage voltage is applied to C-E level

Overvoltage protection setting error

Matching of turn-off operation locus

Overvoltage at turn-off exceeds RBSOA RBSOA

and RBSOA, review of snubber circuit

Matching of overvoltage and device

Overvolta

Overvoltage during FWD reverse recovery exceeds device withstand voltage withstand voltage, review of snubber

ge

Excessive circuit

overvoltage

Gate signal interruption, etc., that result in very short Logic or gate drive circuit

C-E overvoltage Logic and gate signals

off pulse, causes turn-off → turn-on in very short time malfunction due to noise

intervals (on the order of several hundred ns) and

Gate signal during high current

generate excessive reverse recovery overvoltage that

Electromagnetic induction from the operation / twisted wire of gate signal

exceeds the device withstand voltage (hereinafter,

main circuit to the gate signal line line / distance from main circuit to

short off pulse reverse recovery phenomenon)

gate signal line

DC-DC converter malfunction

Drive supply voltage VGE drops below the design value, VCE increases, heat

Drive supply voltage rise is too slow Overheat Check circuit

drop generation (loss) increases, causing destruction

Gate signal wiring disconnected

Check working status (static

Static electricity is applied to G-E

electricity countermeasures)

Gate overvoltage G-E overvoltage

The gate wiring is too long, resulting in overvoltage exceeding G-E withstand voltage Check gate voltage

Destruction by applying C-E voltage (on voltage / withstand voltage measurement, etc.) while Overheat

Driving with open gate Check gate voltage

the gate is open destruction

Insufficient Loose terminal mounting screws

heat Check heat dissipation condition

dissipation Insufficient heat dissipation capacity causes the Insufficient application of thermal grease

Overheat Overheat

capacity device to overheat beyond Tvj max.

Thermal Cooling fan malfunction Check logic circuit

runaway

Stress applied to terminals from external

Stress

wiring Electrical wiring Stress generated at terminals /

The terminal soldering part inside the product is

Stress disconnection inside mounting state of product and other

disconnected due to stress fatigue Vibration of other mounting parts applied

Vibration the product (open) parts

stress to the terminals

The application conditions (environment, temperature change, assembly conditions at the Failure mode is

Reliability time of mounting, storage condition, etc.) of the device and the reliability of the product does different for each Check based on Fig.7-1

not match, causing failure of wiring inside the product, insulation structure, appearance, etc. case

MT5F43750 © Fuji Electric Co., Ltd. All rights reserved. 7-2

Destruction of discrete IGBT Destruction of IGBT RBSOA deviation A

Gate overvoltage B

Junction overheating C

Destruction of FWD D

Reliability E

Dielectric breakdown F

Fig.7-1 IGBT failure analysis diagram (A-E symbols are connected to the following figures)

A RBSOA deviation

[ Origin of failure]

Overcurrent protection

Excessive current Excessive turn-off current Abnormal control PCB

circuit malfunction

Gate drive circuit

Series arm short circuit Abnormal control PCB

malfunction

Gate drive circuit error

Insufficient dead

Abnormal control PCB

time

Output short circuit Abnormal load

Ground fault Abnormal load

Excessive power supply

Overvoltage Abnormal input voltage

voltage

Abnormal regenerative

Motor regenerative operation circuit

Overvoltage protection Abnormal control PCB

circuit malfunction

Snubber resistance

Insufficient discharge of

Abnormal snubber circuit disconnection

snubber

Abnormal gate drive

Turn-off operation during

circuit

short circuit

Abnormal control PCB

Excessive overvoltage during

D

reverse recovery (FWD)

Fig.7-1(a) Mode A: RBSOA deviation

B Gate overvoltage

[ Origin of failure ]

No measures against static

Static electricity Manufactural failure

electricity

Overvoltage Oscillation Long gate wiring

Long gate wiring

L・di/dt voltage

Fig.7-1(b) Mode B: Gate overvoltage

MT5F43750 © Fuji Electric Co., Ltd. All rights reserved. 7-3

Junction

C [Origin of failure]

overheating

Abnormal gate

On-state loss

VCE (sat) increase Insufficient +VGE drive circuit

increase

Abnormal control

power circuit

Overcurrent

Over Abnormal control

IC increase protection circuit

current PCB

malfunction

Gate drive Abnormal control

Series arm short

circuit PCB

circuit

malfunction Abnormal gate

drive circuit

Insufficient dead Abnormal control

time PCB

Output short circuirt Abnormal load

Ground fault Abnormal load

Abnormal control

Overload PCB

Abnormal load

Switching loss Number of switching Abnormal control

Carrier frequency increase

increase increase PCB

Abnormal snubber

circuit

di/dt malfunction

Abnormal gate

drive circuit

Gate drive circuit Abnormal control

malfunction PCB

Abnormal gate

drive circuit

Turn-on time Abnormal gate

Eon increase +VGE decrease

increase drive circuit

Abnormal gate

RG value increase

drive circuit

Excessive turn-on Excessive snubber Snubber circuit

current discharge current error

Series arm Insufficient Abnormal control

short circuit dead time PCB

Turn-off time Abnormal gate

Eoff increase -VGE decrease

increase drive circuit

RG value Abnormal gate

increase drive circuit

Series arm short Insufficient dead Abnormal control

circuit time PCB

Abnormal gate

drive circuit

Contact thermal resistance Insufficient

Insufficient tightening force during mounting

increase tightening torque

Excessive heat sink Heat sink warpage

warpage failure

Insufficient

adjustment of

Insufficient volume of thermal grease

thermal grease

volume

Insufficient

Decreased cooling

Case temperature rise Heat sink clogging dustproof

capacity

measures

Cooling fan speed decrease or Abnormal cooling

stop fan

Abnormal rise in ambient Partial overheating of Abnormal cooling

temperature the stack system

Abnormal

Temperature protection device

temperature

malfunction

protection device

Fig.7-1(c) Mode C: Junction overheating

MT5F43750 © Fuji Electric Co., Ltd. All rights reserved. 7-4

Destruction of

D

FWD

[ Origin of failure ]

Excessive

junction On-state loss increase Overload Power factor decrease

temperature rise

Abnormal load

Abnormal control PCB

Number of Abnormal snubber

Switching loss increase dv / dt malfunction

switching increase circuit

Abnormal gate drive

circuit

Gate drive signal

Abnormal control PCB

malfunction

Abnormal gate drive

circuit

Carrier frequency increase Abnormal control PCB

Contact thermal

Insufficient tightening

resistance Insufficient tightening force during mounting

torque

increase

Excessive heat sink warpage Heat sink warp failure

Insufficient adjustment

Insufficient volume of thermal grease of thermal grease

volume

Case temperature Decreased cooling Insufficient dustproof

Heat sink clogging

rise capacity measures

Cooling fan speed

Abnormal cooling fan

decrease or stop

Abnormal rise in Partial overheating Abnormal cooling

ambient temperature of the stack system

Abnormal temperature

Temperature protection device malfunction

protection device

Excessive overvoltage Abnormal snubber

Overvoltage

during reverse recovery circuit

di/dt increase at Abnormal gate drive

+VGE increase

turn-on circuit

RG value Abnormal gate drive

decrease circuit

Gate signal

Short off pulse reverse interruption Abnormal gate drive

recovery phenomenon due to noise, circuit

etc.

Abnormal control PCB

Excessive overvoltage during

A

IGBT turn-off

Fig.7-1(d) Mode D: Destruction of FWD

MT5F43750 © Fuji Electric Co., Ltd. All rights reserved. 7-5

E Reliabillity

[ Origin of failure ]

Destruction caused by

External force, load Loading during product storage Loading conditions

handling

Stress applied on terminals

Terminal stress

during mounting

Insufficient screw

Excessive contact resistance Terminal part

tightening torque

Excessive vibration during

Vibration transportation (products, Transport condition

equipment)

Product terminal

Loose fixing during product

(check stress due to

mounting

vibration)

Dropping, collisions, etc. during

Shock Transport condition

transportation

Assembly conditions

Heat resistance of Excessive overheat when

during product

soldered terminals soldering terminals

mounting

Storage in abnormal Storage in corrosive gas

Storage conditions

condition atmosphere

Storage in environment prone to

condensation

Storage in dusty environment

Poor uniformity of the main circuit,

Destruction in parallel Main circuit wiring

causing transient current

connection uniformity

concentration and current oscillation

Long-term storage at high temperature (High temperature

Reliability (lifetime) Storage conditions

storage)

Long-term storage in low temperature (Low temperature storage)

※For the results of the Long-term storage in hot and humid conditions (Temperature

reliability test humidity storage)

conducted by Fuji

Electric, please refer to

the specifications or Thermal stress fatigue caused by repeated gradual rise and fall of Matching between

the reliability test result product temperature (Temperature cycle, ΔTC power cycle) working conditions

report. and product lifetime

Thermal stress failure caused by a sudden rise or fall of product

temperature (Thermal shock)

Thermal stress failure of internal wiring of products caused by

changes in semiconductor chip temperature due to sudden

changes in load, etc. (ΔTvj power cycle)

Long-term voltage application in high

Long-term use at

temperature (High temperature bias

high temperature

for C-E and G-E)

Long-term voltage application in hot Long-term use in

and humid conditions (Temperature hot and humid

humidity bias (THB)) conditions

Fig.7-1(e) Mode E: Reliability

F Dielectric breakdown

[ Origin of failure ]

Improper insulation

Insulation sheet

sheet installation

Fig.7-1(f) Mode F: Dielectric breakdown

MT5F43750 © Fuji Electric Co., Ltd. All rights reserved. 7-6

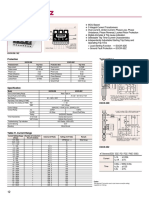

2. IGBT Test Procedures

The following items can be determined by using a transistor curve tracer (hereinafter as CT) to check

the faulty IGBT.

① G-E leakage current ② C-E leakage current (G-E must be shorted)

Other test equipment, such as a Volt-ohm multi-meter that is capable of measuring voltage/resistance

and so forth to determine failures, can be used to help diagnose the fault.

<G-E check>

As shown in Fig.7-2, measure the G-E leakage current or resistance, with C-E shorted. If the

product is normal, the leakage current should be several hundreds nA and the resistance should be

several tens of MΩ to infinity. If the leakage current is more than a few nA or the resistance value is

less than a few MΩ, the device may be defective.

Do not apply G-E voltage in excess of 20V. When using a Volt-ohm multi-meter, make sure the

internal battery voltage is below 20V.

C

Short C-E

G

CT or V-ohm

E multi-meter

Measure G-E leakage

E current or resistance

Fig.7-2 G-E check

<C-E check>

As shown in Fig.7-3, measure the C-E leakage current or resistance, with G-E shorted. If the IGBT

is normal, the leakage current should be below ICES max. specified in the datasheet. Please note the

following items.

① Be sure to connect C to (+) and E to (-). Reverse connections will conduct the FWD thus making

measurement impossible.

② Do not apply voltage higher than the rated value. Applying voltage higher than the rated value

may destroy the device.

CT or V-ohm + G

multi-meter

- Short G-E

Measure C-E leakage E

current or resistance

E

Fig.7-3 C-E check

MT5F43750 © Fuji Electric Co., Ltd. All rights reserved. 7-7

3. Typical Troubles and Troubleshooting

<How to avoid dv/dt shoot through during FWD reverse recovery>

This section describes how to avoid dv/dt shoot through of the IGBT during FWD reverse recovery.

Fig.7-4 shows the causes of dv/dt shoot through. In this fig., IGBT2 is reverse biased. If IGBT1

changes from off to on, FWD2 on the opposite arm goes in to reverse recover mode. At the same

time, the voltage potentials of IGBT2 and FWD2 in the off-state rise, and dv/dt is generated according

to the switching time of IGBT1. Since IGBT1 and IGBT2 have Cres, current I = Cres · dv/dt is generated

through Cres. This current flow through RG, resulting in rise of VGE. If this VGE exceeds the sum of the

reverse bias voltage of IGBT2 and the threshold voltage VGE (th), IGBT2 will be turned-on, resulting in

short circuit of IGBT1 and IGBT2.

IGBT1 FWD1

RG

c

070-3765-4209

I =Cres・dv/dt

FWD2

- RG

IGBT2

+ Off state

Fig.7-4 Principle of dv/dt shoot through

MT5F43750 © Fuji Electric Co., Ltd. All rights reserved. 7-8

Fig.7-5 shows the method to avoid the shoot through.

CGE High-RG

-VGE

(a) Additional CGE (b) Increase of -VGE (c) Increase of RG

Fig.7-5 How to avoid dv/dt shoot through

There are three methods, which are CGE addition, increase of -VGE and increase of RG. Check the

effects of these measures as they differ depending on the gate drive circuit. Also, check the effect of

these measures on switching loss.

The method to add CGE is the way to decrease the current flowing through RG by passing through

CGE. However, in order to charge/discharge the additional CGE, switching speed becomes slower.

Thus, just adding CGE results in increase switching loss. However, by reducing RG and adding CGE, it

is possible to avoid the shoot through without increasing switching loss.

Recommended CGE is about two times the value of Cies described in the specification sheet, and

recommended RG is about half the value before adding CGE.

MT5F43750 © Fuji Electric Co., Ltd. All rights reserved. 7-9

<Energizing main circuit voltage when G-E is open>

When checking the characteristics of a single device, if voltage is applied to C-E when G-E is open,

current (i) will flow through Cres of the IGBT as shown in Fig.7-6. As a result, G-E capacitance is

charged and the gate potential rises, causing the IGBT to turn-on. Thus, IC flows and heat is generated,

which may cause destruction. When driving the IGBT, be sure to drive it with a G-E signal. Also, be sure

to discharge the main circuit voltage (C-E) to 0V before switching the gate signal.

Fig.7-7 shows an example of on-voltage measurement circuit. The measurement sequence is described

with reference to this measurement circuit. First, turn-off the gate drive unit (GDU) (VGE = 0V). Then

turn-on SW1 to apply C-E voltage. Next, apply predefined forward bias voltage from the GDU to

energize the IGBT, and measures the on-voltage. Lastly, turn-off the gate circuit and turn-off SW 1. This

sequencing will allow for the safe measurement of device characteristics without risking destruction.

C(Collector)

i

IC

G(Gate)

RGE

E(Emitter)

Fig.7-6 IGBT behavior when G-E is open

SW 1 R1 D1

DUT

CRO

+

G -

D2 R2 +

-

GDU R3

DUT:IGBT under test, GDU:Gate drive circuit, G:Variable AC power supply

CRO:Oscilloscope, R1, R2:Protective resistance,

R3:Current measurement non-inductive resistance, D1,D2:Diode, SW 1:Switch

Fig.7-7 On-voltage measurement circuit

MT5F43750 © Fuji Electric Co., Ltd. All rights reserved. 7-10

<Diode reverse recovery from transient on-state (short off pulse reverse recovery)>

If very short off pulses are generated when gate signal interruption happens due to noise while driving

the IGBT, excessive reverse recovery overvoltage will occur. This phenomenon is called the short off

pulse reverse recovery. Fig.7-8 shows the timing chart of this phenomenon.

In Fig.7-9, when an off signal Tw is generated at VGE during period Ton in which IGBT2 is on, IGBT2 is

turned off while FWD1 on the opposite arm side is turned on, and IGBT2 is immediately turned on again

while FWD1 goes into reverse recovery. Normally, reverse recovery started after sufficient carriers are

accumulated in the FWD. On the other hand, in the short off pulse reverse recovery, FWD goes into

reverse recovery without sufficient carrier accumulation. As a result, the depletion layer spreads rapidly in

the FWD, causing steep di/dt and dv/dt, and very large C-E (A-K) overvoltage as shown in the dotted line

in Fig.7-8. If the overvoltage exceeds the device voltage rating, the device may be destroyed. When

designing the equipment, be careful not to design a circuit that will generate such short gate signal off

pulse.

TON TW

IGBT1 VAK

0 FWD1

VGE RG

c

070-3765-4209 c

070-3765-4209

RG FWD2

VAK IGBT2

VGE

0

Fig.7-8 Waveforms during short off pulse reverse recovery Fig.7-9 Circuit diagram

MT5F43750 © Fuji Electric Co., Ltd. All rights reserved. 7-11

<Precautions in parallel connection>

When using IGBT to control large current, IGBTs may be connected in parallel. If the current is not

balanced among the IGBTs, current may concentrate on one device and destroy it. The electrical

characteristics of the IGBT as well as the wiring design, affect the current balance between parallel

connected IGBT. In order to maintain current balance it is necessary to match the VCE(sat) values of all

devices. When connecting in parallel, we recommend to use products from the same product lot.

When the main circuit wiring is uneven, uneven voltage is generated in the inductance of each wiring

due to di/dt during switching, and oscillating current flows through the control side wiring loop of the

emitter connected in parallel, causing the gate voltage to oscillate. This oscillation may cause the IGBT

to malfunction.

Balanced current sharing can be achieved by using symmetrical wiring to prevent the above-

mentioned IGBT malfunction (see Fig. 7-10).

LC 1 LC 2

RC1 RC2

GDU

+

VCC

- LL 1 RL1 RL2 LL 2

GDU

LE 1 RE1 LE 2

RE2

Wiring so that RC1=RC2, RL1=RL2, RE1=RE2,LC1=LC2, LL1=LL2,LE1=LE2

Fig.7-10 Equivalent circuit of parallel connection

MT5F43750 © Fuji Electric Co., Ltd. All rights reserved. 7-12

Fig.7-11(1) shows the oscillation phenomenon when the wiring inductance of the emitter is made

extremely unbalanced.

iG1 iG1

iG2 iG2

iC11 iC11

iC21 iC21

(1) When emitter inductance is unbalanced (2) When common mode coil is inserted

in gate emitter wiring

Fig.7-11 Waveforms of 2 parallel connection

A common mode coil can be inserted in each gate emitter wiring to eliminate the loop current in the

emitter. Fig.7-11 (2) shows the waveforms with the common mode coil. Compared with Fig.7-11(1),

oscillation is suppressed.

Common mode coil

GDU

+

VCC

-

Common mode coil

GDU

Fig.7-12 Parallel circuit with common mode coil inserted

MT5F43750 © Fuji Electric Co., Ltd. All rights reserved. 7-13

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- How To Test Distance Relay 7SA522 - EditedDocument55 pagesHow To Test Distance Relay 7SA522 - Editedvernight100% (2)

- Fundamentals of Substation Protection Relay DevicesDocument113 pagesFundamentals of Substation Protection Relay Devicesmaynard pacala100% (1)

- 07-BKH-coordination & Fault EliminationDocument56 pages07-BKH-coordination & Fault Eliminationshawon_darkNo ratings yet

- Offshore Electrical Engineering ManualFrom EverandOffshore Electrical Engineering ManualRating: 4 out of 5 stars4/5 (9)

- Instrument Transformer Testing Brochure ENUDocument36 pagesInstrument Transformer Testing Brochure ENUJayakumar JNo ratings yet

- Transformer ProtectionDocument6 pagesTransformer Protectionapi-3743746100% (2)

- Extremely Low Frequency Radio Receiver Circuit Project With VU MeterDocument3 pagesExtremely Low Frequency Radio Receiver Circuit Project With VU MeterpecceriniNo ratings yet

- Wireless Communications Design Handbook: Interference into Circuits: Aspects of Noise, Interference, and Environmental ConcernsFrom EverandWireless Communications Design Handbook: Interference into Circuits: Aspects of Noise, Interference, and Environmental ConcernsNo ratings yet

- How To Test Distance Relay 7SA522 PDFDocument55 pagesHow To Test Distance Relay 7SA522 PDFBalaji100% (1)

- Instrument Transformer TestingDocument36 pagesInstrument Transformer TestingChowdhury, A Hasib100% (2)

- Fundamentals of Electrical Engg. Lab ManualDocument54 pagesFundamentals of Electrical Engg. Lab Manualtanay jaiswal100% (2)

- Understanding and Servicing Alarm SystemsFrom EverandUnderstanding and Servicing Alarm SystemsRating: 1 out of 5 stars1/5 (1)

- 5 MCE Test Data PDFDocument60 pages5 MCE Test Data PDFLuis GonzalezNo ratings yet

- Basics of Surge Arresters for Power TransmissionDocument32 pagesBasics of Surge Arresters for Power Transmissionedwinoria100% (1)

- SolaX Power Troubleshooting X1MINI&AIR&BOOST PDFDocument10 pagesSolaX Power Troubleshooting X1MINI&AIR&BOOST PDFmarketingsunfix sunfix100% (1)

- IEEE Generator ProtectionDocument40 pagesIEEE Generator ProtectionAndi Uga SismiletostyleNo ratings yet

- (D. A. Bradley, D. Dawson, N. C. Burd, A. J. Loade (B-Ok - CC) PDFDocument518 pages(D. A. Bradley, D. Dawson, N. C. Burd, A. J. Loade (B-Ok - CC) PDFchinnapparaj.sNo ratings yet

- Power Transformer Diagnostics - Introduction: Rafik FouadDocument45 pagesPower Transformer Diagnostics - Introduction: Rafik FouadiraqnewNo ratings yet

- Trouble Shooting: Quality Is Our MessageDocument9 pagesTrouble Shooting: Quality Is Our MessageMaya MenanNo ratings yet

- Fuji IGBT Protection PDFDocument17 pagesFuji IGBT Protection PDFsamacda1000No ratings yet

- Inovance Err Trouble Shooting GuideDocument23 pagesInovance Err Trouble Shooting GuideSohag Walle UllahNo ratings yet

- Rules, Risks, and Blackouts: Transmission Security OverviewDocument94 pagesRules, Risks, and Blackouts: Transmission Security OverviewAmbachew A.No ratings yet

- REH984e 05Document16 pagesREH984e 05Jaya AdnyanaNo ratings yet

- SurgeProtectionDevices-PPT-R50486-0523Document26 pagesSurgeProtectionDevices-PPT-R50486-0523Francisco PereiraNo ratings yet

- Synchrophasors in Southern Region Operational ExperienceDocument73 pagesSynchrophasors in Southern Region Operational Experiencesherub wangdiNo ratings yet

- Eocr-Pfz: Digital Over Current RelayDocument1 pageEocr-Pfz: Digital Over Current RelayFaris RasyadiNo ratings yet

- Protection5 MCDocument91 pagesProtection5 MCUdara DassanayakeNo ratings yet

- Cable Fault LocationDocument29 pagesCable Fault Locationmahmoud MotamediNo ratings yet

- 高压交流自动重合器0424Document5 pages高压交流自动重合器0424leslicehuangNo ratings yet

- 16 - Apéndice B2Document19 pages16 - Apéndice B2Jose Rafael CastroNo ratings yet

- Overview of Low Voltage Test Methods - EN - V01Document1 pageOverview of Low Voltage Test Methods - EN - V01Poya ShefayeNo ratings yet

- Vacon NXS: "All in One" ApplikationsmanualDocument8 pagesVacon NXS: "All in One" ApplikationsmanualMesafint kassieNo ratings yet

- Eocr 3de 3ez 2 PDFDocument1 pageEocr 3de 3ez 2 PDFDeviNo ratings yet

- MCU Based 3-Phase Protection with Current Monitoring and Fault IndicationDocument1 pageMCU Based 3-Phase Protection with Current Monitoring and Fault IndicationKALYANNo ratings yet

- Monitoring TechniquesDocument4 pagesMonitoring TechniquesJabir SamadiNo ratings yet

- 53rd Annual Conference Protective Relay Engineers Presentation Improved Transformer Inrush AlgorithmDocument27 pages53rd Annual Conference Protective Relay Engineers Presentation Improved Transformer Inrush Algorithmcadel1030No ratings yet

- 2instruction Manuals SG25-1150Document11 pages2instruction Manuals SG25-1150Claudio VazquezNo ratings yet

- Voltage Sags An Explanation Causes, Effects and Correction: White PaperDocument8 pagesVoltage Sags An Explanation Causes, Effects and Correction: White PaperAzeemuddinNo ratings yet

- Power System Protection Lecture 1 AnnotatedDocument8 pagesPower System Protection Lecture 1 AnnotatedJABERNo ratings yet

- MK3000L BrochureDocument2 pagesMK3000L BrochureXuân QuỳnhNo ratings yet

- Department of Electrical Power Engineering: Pyay Technological UniversityDocument22 pagesDepartment of Electrical Power Engineering: Pyay Technological UniversityJeong Do-jeonNo ratings yet

- Hawaiian Electrics Protection Roadmap Steven SanoDocument18 pagesHawaiian Electrics Protection Roadmap Steven Sanomaran sNo ratings yet

- Electric Reliability Troubleshooting Guide SolutionsDocument2 pagesElectric Reliability Troubleshooting Guide SolutionsLeonardo A. Prieto M.No ratings yet

- 6100 SeriesDocument2 pages6100 SeriessantiagoyepezNo ratings yet

- 6100 SeriesDocument2 pages6100 SeriessantiagoyepezNo ratings yet

- 6100 Series FG WilsonDocument2 pages6100 Series FG WilsonsantiagoyepezNo ratings yet

- The Importance of The NGRDocument58 pagesThe Importance of The NGRmelekimNo ratings yet

- 3RB22Document2 pages3RB22veemandalNo ratings yet

- An Improved Transformer Inrush Restraint AlgorithmDocument29 pagesAn Improved Transformer Inrush Restraint AlgorithmNguyen Xuan TungNo ratings yet

- P3G32 Data Sheet-6DI 9DODocument4 pagesP3G32 Data Sheet-6DI 9DOkeglobalNo ratings yet

- Tesys T - LTMR100EFMDocument4 pagesTesys T - LTMR100EFMFelipe Franco de PaulaNo ratings yet

- Oi For Earth Leakage RelayDocument2 pagesOi For Earth Leakage RelaySweety RoyNo ratings yet

- WR - TS3031 - E01 - 1 ZXSDR Node B Troubleshooting 25PDocument25 pagesWR - TS3031 - E01 - 1 ZXSDR Node B Troubleshooting 25PfatehmeNo ratings yet

- SolaX Power Troubleshooting X1-AC PDFDocument12 pagesSolaX Power Troubleshooting X1-AC PDFmarketingsunfix sunfixNo ratings yet

- Tesys T - LTMR100EFMDocument4 pagesTesys T - LTMR100EFMAntonioGuarderasNo ratings yet

- INVT GD35 FaultDocument10 pagesINVT GD35 Faultphth411No ratings yet

- Relay Setting in Real Power SystemDocument7 pagesRelay Setting in Real Power SystemtrusselNo ratings yet

- TeSys T Motor Management System - LTMR27MFMDocument4 pagesTeSys T Motor Management System - LTMR27MFMAnonymous dso6R0No ratings yet

- Electromagnetic Compatibility by Felicito S Caluyo PDFDocument40 pagesElectromagnetic Compatibility by Felicito S Caluyo PDFmjpadz100% (2)

- T1 25 KVA transformer load data analysisDocument4 pagesT1 25 KVA transformer load data analysisLuigi PortugalNo ratings yet

- Compact Photocouplers with Single, Dual, and Quad ChannelsDocument3 pagesCompact Photocouplers with Single, Dual, and Quad ChannelsLuigi PortugalNo ratings yet

- NTE454 MOSFET Datasheet - TV UHF/RF Amp, Gate ProtectedDocument4 pagesNTE454 MOSFET Datasheet - TV UHF/RF Amp, Gate Protecteddevon39No ratings yet

- 10 D Artikel Automatic Water Tank Filling SystemDocument6 pages10 D Artikel Automatic Water Tank Filling SystemAbhijeetNo ratings yet

- T1 25 KVA transformer load data analysisDocument4 pagesT1 25 KVA transformer load data analysisLuigi PortugalNo ratings yet

- Application of Earth Tube Heat Exchanger and Solar Chimney For Natural Cooling System in Basrah CityDocument10 pagesApplication of Earth Tube Heat Exchanger and Solar Chimney For Natural Cooling System in Basrah CityaishaNo ratings yet

- AC-250 Diaphragm MeterDocument2 pagesAC-250 Diaphragm MeterLuigi PortugalNo ratings yet

- Amco CR4000 PDFDocument4 pagesAmco CR4000 PDFDANIEL CASTAÑEDANo ratings yet

- Plantilla para La Preparación de Atículos Con Normas IEEE (December 2016)Document9 pagesPlantilla para La Preparación de Atículos Con Normas IEEE (December 2016)Alex LozadoNo ratings yet

- CamScanner Scans PDFs from PhotosDocument3 pagesCamScanner Scans PDFs from PhotosLuigi PortugalNo ratings yet

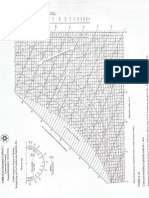

- Carta AshraeDocument1 pageCarta Ashraeseccion3dNo ratings yet

- PlantaDocument2 pagesPlantaLuigi PortugalNo ratings yet

- Formula ResorteDocument2 pagesFormula ResorteLuigi PortugalNo ratings yet

- Tarea#1 de Mecanica de MaterialesDocument7 pagesTarea#1 de Mecanica de MaterialesLuigi PortugalNo ratings yet

- CamScanner Scans PDFs from PhotosDocument3 pagesCamScanner Scans PDFs from PhotosLuigi PortugalNo ratings yet

- Pipe BranchDocument7 pagesPipe BranchDimitra MeidinaNo ratings yet

- Solarni Kontroler LS1024 Manual PDFDocument28 pagesSolarni Kontroler LS1024 Manual PDFMango PapajaNo ratings yet

- Written Report Transducers PDFDocument11 pagesWritten Report Transducers PDFJudy Ann Bernalte VargasNo ratings yet

- GBD PlusDocument2 pagesGBD PlusseinnationalNo ratings yet

- ML11229A702Document86 pagesML11229A702დიმიტრი კოლოტაურიNo ratings yet

- Au/Sn Solder Alloy and Its Applications in Electronics PackagingDocument7 pagesAu/Sn Solder Alloy and Its Applications in Electronics PackagingTeguh Yassi Akasyah PutraNo ratings yet

- LCD - Backlight - Inverter - IC SOLUTIONS PDFDocument44 pagesLCD - Backlight - Inverter - IC SOLUTIONS PDFVictor Avendaño GrilloNo ratings yet

- Measurement & Intrumentation: Made By: Engr. Danish Arif SiddiqiDocument52 pagesMeasurement & Intrumentation: Made By: Engr. Danish Arif SiddiqiMuhammad Usama Sharaf SAAFINo ratings yet

- Ferroelectric RamDocument20 pagesFerroelectric RamRijy LoranceNo ratings yet

- C3611-Panasonic Semiconductor PDFDocument4 pagesC3611-Panasonic Semiconductor PDFNemo VeřitelNo ratings yet

- Beng (Hons) Electrical and Electronic Engineering - E430: Modules CreditsDocument9 pagesBeng (Hons) Electrical and Electronic Engineering - E430: Modules CreditsSalinee BookauramNo ratings yet

- PCB Chassis Mount AC SSRDocument2 pagesPCB Chassis Mount AC SSRjbhupiNo ratings yet

- Absensi Peserta Seminar (Jawaban)Document24 pagesAbsensi Peserta Seminar (Jawaban)Sopika AsmuniNo ratings yet

- Bidirectional Visitor CounterDocument28 pagesBidirectional Visitor CounterRahul Verma100% (1)

- BAV16W/1N4148W Features Mechanical Data: Surface Mount Fast Switching DiodeDocument5 pagesBAV16W/1N4148W Features Mechanical Data: Surface Mount Fast Switching DiodeshareatorNo ratings yet

- Transformer Coupled AmplifierDocument6 pagesTransformer Coupled AmplifierXyrex CalangNo ratings yet

- ARC LS22 Schematic and PartsDocument7 pagesARC LS22 Schematic and PartsarfoceNo ratings yet

- Activated script manipulates page elementsDocument2 pagesActivated script manipulates page elementsSamir IslamNo ratings yet

- P72x - EN T - C21 - V11DDocument334 pagesP72x - EN T - C21 - V11DTlili MahmoudiNo ratings yet

- Modern HVDC: State of The Art and Development Trends: Víctor F. LescaleDocument5 pagesModern HVDC: State of The Art and Development Trends: Víctor F. Lescalenithin krishnaNo ratings yet

- Transmitters and ReceiversDocument20 pagesTransmitters and ReceiversRudra Kumar MishraNo ratings yet

- A New Physical Design Flow For A Selective State Retention Based ApproachDocument15 pagesA New Physical Design Flow For A Selective State Retention Based ApproachJoseph HuangNo ratings yet

- Gunn Diode BasicsDocument5 pagesGunn Diode BasicsshaheerdurraniNo ratings yet

- Design of Electrical Power SystemsDocument36 pagesDesign of Electrical Power SystemsAhmed AwadenNo ratings yet

- L060 Push Pull (2UP)Document10 pagesL060 Push Pull (2UP)srikanthkmsNo ratings yet

- AFE eDocument110 pagesAFE eDươngNo ratings yet